前一段时刻一向在研讨通讯体系,必定就会和各种滤波器打交道,相同也遇到了一些问题。比如说本文的首要内容,滤波器的延时问题。

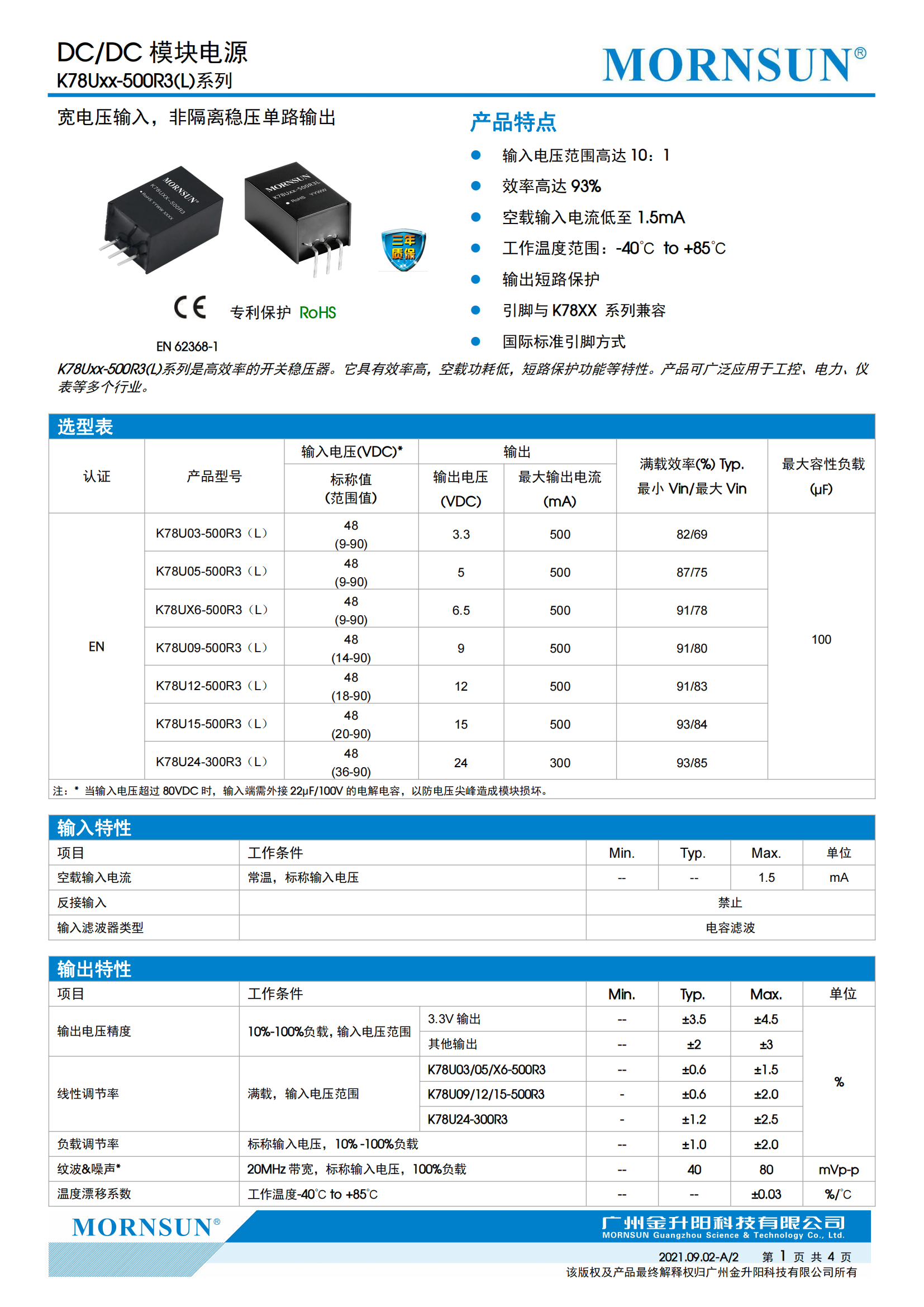

在生成滤波器IP核之前需求发生抽头系数,这个抽头系数的阶数是自己设定的,阶数越高代表滤波器乘累加运算越多,可是阶数巨细的挑选要看是否满意自己的规划要求(例如衰减db是否满意要求)。一起,生成的滤波器抽头系数的值是与自己规划滤波器的各种参数确认的,如数据采样速率,通带截止频率、阻带开端频率(低通)、滤波器类型等。

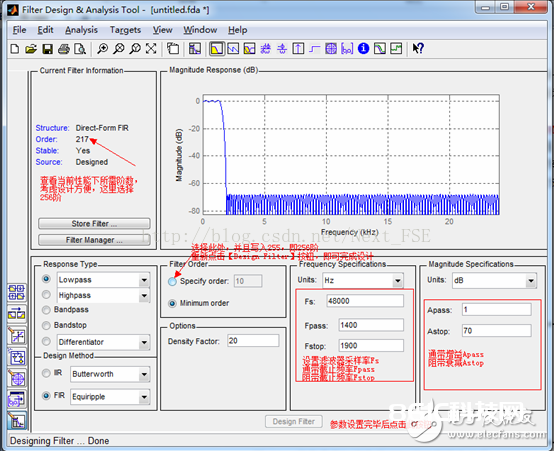

这些抽头系数能够用MATLAB生成,MATLAB中有一个FDATool的东西,以图形化的办法供运用者发生所需的滤波器,然后将系数导出(以coe格局),这样咱们在ISE中新建FIR IP核之后就能够直接导入刚刚发生的抽头系数表,十分便利。

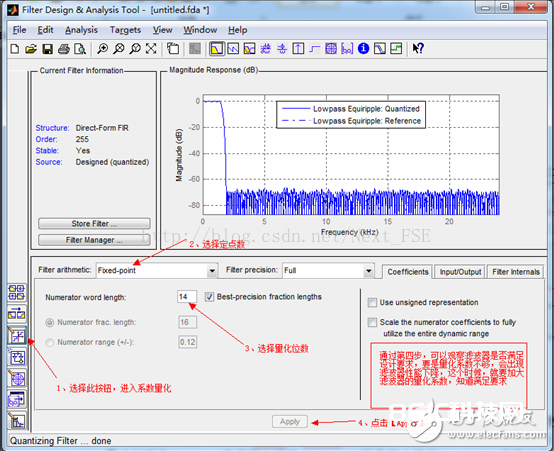

下面直接开端用MATLAB生成抽头系数表:

1、运用 matlab 的 FDATool,发生需求的滤波器系数,翻开【FDATool】

2、滤波器参数设置

留意:

Order数=滤波器阶数-1

尽量规划偶数阶滤波器,偶数阶滤波器乘法器运用率高。

3、滤波器系数量化

一般量化位数在12-16之间,量化位数越低乘法器耗费的资源越少,需求规划者权衡资源与精度。关于FIR Compiler,他运用的是DSP48 slices,经测验14位输入时16位量化位数与16位量化位数耗费相同资源,应挑选16位系数。(至于为什么耗费相同的资源,是因为FPGA内部的DSP48E1硬核乘法器是25*18的,所以无论是16位仍是14位都会占用一个DSP)。

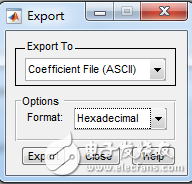

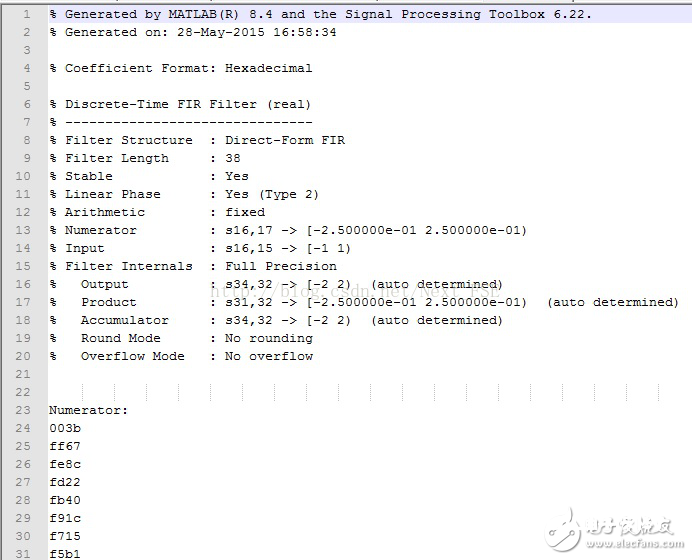

4、导出量化系数点击【file -> export】

点击【Export】,即可把数据导入fcf文件,保存后用UltraEdit翻开即可。

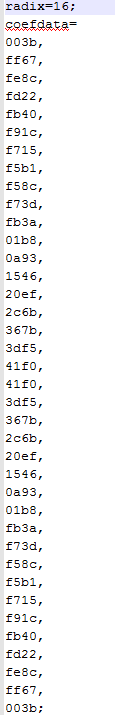

5、假如运用IP core则将16进制数复制生成coe文件;

假如运用乘法/加法器则直接将数据在代码中生成parameter。

留意:因为FIR的对称性,parameter的数量为(阶数+1)/2。

FIR Compiler生成:

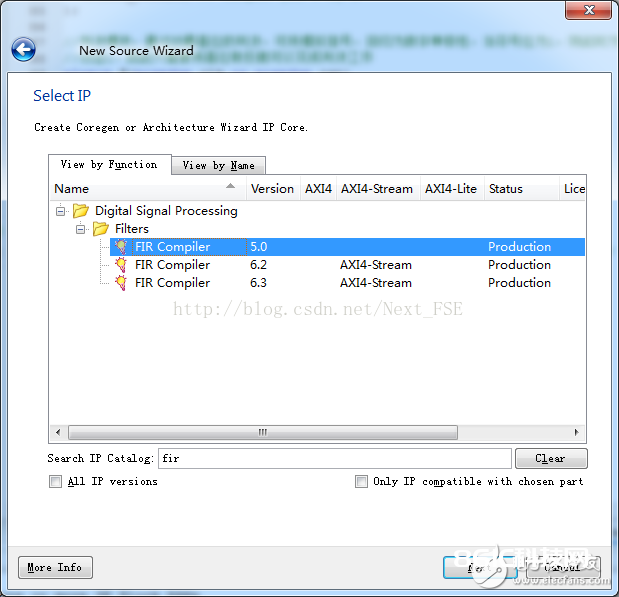

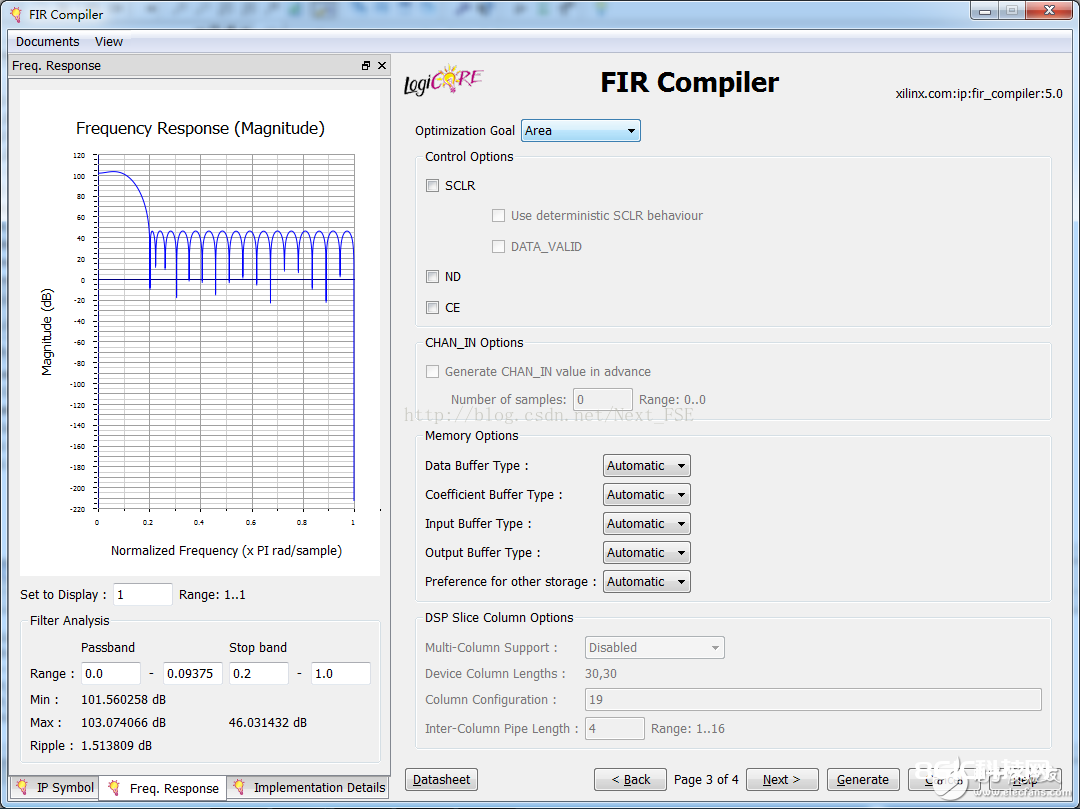

1. 看图说话,根据s6的FIR,k7与其规划办法相同,都是5.0版别

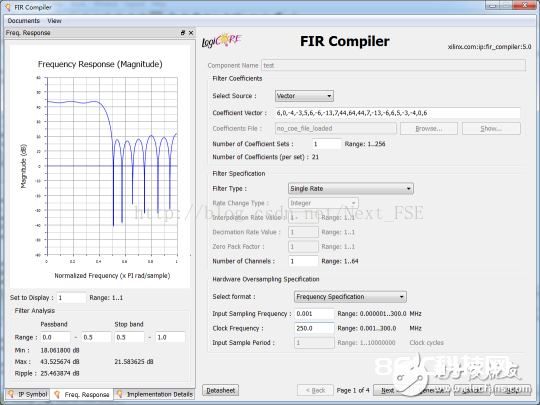

2. (1)左面的部分是通带阻带规划,如图通带0.0-0.5pi,阻带0.5-1.0pi。(明显,低通滤波器是以2pi为周期关于pi对称,所以只需求规划0到pi的部分)

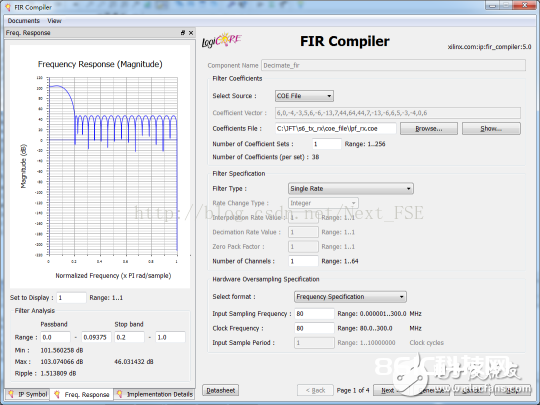

例如,滤波器参数80MSPS,通带0-3.75MHz,阻带8-40MHz,那么通带参数0.0-0.09375pi,阻带参数0.2-1.0pi。

(2)改成coe方式,然后找到coe文件,用“show”查看滤波器系数。

留意:IP核生成后不能替换coe文件,coe文件数据不能更改,复制到其他目录下或许其他电脑内都会导致IP核失效。

解决办法是删去IP核重建,并且需求在ipconfig文件夹内手动删去文件。

(3)时钟频率与输入采样数据速率。输出数据速率与输入采样数据速率持平。时钟频率指的是提供给FIR作业的时钟频率,该参数影响复用,也便是影响DSP的复用。

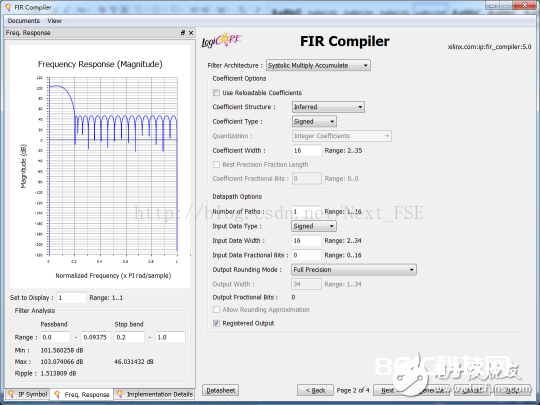

3、 (1)滤波器系数设置,一般都是有符号数,宽度拜见coe文件。

(2)输入输出设置,一般都是有符号数,输出数据挑选全精度输出,在FIR模块外面再用assign代码截位,这样截位可控。

4. 一般挑选优化方针为area,节省资源。

5. 生成

点击generate就能够了

滤波器输出截位设置与测验:

滤波器截位调整的首要意图是使得输入峰峰值挨近最大量程的正弦波时通过该滤波器能够发生峰峰值挨近最大量程的输出正弦波,这样做的意图是滤波器输出的精度最大化。

好了,上面讲了滤波器系数的发生及ISE中生成FIR IP核的办法,下面讲一个问题,便是滤波器延时的问题。

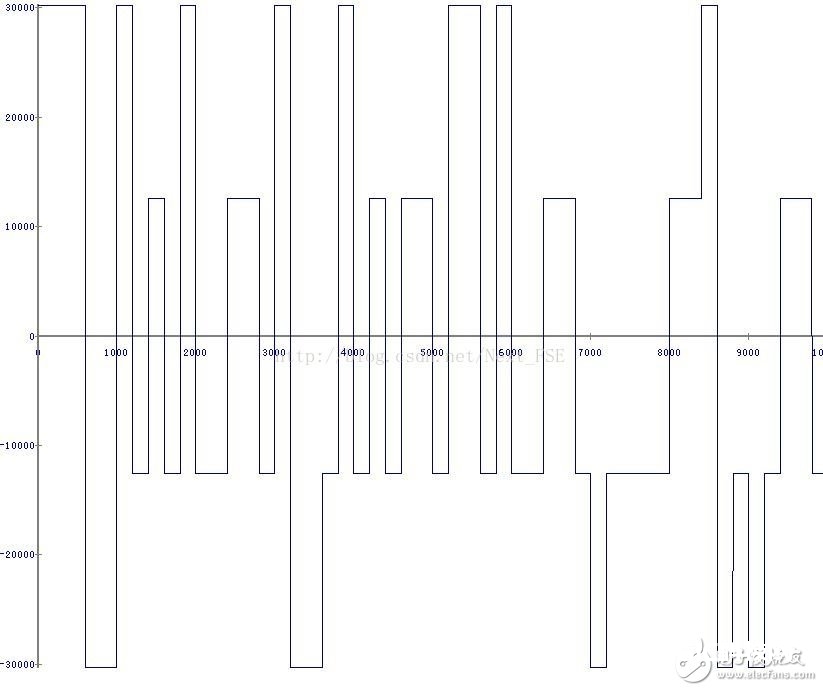

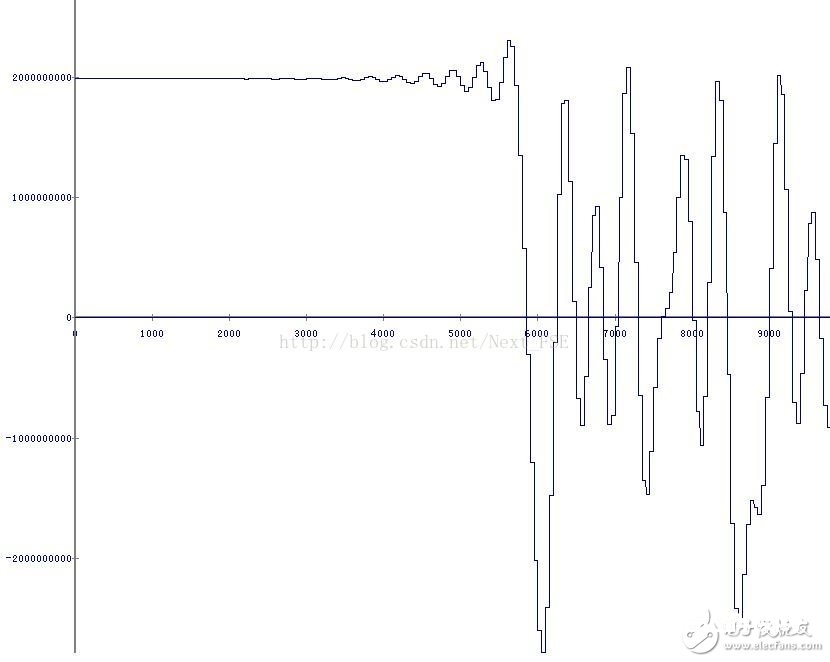

在FPGA工程中调用FIR IP核,把系数文件导进去,输入进FIR IP核的数据速率为2.5k,采样速率为10k,FIR作业时钟为50M。接着用Chipscope抓取数据时发现第一个送进滤波器的数据会延时11ms输出,直接上图。第一张图是输入滤波器数据,第二张图是滤波器输出数据

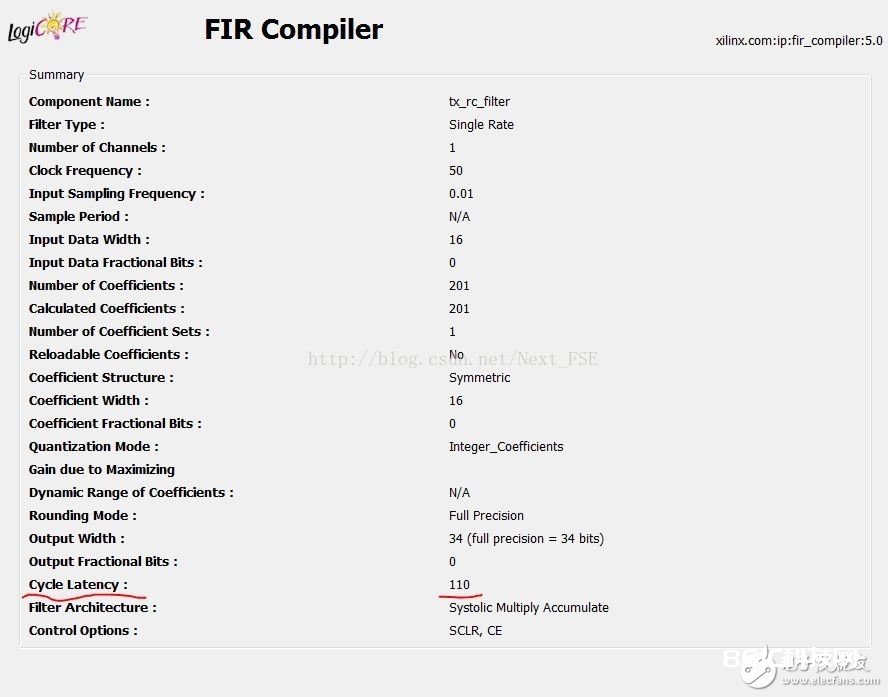

后来查了一下FIR的datasheet,发现里边的确有这个延时相关的信息,数据手册上说这个延时其实能够直接在生成IP核的最终一页的Summary中看到。。。。。。

翻开IP核后的确有这一项,并且数值也为11ms

在数据手册中也解说了这个时延是FIR 的iniTIal startup latency (初始化启动时延)

便是说FIR会有一个初始化的时刻,初始化完成后才开端正常作业,而这个时延的巨细与滤波器的参数有关,即滤波器阶数、通道数、系数是否对称,时延是这些参数的一个函数,可是没有给出计算公式。所以只能了解这个时延终究是什么。。。。。。

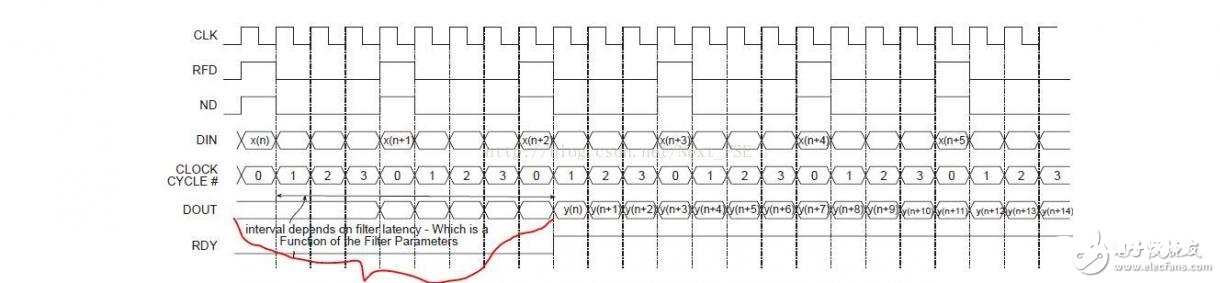

这儿还有一个时延的阐明,贴个图

翻译:

FIR的时延周期个数是阶数、滤波器类型、通道个数及系数是否对称的函数。时延周期个数指的是从RFD失效(标明一个DIN引脚数据现已被采样到)到RDY引脚有用(标明滤波器输出一个有用的数据)。

当输入数据速率与 ip core的作业时钟相同的时分,RFD信号引脚在每一个周期都不会失效。相同关于单数据速率滤波器,RDY引脚也一向坚持有用(便是说当作业时钟与采样时钟持平时,每一个时钟周期输出的数据都是有用的)。在这种状况下,周期延时个数就标明输入到FIR的采样数据到这个数据输出时需求通过的周期个数。

关于那些将FIR装备成具有多通道抽取或内插功用的状况,IP 核就会包括一些采样的缓冲器,这些缓冲器会发生延时,延时个数与缓冲器的巨细有关。此刻延时周期个数标明的是从输入的最终一个采样数据的RFD信号失效(标明输入数据现已接纳)到RDY信号的有用(输出数据有用)。