前语

图画的收集和显现体系有很多种,本文介绍的依据CMOS图画传感器芯片OV5017和CPLD的图画收集显现体系具有体系简练、操控便利的特色。

1 CMOS图画传感器的一般特征

现在,CCD(电荷耦合器材)是首要的实用化固态图画传感器材,它具有读取噪声低、动态规模大、呼应灵敏度高级长处。但CCD技能难以与CMOS技能集成于同一芯片之中。这样,比如守时发生、驱动扩大、主动曝光操控、模数转化及信号处理等支撑电路就不能与像素阵列做同一芯片上,以CCD为根底的图画传感器难以完成单片一体化,因此具有体积大、功耗高级缺陷。 CMOS图画传感器是近向年开展较快的新式图画传感器,因为选用了相同的CMOS技能,因此能够将像素阵列与外围支撑电路集成在同一块芯片上。实际上,CMOS图画传感器是一个较完好的图画体系(Camera on Chip),一般包含:一个图画传感器中心、单一时钟、一切的时序逻辑、可编程功用和模数转化器。其根本结构见图1。与CCD比较,CMOS图画传感器将整个图画体系集成在一块芯片上,具有以下长处:

(1)体积小、重量轻、功耗低;

(2)编程便利、易于操控;

(3)均匀成本低。

2.OV5017的根本功用

OV5017是美国OmniVision公司开发的CMOS是非图画传感器芯片,该芯片将CMOS光感应核与外围支撑电路集成在一起,具有可编程操控与视频模/数混合输出等功用,其输出的模仿视频为是非图画,与CCIR规范兼容。

OV5017芯片的根本参数为:

(1)图画尺度4.2mm×3.2mm,像素尺度11μm×11μm;

(2)信噪比SNR》42dB;

(3)帧频50时,最小照度为0.5lux@f1.4MHz;

(4)帧频50时,峰值功耗小于100mW。

OV5017输出模仿视频信号,格局为逐行扫描。OV5017内部嵌入了一个8bit的A/D,因此能够同步输出8位的数字视频流D[7…0]。在输出数字视频流的一起,还供给像素时钟PCLK、水平参阅信号HREF、笔直同步信号VSYNC,便于外部电路读取图画。

OV5017的像素阵列为384×288,分为16×16的子块,每个子块巨细为24×18,能够在整个图画的部分开窗,输出窗口中的图画。

3 CPLD简介

CPLD是Complex Programmable Logic Device的简称。它是从PAL、GAL根底上开展起来的高密度PLD器材,它们大多选用CMOS、EPROM、EEPROM和快闪存储器(Flash Memory)等编程技能,因此具有高密度、高速度和低功耗等特色。与FPGA(Field Programmable Gate Array)的区别从电路办法来讲最大的区别是CPLD不需要装备器材。因此电路上比FPGA简略。而且在调试上面也很简略。本体系就选用CPLD,型号为Altera公司的EPM9320RC208-15。

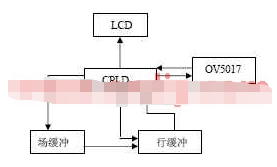

5. 依据OV5017和CPLD的图画收集显现体系框图

作业流程:CPLD操控OV5017的功用而且承受它的数据信号与行场同步和时钟。由CPLD发生行场缓冲器和LCD的操控信号。

5.1要害信号剖析。

Ov5017的像素时钟为fp=7.19MHz。输出为384×288。CPLD的时钟是f=27 MHz,场缓冲的写时钟是fvw=7.19MHz, 读时钟是fvr=6.75MHz,行缓冲的写时钟是flw=6.75MHz, 读时钟是flr=13.5MHz ,LCD的显现时钟是flcd=27MHz。在这种时钟的规划下完成了视频数据信号的采样和一点变两点,一行变两行的功用。最终的显现是640×480。fp信号由ov5017发生,fvw=fp。fvr=1/4f flw=fvr flr=2flw flcd=f。

5.2规划行场扫描时序

一般有两种办法:查找表办法和编程逻辑办法。查找表办法首要由存储芯片构成,如SRAM、EPROM、PORM等。使用时,先依据所要发生的时序在存储单元写入相应的数值,查表时再从表内读出时应存储单元的数值,以构成扫描时序。扫描时序查找表分为行扫描时序查找表和场扫描时序查找表。场扫描时序查找表的输入时钟由行同步脉冲供给。用查找表构成时序的办法存在体积大、核算烦琐的缺陷。跟着大规模逻辑芯片的呈现,使用编程逻辑办法发生行场扫描时序是一个开展方向。这种办法具有电路简略、功用强、修正便利、可靠性高级长处。

VHDL言语程序(略)。

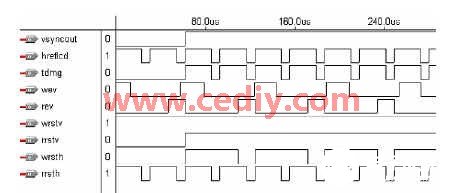

本体系部分信号的仿真波形如下:

信号阐明:

vsyncout:LCD的场同步 hreflcd:LCD的行同步

tdmg:LCD的数据显现答应使能 wev:场缓冲的写答应

rev:场缓冲的读答应 wrstv:场缓冲的写复位

rrstv:场缓冲的读复位 wrsth :行缓冲的写复位

rrsth :行缓冲的读复位

在这些信号的操控之下,OV5017输出的384×288的视频数据最终以640×480的格局在LCD上面显现出来。

这种用VHDL发生扫场描时序的办法简略、易读,而且易于修正。在代码中只须修正一些时序参数就能发生恣意时序的波形,具有很好的可重用性。

6.总结

该体系因为省掉了A/D等器材,因此具有结构简略、体积小、功耗低一级长处。一起,因为OV5017内部嵌入曝光、增益、开窗等操控电路,而且编程便利,这就提高了收集体系在功用上的灵活性。选用CPLD技能规划的LCD操控器,大大减少了电路板的尺度,一起增加了体系可靠性和规划灵活性。这种用VHDL言语完成LCD驱动时序生成器的办法,具有简洁易读和可重用性强的特色。本体系适合于监控、多媒体等使用规模。

责任编辑:gt