依据单核结构的嵌入式处理器越来越难以满意日益增长的嵌入式多媒体运用的处理需求,多核嵌入式结构已成为处理这一问题的有用途径,一起也为怎么充沛开发运用多核结构的运用软件带来应战。现在的编译技能和开发工具需求更精细,才能使多核结构的运用获得成功。大大都并行软件都是经过手艺转化办法将次序程序转化为并行程序来完结的,由于缺少具有多核认识的开发工具,使得软件难以进行功能评价。因而,假如没有预先有用牢靠的工程规划,将不得不面临运用软件功率低下以及推迟产品上市时刻等问题。

软件结构为多核运用软件的开发供给了一个更好的起点,能够协助缩短开发时刻。本文将具体阐明嵌入式多媒体运用软件的规划结构,一起,本文的数据流模型也可扩展到许多其它运用中。该结构归纳了多媒体运用软件固有的数据并行结构,并阐明晰怎么经过运用底层架构来有用办理数据流。

在规划并行软件的进程中有两大应战:一是开发有用的并行算法,二是有用地运用存储器、DMA(直接存储器拜访)通道和互连网络等同享资源。在该进程中,次序运转的运用程序的功能可依据可用处理器核的数目进行扩展。

完结运用程序的并行处理常常有多种办法。有些运用程序表现出固有的并行特性,而其它的则具有极端杂乱且不规矩的数据存取形式。但总的来讲,科学核算类的运用程序和多媒体运用程序的并行化一般易于完结,由于它们的数据存取形式比那些操控类运用程序相对简单猜测。本文要点评论针对多媒体算法的并行技能,这类算法需求很高的处理才能,而且更适合嵌入式体系运用。

多媒体运用程序中存在数据的并行等级。一组数据帧与数据帧中的一个宏块之间的并行粒度有很大不同。一般来讲,粒度越小,同享单元(如处理器核和DMA通道等)之间所需的同步等级越高。粒度越小,并行程度就越高,网络通信量越小;粒度越大,同步要求就越低,但网络通信量会增大。因而,依据运用的不同类型和体系需求,软件结构也界说了不同的并行等级。

需求阐明的是,可扩展并行软件的开发还依赖于对互连网络、分级存储器体系以及外设/DMA资源的有用运用。体系严厉的低功耗和低成本要求对一切这些要素都会构成约束。在多核环境下编程时,有用运用这些资源需求进行立异。本文提出了一些在ADI公司的Blackfin ADSP-BF561双核处理器上有用办理资源的设想。

多媒体数据流剖析

为了完结数据并行,需求在数据流中找到这样一个或一组数据块:能够独立处理并将其“喂”给一个处理元件。独立的数据块能够下降同步开支并简化并行算法。要找到这种数据,有必要澄清运用的数据流模型,或者说“数据存取形式”。

关于大大都多媒体运用,能够将数据存取形式看成是2D(空间域)和3D(时刻域)操作形式。在2D形式中,独立的数据块被约束在单个数据帧内,而在3D形式中,独立数据块能够横跨多帧。在空间域中,能够将帧区分为由N个接连行和视频帧宏块组成的片段,而在时刻域中,能够对数据流进一步细分到帧级或图片组(GOP)级。

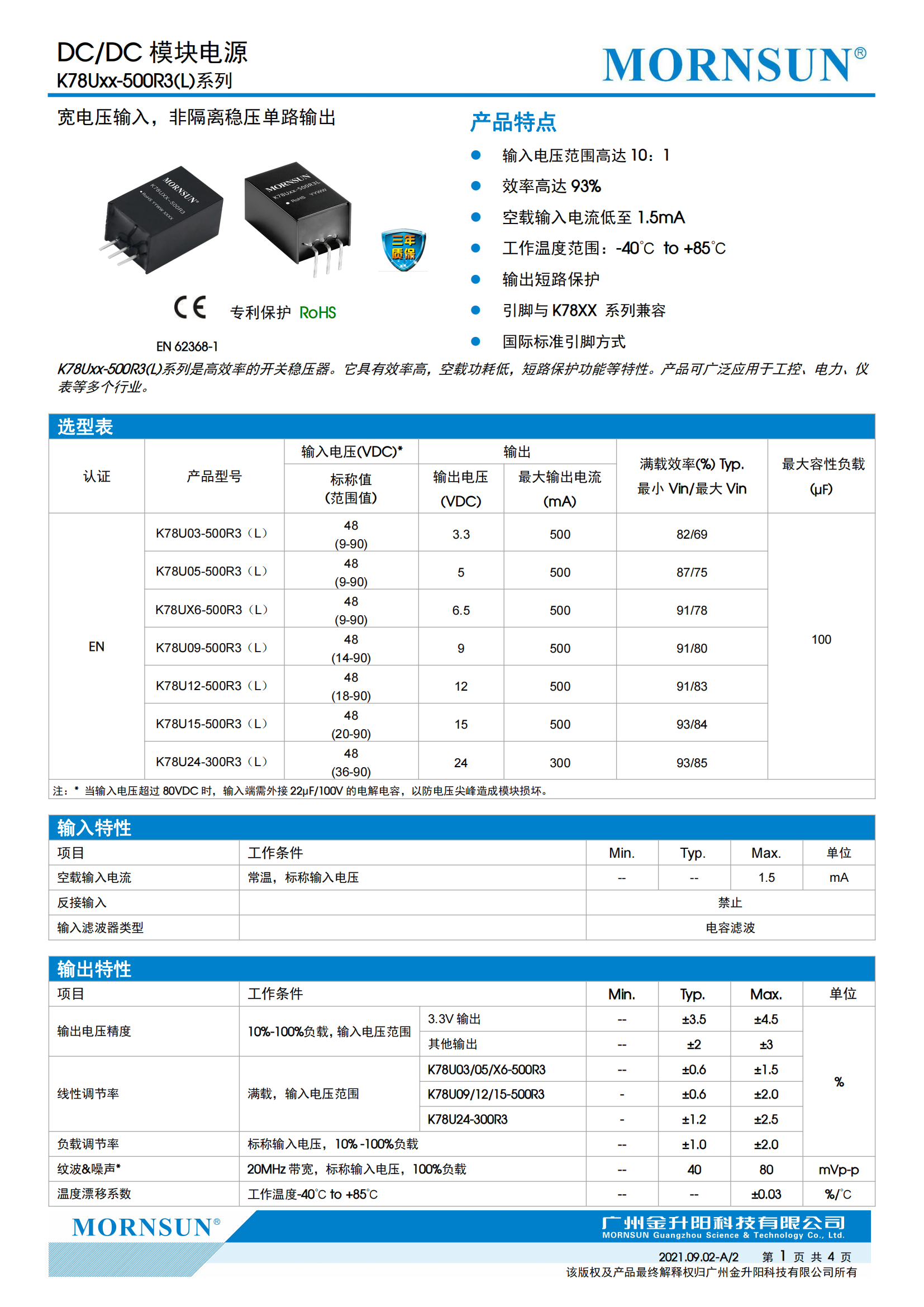

选用片段或宏块数据存取形式的算法对同步性要求较高,但网络传输量较少,这是由于分级存储器体系只需存储图画数据的一部分。关于帧或图片组类型的数据存取形式,分级存储器体系则需求存储很大都据,但对同步性的要求则相对低得多,这是由于体系的并行粒度更大。图1阐明晰多媒体运用软件中的并行等级,一起显现了四个等级的相对同步要求和网络通信量。

图1 多媒体运用展现了不同的数据并行等级,这些等级对应不同的同步要求和网络通信量。

多核结构剖析

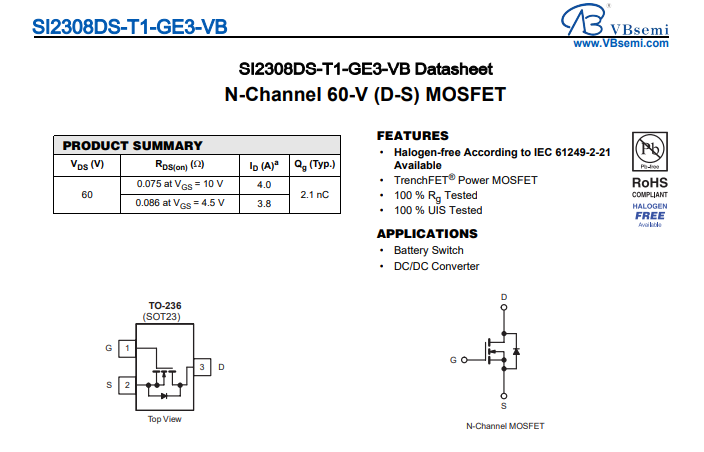

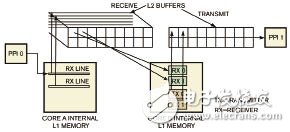

图2显现了ADSP-BF561的结构,它包含独立的指令和数据存储器,别离归于两个处理器核专有,此外还包含同享的L2存储器和外部存储器。用户能够运用可装备的裁定计划将一切外围设备和DMA资源衔接就任一处理器核。该处理器有两个DMA操控器,每个DMA操控器由两组MDMA(存储器DMA)通道组成。L2存储器与每个处理器核之间经过独立的总线衔接,外部存储器与两个处理器核之间则由一条同享总线衔接。

图2 ADSP-BF561的结构包含独立的指令和数据存储器,别离归于两个处理器核专有,此外还包含同享的L2存储器和外部存储器。

一切结构都运用DMA办法将数据流送入分级存储器体系。另一种挑选是高速缓存,它不办理任何数据。假如清楚方针运用的数据存取形式,就能够运用DMA引擎对数据进行有用的办理。而运用高速缓存需求忍耐不确定的拜访时刻、高速缓存未射中的价值,以及需求较高的外部存储器带宽。运用DMA引擎,能够在处理器核恳求数据之前就将数据送入L1存储器,体系在后台履行传输操作,而不会由于数据项恳求使处理器核暂停作业。

由于每个DMA操控器上都有两组MDMA通道,因而体系能够将MDMA通道在处理器核上均匀分配,然后能够对称地进行并行处理。

关于数据存取形式粒度较小的运用,能够轻松地运用对L1和L2存储器的快速拜访。也能够直接将独立的数据块从外设接口传送到L1或L2存储器,而不需求拜访慢速的外部存储器,这样能够节约名贵的外存储器带宽和MDMA资源,并缩短数据传输时刻。

关于数据存取形式粒度较大的运用,存储器或许成为瓶颈,由于较小的L1和L2存储器级不足以包容很多的数据帧。但是,很大都据帧之间尽管存在数据相关性,但这种相关一般也仅存在于跨数据帧的较小数据块上。假如能将一切相关的数据帧存放在一个较大的存储空间(外部存储器)中,就能够将每一帧中的独立数据块相继送入闲暇的处理器核进行处理。假如这些独立的数据块比数据帧小得多,契合L1或L2存储器的容量,就能够削减存储器存取推迟,高效地处理数据。

尽管L2和外部存储器都有独立的总线衔接,但两个处理器核仍同享这些存储器接口总线。因而,应当尽量防止两个处理器核一起对同一等级的存储器进行存取操作,防止因总线抵触而停止作业。为了削减总线抵触情况,结构应考虑代码和数据目标的映射,让一个处理器核首要拜访L2存储器核,而另一处理器核则首要拜访外部存储器。在这种情况下,尽管处理器核完结大都外部存储器拜访会呈现较大的拜访推迟,但总的拜访推迟依然小于总线抵触的价值。

结构把一切输入外设接口分配给一个处理器核,把一切输出外设接口分配给另一处理器核。结构运用视频输入/输出接口,例如PPI(并行外设接口)来输入和输出视频帧。BF561架构有两个PPI接口。

假如中止处理时刻比数据流的处理时刻要短,则可将一切的外设接口分配给一个处理器核以便于编程,较短的中止处理时刻不会影响两个处理器核的负荷平衡。

软件结构的主张模型

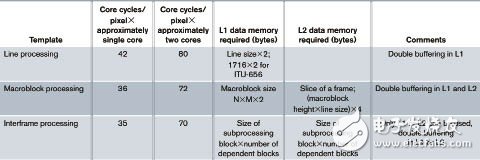

依据数据存取形式的粒度,能够界说四种软件结构:行处理(空间域)、宏块处理(空间域)、帧处理(时刻域)以及GOP处理(时刻域)。假如某个运用程序的数据存取形式适于这四种模型中的任何一种,就能够选用相应的结构。假如一个数据流有两种或更多的处理算法,还能够将多种结构结合起来,完结非对称的并行处理。

内行处理形式中,相关性只存在于行级,也就是说,只存在于相邻像素之间。每行数据构成一个数据块,各处理器核都能够独立处理。

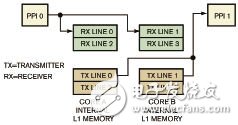

图3显现了行处理结构的数据流模型。处理器核A处理视频输入,处理器核B处理视频输出。核A和B之间的数据由独立的MDMA通道组进行办理。L1存储器运用多个缓神器,能够防止处理器核与外设DMA拜访总线的抵触。两个处理器核之间每行数据的同步经过计数信号量完结。在这种结构中,选用单处理器核办法将数据直接存入L1存储器也具有优势,能够节约外部存储器带宽和DMA资源。这种结构的运用实例包含颜色改换、直方图均衡化、滤波和采样。

图3 行处理结构的数据流模型。处理器核A处理视频输入,处理器核B处理视频输出。

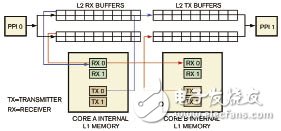

图4显现了宏块数据拜访形式的数据流模型,能够在两个处理器核之间替换传送宏块。L2存储器具有多个片段缓冲器,独立的MDMA通道将宏块从每个处理器核的L2存储器传输到L1存储器。L1存储器也有多个缓神器,用以防止DMA与处理器核拜访总线的抵触。与行处理结构相似,该结构中处理器核A操控输入视频接口,处理器核B操控输出接口,计数信号量完结两个处理器核之间的同步。这种结构的运用实例包含边际检测、JPEG/MPEG编码/解码算法和卷积编码。

图4 在双核宏块数据拜访形式中,L2存储器具有多个片段缓冲器,独立的MDMA通道将宏块从每个处理器核的L2存储器传输到L1存储器。

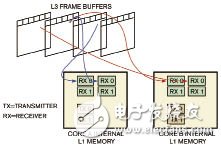

在帧级处理形式中,外部存储器存储相关帧。依据数据帧(宏块或行)之间的相关性粒度,体系将数据帧的子块传送到L1或L2存储器。图5显现了帧级处理结构的数据流模型。在这种情况下,假定某个宏块在多个帧之间存在相关,则体系将数据帧的宏块传送至L1存储器。与其它结构相似,该结构中处理器核A操控输入视频接口,处理器核B操控输出接口,经过计数信号量完结两个处理器核之间的同步。这种结构的运用实例包含运动检测算法。

图5 在帧级处理流程中,外部的存储器存储独立帧

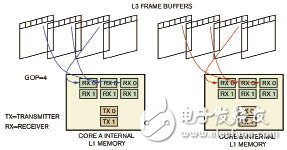

在GOP级处理形式中,每个处理器核处理多个相继的数据帧。帧级处理结构与GOP级处理结构之间的差异在于,前者是在帧内完结空间区分,后者则经过时刻区分(帧序列)完结并行处理。关于GOP数据拜访形式,相关性存在于一组数据帧内部,两组帧之间数据不存在相关性。因而,处理器核能够独立处理每一组帧。图6显现了这种结构的数据流。与帧级处理结构相似,体系能够将帧数据块传送至处理器核的L1存储器。为了有用运用外部存储器的交织存储库结构,体系在处理器核间均衡地分配存储库。ADSP-BF561的每一个外部存储库都支撑多达四个内部SDRAM存储库。这种结构的运用实例包含MPEG-2/4等编码/解码算法。

图6 在GOP级数据拜访形式中,相关性存在于一组数据帧内部,两组帧之间数据不存在相关性。

在实践运用中,体系或许运用多种算法处理数据流,而每种算法都或许用到不同的数据存取形式。这种情况下,能够针对特别运用将几种结构结合起来运用。为运用多核结构,能够选用流水线处理来完结并行操作,但这种并行操作是不对称的,由于不同处理器核上或许履行不同的核算。但是,体系能够分配一些其它的使命到处理器核的闲暇指令上,在坚持灵活性的一起到达处理器核的作业量平衡。图7显现了行级处理和宏块处理相结合的结构的数据流模型。

图7 行级处理和宏块处理相结合的结构的数据流模型

在某些其他运用中,多个数据块之间也会存在数据相关性,数据存取形式依然是可猜测的,但它扩展到了一个宏块或一行的粒度之外。例如,运动窗口查找就或许运用几个相邻的宏块。数据存取形式依然是可猜测的,但体系在算法的屡次迭代之间要拜访多个数据块。这种情况下,能够对软件结构进行批改,以完结有用的并行操作。例如,假如多行间存在相关,能够经过调整行处理结构,将N个接连行的帧片段传送到每个处理器核的L1存储器。运用相似的办法,还能够对宏块处理结构进行扩展,以便将多个宏块从L2存储器送入内部L1存储器。

软件结构剖析

为了对双核处理的软件结构进行评价,ADI公司运用数据流模型首先开发了一款单核运用软件,然后与双核计划进行比照。Blackfin独有的体系优化技能也能有用地运用可用带宽。为了简化剖析,ADI公司只比较了根本结构的处理速度,而没有考虑几种架构的组合。

所谓周期,是指为了满意NTSC(美国国家电视体系委员会)视频输入的实时约束条件而用于处理数据流的处理器核核算周期。关于一个以600MHz速度运转的处理器核,为了满意实时约束条件,处理每一像素可用的总周期数为44周期/像素。任何对数据流的处理器核拜访都只需求一个单核周期,由于一切数据拜访都是对L1存储器的拜访。所示的周期数不包含中止推迟。

如表1所示,双核结构将一切结构的处理速度有用提高了两倍。表中还阐明晰每个处理器核的L1存储器运用量,以及各种结构需求的同享存储器空间。这些结构运用ADI公司的DD/SSL(器材驱动/体系服务库)完结对外设和数据的办理。

表1:结构阐明

责任编辑:gt