1 导言

滤波器便是选频电路,可答应一部分频率的信号经过,而按捺另一部分频率的信号,它在数据搜集、信号处理和通讯体系等范畴具有重要作用。这儿提出一种根据开关电容有源滤波器的程控滤波器,可自由挑选低通、高通和带通形式,也可步进调理滤波器通带截止频率和放大器增益。该程控滤波器规划成本低、完结简略,可广泛应用于数字信号处理、通讯、自动操控等范畴。

2 体系规划方案

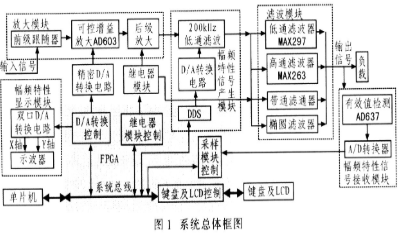

该体系规划由可控增益放大器、程控滤波器、椭圆滤波器和幅频特性测验仪4部分组成。图1为其体系整体规划框图。

图1中,可控增益放大器部分是以AD603作为中心器材,完结0~60 dB之间的增益调理。AD603为低噪声精细可变增益放大器,温度稳定性高,其内部由R-2R梯形电阻网络和固定增益放大器构成,加在其梯形网络输入端的信号经衰减后,由固定增益放大器输出,衰减量由加在增益操控接口的参阅电压决议;其增益与操控电压呈线性关系,经过单片机操控,而由D/A转化器发生准确的参阅电压来操控增益,然后完结较准确的数控,一起可下降搅扰和噪声。程控滤波器部分选用开关电容滤波器完结。开关电容滤波器是由MOS开关、MOS电容和MOS运算放大器构成的集成滤波器,其开关电容组在时钟频率的驱动下,可等效成1只与时钟频率有关的等效电阻R=1/2πCfc。其间C为开关电容组的电容,fc为滤波器时钟频率。

当用外部时钟改动fc时,等效电阻R改动,然后可改动滤波器的时间常数,也改动滤波特性。

开关电容滤波器可直接处理模仿信号,而不用像数字滤波器需求A/D、D/A转化,这样简化电路规划,进步体系的牢靠性。该体系选用集成的开关电容滤波器MAX297完结低通滤波,选用MAX263完结高通滤波。

运用电感和电容可建立各种类型的滤波器该体系运用无源LC滤波器技能,参照滤波器规划手册相关参数,比较容易地完结较抱负的四阶椭圆低通滤波器,选用有源RC滤波器完结带通滤波器。

放大器输出信号经过滤波器后加在1 kΩ的负载上,各滤波器的输出切换由继电器完结。该体系以单片机和FPGA为操控中心,辅以DDS扫频电路,经有用值检波电路,完结幅频特性的测验与显现。体系功能目标到达规划要求,作业牢靠,用户界面友爱。

3 理论剖析与电路规划

3.1 放大器模块

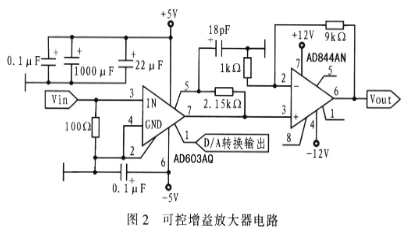

可变增益放大器AD603的操控电压与增益呈线性关系,其增益为G(dB)=40×VG+G0。其间,VG为差分输入电压,VG规模为-500~500 mV。G0是增益起点,接入不同反应网络时G0也不同。该体系选用AD603的通频带为30 MHz的典型接法,此刻G0为20 dB,则增益为0~40 dB。AD603后由继电器操控接入增益为20 dB的同相放大器,然后完结0~60 dB的增益规模,电路如图2所示。

选用16位串口D/A转化器MAX542输出电压操控AD603的增益,其增益步进可到达0.1 dB,终究设定体系的增益步进为10 dB。

3.2 滤波器模块

3.2.1 低通滤波器

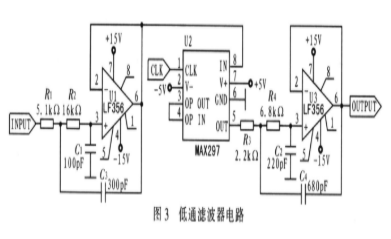

体系选用开关电容滤波器MAX297完结低通滤波器。 MAX297是8阶开关电容式低通椭圆滤波器,其滚降速度快,从通频带到阻带的过渡带很窄。它由带有求和与换算功用的开关电容积分器模仿梯形无源滤波器网络而构成,其时钟频率与通频带之比为50:1,改动时钟频率,通频带在0.1 Hz~50 kHz规模内改动,增益在通频带内存在的±0.1 dB的动摇。

体系设计时,特别要注意MAX297的运用,当信号频率和采样频率同频,且相位合当令,开关电容组在电容上顺次搜集起伏相同的信号为幅值信号,相当于输入直流信号。因而采样电容发生直流信号,使得滤波器输出也直流电平。同理,当信号频率为采样频率的整数倍时,也会呈现相同现象。要除掉这种现象,须约束输入信号规模,使之小于开关电容滤波器的采样频率,即时钟频率。因而在运用MAX297时.应在其前面添加模仿低通滤波器,有用滤除采样频率及其以上的高频信号。而在其后边也应添加低通滤波器,滤除信号的高频重量,使波形愈加滑润。详细完结电路如图3所示。

3.2.2 高通滤波器

体系选用开关电容滤波器MAX263完结高通滤波器。该器材内部结构与MAX297类似,但其间心频率f0与Q值由外置引脚编程设置。将MAX263的Q值设置为0.790,fclk/f0设置为185.35。经过改动外部时钟fclk操控高通滤波器的3 dB截止频率f0。

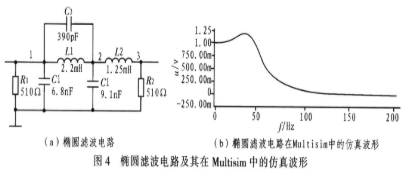

3.2.3 椭圆低通滤波器

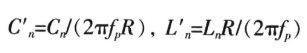

选用无源LC椭圆低通滤波器完结,从滤波器规划手册上查表得四阶椭圆无源滤波器在θ=19°,Ωs=3.311时,相应归一化参数:C1=1.210 F,C2=0.062 42 F,L2=1.220 H,C3=1.891 F,L4=0.846 9 H。取无源滤波器的端间匹配阻抗为R=510 Ω,截止频率fp=50 kHz代入公式:

式中,Cn,Ln表明归一化的电容值,电感值;C‘n,L’n表明以fp为通带3 dB衰减的低通滤波电路中所对应的电容值、电感值。核算成果为:C1=7.56μF,C2=390 pF,L2=1.98 mH,C3=11.81μF,L4=1.38 mH。将上述值转化为标称值后,得到图4所示的电路原理图和仿真波形。

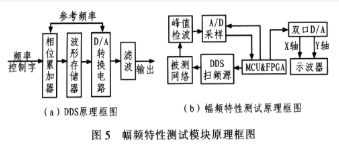

3.3 幅频特性测验模块

FPGA由DDS发生0~200 kHz规模内的扫频信号,DDS发生信号的频率稳定度较高,并且信号的频率步进和信号幅值操控便利。DDS以Nyquist时域采样定理为根底,在时域中进行频率组成。DDS的根本作业原理:每个参阅频率fs上升沿到来时,N位的相位累加器值便依照频率操控字K的长度添加一次,输出所得相位值,正弦查找表将相位信息转化为相应的正弦起伏值。在fs和N必定的情况下,输出波形频率由频率操控字K决议。以必定步进循环添加频率操控字K,输出频率改动的扫频信号。

扫频信号经过被测网络后,由AD637检测有用值,即运用各个频点经过网络后的有用值在示波器上显现其幅频特性图。AD637的外围电路简略,并且当输入峰峰值大于2 V时,其丈量差错在100 Hz~1 MHz的规模内可疏忽。图5为幅频特性测验模块原理框图。

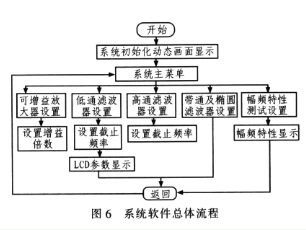

4 体系软件规划

体系软件规划主要有3部分:(1)设置放大器的增益,操控凹凸通等滤波器的切换并设定其截止频率;(2)幅频特性测验.发生DDS信号的频率操控字,操控频率步进,丈量并显现信号经过滤波器后的幅值信息;(3)人机交互功用。体系软件规划选用模块化思维,模块内部选用层次化规划,将硬件接口处理及初始化部分作为底层的子程序,操控硬件接口的中止并向上层供给接口读取数据;中间层程序完结底层数据的搜集和处理,将其成果上传至终究的上层功用操控程序;最终主程序经过调用相关的功用操控模块完结对整个体系的构建。体系软件整体流程如图6所示。

5 测验成果

(1)用信号源在放大器输入端输入峰值为10 mV的正弦信号,在100 Hz~40 kHz规模内,用双踪示波器检测放大器的通频带。预置放大器增益,用低频毫伏表测验输出信号的有用值并检测其实践增益,核算增益差错,查验增益步进。测验成果表明放大器的增益规模为0~60 dB,步进为10 dB,增益差错小于0.5%。

(2)将放大器增益设置为40 dB,输入信号为10 mV,挑选高通或低通滤波器模块,预置滤波器截止频率,用低频毫伏表和双踪示波器测验其实践截止频率,核算相对差错,并检测截止频率步进和(低通)或(高通)处的电压总增益,检测到该处电压总增益不超越20 dB。测验成果表明高通和低通滤波器的截止频率在1~30 kHz内可调,频率步进为1 kHz,且截止频率差错小于2%。

(3)椭圆滤波器的测验,将放大器的增益设置为40 dB,用低频毫伏表和示波器丈量其通带动摇、-3 dB截止频率和200 kHz的总电压增益。测验成果表明该椭圆滤波器的带内动摇小于0.2 dB。截止频率为50.15 kHz,在200 kHz处衰减58.35 dB。

(4)幅频特性测验仪的测验,挑选各滤波器为被测网络,设定测验信号扫频带宽和步进开端扫频,调查液晶显现屏上的幅频测验图,成果表明幅频特性曲线与被测网络理论核算成果比较相符。

6 定论

该体系规划完结各项规划目标,前级放大器选用可控增益放大器完结0~60 dB的增益改动规模,开关电容滤波器完结截止频率在1~30 kHz规模内数字可调,选用无源LC网络完结四阶椭圆低通滤波器,运用高速D/A转化器和有用值检波电路完结幅频特性测验仪,体系功能杰出。体系规划简略,可较好地完结滤波器的程控,运用便利,具有较高的性价比、实用性和运用价值。

责任编辑:gt