1.导言

NAND FLASH因为其存储的容量大,小体积,一起读写速度快,外围电路简略而成为现在存储运用中的主流产品。但NAND FLASH的写操作比较特别,在存储数据时要先写入存储指令和存储地址,编程时不能对其履行任何操作。传统的由单片机作为中心的收集选用查询的办法对NAND FLASH进行编程,不只操作杂乱,并且减慢了存储速度。

为此规划了一种根据DMA传输办法的高速存储阵列。选用DMA办法完成了对指令和地址的传输,并完成流水线存储进程,加快了存储速度。并且体系以FPGA为渠道,集成度高,具有灵敏的总线宽度,拓宽了存储阵列的运用环境。

2.体系结构

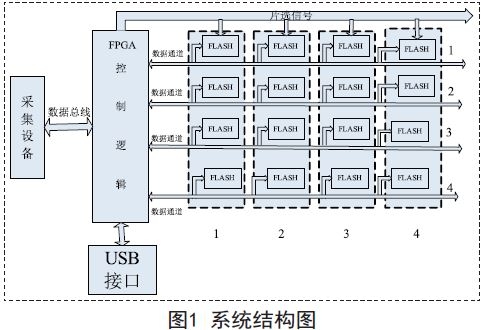

数据存储体系结构如图1所示,包括以下3个部分:

(1)FPGA,数据存储体系的中心,集成度高,功耗低,内部嵌有总线结构灵敏,并行处理能力强的软处理器核MICROBLAZE,并有用户自定义的IP核,能够完成对闪存阵列的操控和数据的正确存储,并且能够将阵列中存储的数据上传到电脑,进行数据的后期处理。

( 2 )存储阵列:体系选用4×4阵列办法,由SAMSUNG公司的K9NBG08U5A建立而成。构建闪存阵列时,一切FLASH运用相同的操控信号;同一列的FLASH的片选信号相同,但数据通道不同;同一行的FLASH的片选信号不同,而数据通道相同。

(3)USB接口:上位机和存储体系的交互经过USB接口进行,上位机将指令和装备信息经过USB接口传入FPGA,使FPGA内部的MICROBLAZE履行相应的操作。数据回读时经过USB接口将数据传回上位机。本规划选用FIDI公司的FT245R作为上位机与FPGA通讯的USB接口芯片。运用FIDI公司供给的D2XX驱动程序,最快的传输速率高达1MBps.

3.DMA规划完成

DMA的作用是操控闪存阵列的操作,到达数据的快速存储。其规划首要包括两部分:DMA办法写指令和地址,流水线操作流程的完成。DMA办法写指令和地址是用硬件的办法将闪存阵列编程需求的指令码和地址按时序释放到数据总线,节省了单片机查询时所糟蹋的时刻;流水线操作流程是DMA对闪存阵列编程阶段等候的时刻的使用,提高了存储速度。

3.1 DMA办法写指令和地址

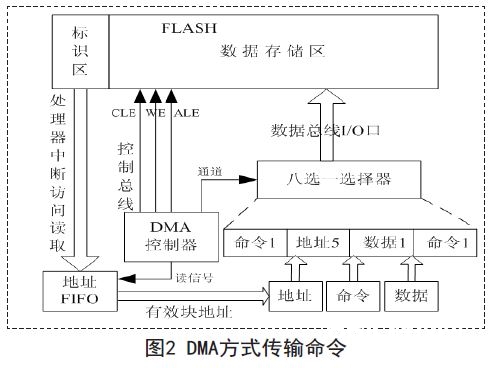

对FLASH进行存储操作时应先向FLASH写入编程开端指令,然后是五个周期的有用块存储地址和2K字节数据,最终写入完毕编程指令。用DMA办法传送指令和地址花费的时刻低于单片机查询的办法,提高了存储速度。因为体系闪存阵列规划小,能够选用全相关的无效块管理办法,其操控简略、算法简单完成。无效块的信息事前缓存于地址FIFO,待数据存储时,由DMA读取。此外每片NAND FLASH的编程指令码相同,所以对每一列闪存操作时,每个FLASH IO口上的数据是相同的。DMA办法写指令和地址如图2所示,相同的地址和指令先并置在一起,然后经过DMA办法发送到数据总线,最终在每个FLASH的I/O口将分配。

图2中的八选一电路的作用是按flash的操作时序将包括存储数据,指令,地址放到FLASH的IO总线上,通道的挑选由DMA操控。与此一起,相应的操控信号ALE、CLE、WE等变为有用电平,完成指令、数据、地址的写入。

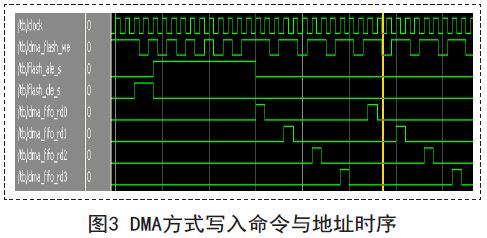

这个部分时序仿真如图3所示。信号线一是频率为50MHz的时钟信号;信号线二是FLASH写信号;信号线三是ALE信号线,当它为高电平时,写入FLASH的地址将锁存到地址寄存器;信号线四是CLE信号,当它为高电平时,写入FLASH的指令将锁存到指令寄存器;剩余的信号是读数据FIFO的信号。

3.2 DMA完成流水线操作流程

K9NBG08U5A对有用数据的存储操作包括加载阶段和编程阶段,编程阶段期间,FPGA不能对FLASH进行操作,因而关于单片F L A S H存储器而言,编程阶段的时刻被糟蹋,不利于到达快速存储。为此可选用时分多路复用的办法对数据进行存储,详细完成办法便是首要对榜首列的Nandflash加载数据,数据加载完后,榜首列Nandflash随后就将进入主动编程状况,当即再加载第二列FLASH.如此循环进行数据加载,直到最终一片加载完成后,再回到榜首片。这样就充分使用了编程阶段的时刻,使存储速度得到提高,此进程也称流水线操作。

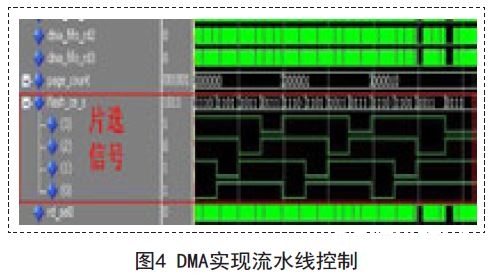

为了完成流水线的存储办法,本文也用DMA操控器完成了对FLASH的片选。如图4所示,图中flash_ce_s代表每列flash的片选信号,其间低电平代表对flash加载有用,从图中能够看出DMA操控器对flash顺次加载,完成了流水线的操作流程。

4.体系验证

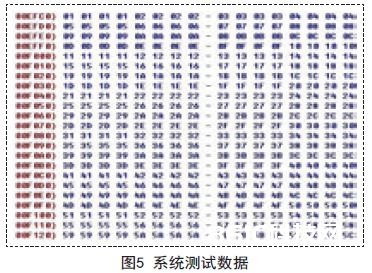

本规划在用户逻辑里规划一个计数时钟为16MHZ的计数器,计数时钟每来一次,就将数据别离缓存于四个FIFO并将数据经过DMA的办法存入闪存阵列体系中。经过上位机将数据回读,如图5所示。

从图中能够看出接连的4个字节的数据都是相同的,它们别离来自4个缓存FIFO的同一个次计数的数据。一起,数据每4个字节是按一递加,即没有呈现数据丢掉的现象。由此可知体系的DMA操控器能够完成闪存阵列对数据的快速,正确存储。

5.定论

本文在测控体系中海量数据的快速存储的基础上提出了一种根据DMA的数据存储阵列体系的规划方案。它是以FPGA为渠道构建的SOPC体系,内含软核处理器Microblaze和包括DMA操控器的用户自定义IP,经过试验验证了本方案所规划的DMA操控器完成了对闪存阵列的编程指令、地址的传输,以及存储阵列的流水线编程,提高了传统的由CPLD与单片机组成的存储测验体系的速度。