总述

实时时钟芯片(RTC)答应一个体系能同步或记载事情,给用户一个易了解的时刻参阅。由于RTC的运用越来越广泛,为了避开规划时呈现的问题,规划者应了解RTCs。

挑选接口

RTC可用的总线接口规模很宽。串行接口包含2线(I2C),3线和串行外设接口(SPI)。并行接口包含多总线(多数据和地址线)和带独自地址及字节数据输入的规划。接口的挑选一般由所用的处理器类型决议,许多处理器包含2线或SPI接口。其它的,如8051处理器及其派生的处理器支撑多路地址和数据总线。时刻坚持非易失性(NV) RAM和SRAM用相同的操控信号,许多处理器都供给这种便利的接口,也包含各种不同的用电池组支撑的RAM。最终,看不见的时钟躲藏电池供电的RAM中并可用64位的软件协议去拜访时钟。

备用电池的功用

在有的运用中,例如VCRS,假如去掉电源, 会丢掉时刻和日期信息,。许多新的运用中,即便主电源去掉了, 要求时刻和日期信息应坚持有用。为了坚持时钟晶振运转,要用到一个主电源或许备用电源,或许一个大容量的电容。在这种状况下,时钟芯片有必要可以在两个电源之间进行切换。

假如有一个电池,例如钮扣型锂电池用作备用电源,当在用备用电源作业时RTC应规划成尽或许少的耗费功耗。电源切换电路,一般状况下由主电源供电,会使电源切换到电池供电,并使RTC进入低功耗方法。微处理器和RTC之间的通讯一般确认(称为写维护),用来使电池供电电流最小和避免数据损坏。

许多时钟芯片都包含一个晶振操控位,一般称之为时钟中止(CH)或是晶振使能位(/EOSC)。此位一般坐落秒存放器或操控存放器的最高位(位7),简直在有这位的一切时钟芯片中,初始电池上的首选状况关于晶振来说是无效的。这答应体系规划者提出制作流程,在装置和测验后,用Vbat进行供电,一般用个锂电池。此刻晶振处于一个中止状况,保存电池到体系电压可以作业。在这个点上,软件/硬件应该发动晶振并促进处理时刻和日期。

在一般状况下,锂电池的作业温度是-40℃到+85℃。电池不能露出在+85℃以上的环境中。含电池和露出电池的引脚的封装,例如灵敏性插座,不该接触到水。浸水使电池短路,因而耗尽电池。

时钟模块,启封和保存期限

在备用电池方法下,时钟的电流耗费首要来自晶振。一切带有嵌入晶振和电池组的时钟模块在出厂时现已构成在里面了而且晶振是不作业的。当晶振不作业时,电池的电流小于自放电电流,或处于室内温度时每年的0.5%.

一些时刻坚持非易失性(NV) RAM模块用到时钟操控IC和一个SRAM,它们从厂家出来时,晶振不作业且电池对SRAM的供电是不接连的。VCC第一次去掉后,电池就衔接到SRAM上,这个功用常称为“启封”,用于保存电池直到模块初次运用。其它时刻坚持非易失性(NV) RAM模块是单片集成电路(在一块IC中有操控器和SRAM),不需求启封。

模块封装

时刻坚持非易失性(NV) RAM,多路总线时钟,一些看门狗和隐形时钟都可用于模块或许电源帽封装。模块内部嵌入一个32.768Hz的晶振和一个锂电池,使得规划PCB变得更简单。可是,晶振和电池不能容耐再次回流期间的温度。在再次回流后,模块可以用手附上或插到座子上。只需锂电池不会露出在85℃以上温度,模块也可以用波焊的办法焊到PCB上。

电源帽产品选用两片结构来供给一种能再次回流进程的外表焊接设备。用规范的回流技能可将含有RAM和时钟的模块底部装置到电路板上。在焊接之后, 含有灵敏性电池和晶振的电源帽上部会突然折断到底部。

时钟格局

RTC用到了3种首要的数据格局,BCD格局,带月,星期,年等独自存放器的二进制格局和无格局的二进制寄数器格局。

BCD是最常用的一种格局。它盛行的一个原因是时刻和日期数据可以很便利的读取,而不必转化。每8位存放器代表两个数字(每个数字一个半位),每4位比特二进制标明数字0到9。图1显现出了一个典型二进制时钟格局图。

由于有些位在特别的时刻或日期范畴里不需求,这些位可以用于特别的功用,一般状况下是用作读/写位的,也可以用硬件读回来而总是处于1或0状况,这是由规划来决议的。在图1中,秒存放器的第7位是用作时钟中止位(CH)的。

第二种是二进制方法,各个独自的存放器和BCD格局相同。在带BCD格局的时钟上二进制格局一般是可以编程进行挑选的。

第三种是在某种参阅点的无格局二进制值中,用单个的多字节存放器来标明秒时刻。

图1.典型时刻和日期存放器图

时刻和日期存放器每秒更新一次。日期的改变值根据月和二月所在的年而不同。星期存放器除多总线时钟外,与其它存放器无关。星期存放器在午夜添加,并从7到1改变。只需在程序中的分配是接连的,程序员可以选定任何特别的一天作为“1”。在总线复用时钟中,星期天有必要是“1”,由于星期存放器用白日保存测验。在从前的午夜改变上,为白日保存的测验在午夜完成了,当测验白日保存功用时这有必要阐明。

当时钟格局由12小时格局成24小时格局,或从BCD格局变成二进制格局,或从二进制格局变成BCD格局,时刻,日期,报警存放器都有必要从头进行初始化。

无格局的二进制计数器时钟有一个独自的存放器,代表性地是32位,每秒能添加一次。一般,存放器值00H被认为是某些缺省的时刻或日期值。例如,格林尼治时刻1970年1月1号00:00:00便是“0点”。存放器中的二进制值就代表从那一点走过的时刻。软件程序有必要把32位的二进制值变成可以读写的时刻和日期,而且将用户数据转化成二进制值。

Y2K Compliance

FS半导体RTCs 与Y2K相习惯,兼容Y2K,或许是不包含对日期灵敏的逻辑。一个习惯Y2K的时钟有这些逻辑,包含世纪信息(有世纪数字或世纪位),可以正确核算闰年直到2099年,但要求体系软件对世纪进行盯梢。二进制秒时钟没有对日期灵敏的逻辑,软件有必要核算正确的日期,包含闰年的正确性。

晶振和准确度

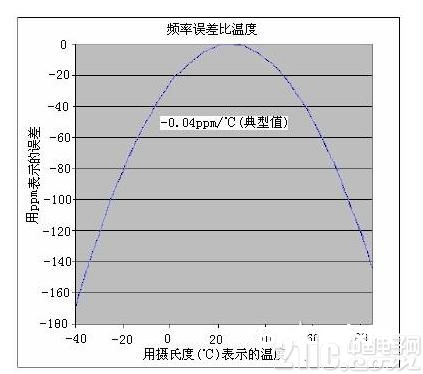

晶振是一种最准确的可以用来供给固定频率的电路。32768Hz的晶振用于大多数RTCs。经过区分晶振的输出频率,一个1HZ的参阅频率可用于更新时刻和日期。时钟的准确度首要取于晶振的准确度。调谐晶振对温度有一个抛物线呼应(图2)。23ppm的差错大约为每月一分钟。

在特别的容性负载下,晶振能调到正确的频率处振荡。在一个规划能供给6pF 电容负载的晶振的RTC中,用一个调到12.5pF的电容负载的晶振会导致RTC走得要快。

图2.晶振的准确度与温度

晶振的衔接

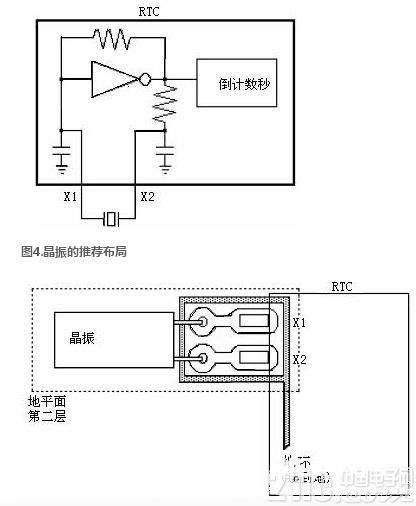

一切FS的RTCs的内部都有一个偏置网络。晶振应直接连到X1和X2的引脚上,而没其它任何元件(图3)。晶振应尽或许近的挨近X1和X2引脚。地平面应置于晶振,X1和X2下面(图4)。数字信号线应当远离晶振和晶振的引脚,有严峻辐射的RFI的元件应屏蔽起来且远离晶振。低功耗的晶振电路对邻近的RFI灵敏,RFI会引起时钟走时变快。

图3.RTC-等效电路显现其内部的偏置网络

PC板上包含了可调晶振,例如那些带RTCs,不能把超声波扫除在外。晶振或许由共振损坏。

晶振起振时刻

晶振的起振时刻在很大程度上依赖于晶振的特性和电路布局。高的串行等效电阻(ESR)和过大的电容负载是延伸发动时刻的首要因素。用含有引荐的特性的晶振和按照引荐的电路布局的电路一般能在一秒内发动晶振。

电池衔接

大多数FS的RTCs都包含一个电池输入引脚。电池是用来坚持当主电源断开后时钟可以正常走动。关于大多数规划来说,所用的电池都是钮扣锂电池。

有的RTCs用电源电压作为参阅来决议什么时候VCC是有用电平。当VCC低于最小值时,器材进入写维护,阻挠外部拜访器材。当器材作业在VCC条件下时,VBAT输入将处于高阻状况。假如电池没有衔接到VBAT上,或是衔接到串行二极管,VBAT的输入处于高电平漂浮状况,引起RTC进入写维护。在FS的大多数时钟内部都供给反充电写维护,以消除外部二极管。

读/写时刻和日期

由于在读或写的进程中可以进行内部存放器更新而没数据的损坏,大多数FS 的时钟都供给能保证拜访时刻和日期的办法。

辅佐缓冲存放器(二级缓存)也用在串行时钟上。当拜访(读)RTC时,当时时刻和日期传送到辅佐存放器。一个脉冲读信号将从辅佐存放器中读数据,在内部存放器接连更新时辅佐存放器的内容将坚持不变。 下一次拜访(当芯片有用,复位或开端)将又一次传送数据。当存放器被写时相似的进程发生,除非数据在拜访之前没有被内部存放器改写。

在时刻坚持非易失性(NV)RAM时钟上,用TE位或R和W位封存用户存放器。

有多总线时钟里。有几种办法能保证时刻和日期存放器在拜访间不变。以下办法便是:

设置位

B存放器的SET位设为1时,用户双缓存时刻和日期存放器被锁存了。内部存放器依然正常的不断更新。

UIP 标志

进程中的更新标志位(UIP)每秒将发生一个脉冲。当UIP位变为高电平后,更新将在244uS后发生。假如UIP位读出的为低电平,为避免更新时的过错用户至少有244uS的时刻可以读存放器的数据。

UF 中止

假如使能,那么在每一次更新周期之后发生一次中止,该周期标明999ms能读有用时刻和日期信息。

默许的存放器值

假如数据手册中没有特别阐明,初始上电存放器值不确认。也便是说,它们和DROM或SRAM是相同:初始上电后,用于实践的数据是随机的。

发现并处理新规划中的问题

不能和RTC通讯

在新的规划并处理问题的进程中,这里有多种办法可以协助确认发生问题的原因。例如,假如显现出来的是器材底子不通讯,常常值得去确认该器材是否没读,写或两者都没。假如器材有软件使能的特色,例如方波输出,尝试着使那个特性有用是一个很好的方法去决议是否可以写器材。在2线器材上,示波器可以确认时钟在传送每个字节后是否发送应对信号。下面的阶段描绘了一些附加的规划中的问题并处理的提示”

有备用电池的实时时钟芯片用一个比较器在VCC和VBAT之间切换。有些实时时钟芯片用电池电压作为参阅电压,别的的用一个能带参阅电压决议什么时候VCC有用。当VCC下降到比较器的触发点,就不可以进行读写。在一个电压下的阻挠读写有助于对处理器进行不注意的写,该处理器不再有有用的供给。而且,当VCC电压高于触发点,比较器把内部供电电源切换到VCC,避免电池耗尽。在电池电压为参阅的器材中,一个悬空电池输入,在电池和VBAT之间有一个二极管的输入,或有太高电压的电池能阻挠和RTC的通讯。保证VBAT在有用的电压规模内,而且在电池和电池输入引脚之间没有二极管。

串行时钟要求正确的向器材中写人指令字节或从地址。不正确的指令/地址常常导致器材忽略读操作。在那些状况下,数据I/O口终止于高阻态。在带上拉电阻的串行线上,数据重复常常是0XFF。在3线接口中,假如I/O口有内部下拉电阻,数据常常是0。在其他的状况下,数据重复常常是指令字节最终一位的值。有些串行时钟用别离的输入作输出,以便在一个较低供给电压时答应处理器和谐作业。没接有用的供给到输入端会阻挠I/O口驱动高电平。最终,假如软件不能使处理器的端口(接到了时钟的输入输出引脚)从输出(写指令节)切换到输入(读数据),那么输出的数据或许是全0或全1。

无效时刻和数据值

大多数时刻和日期存放器可以接纳任何值,包含无效值。假如无效值进入存放器,那么该值将不断添加,直到和发生翻转的位相匹配后比较,到达最小值。假如时钟处于过错的方法。也或许形成无效值,例如,二进制码替代BCD码,或12小时制替代24小时制。

数据丢掉/数据损坏

有两种状况可以引起数据丢掉:无意中的写时钟或反相小毛病脉冲电压用到IC上。由于CH或/EOSC位(带晶振操控位的时钟上)处于默许的中止状况, 反相电压输入到%&&&&&%所形成的数据丢掉有时能辨认。别的,大多数而不是一切的存放器中的数据会损坏。无意中的写一般发生在电源周期时,可是一般只影响一个存放器,而不影响串行时钟。

在上电和/或掉电时许多现代的开关电源将在VCC上发生一个-5V或-6V或乃至更大的毛刺。经过输入维护二极管,这个负电压耦合到内部时钟电源。假如电源可以供给比电池大的电流,那么数据将丢掉。在某种状况下,用一个肖特基二极管可以钳位这个负毛刺电压。别的一个时钟上的负电压源来自RS232衔接器。假如带时钟芯片的PCB板掉电,上电的PC或其他器材经过RS232衔接器衔接到那块板上,RS232收发器芯片或许将负电压传到不上电的PCB板上的其他芯片。

无意中的写也或许形成数据损坏。在写维护为有用前,在上电或掉电期间处理器能写入过错的数据。在上电和掉电时,接口电路或许迫使输入引脚进入写状况。在多总线时钟的状况下,地址信号锁存在ALE的下降沿。假如/WE和/CS在器材处于写维护之前变为低电压,那么在最终存放器中最终拜访的数据会损坏。VCC的上升时刻和下降时刻应核对无误以用于数据手册的需求。

不正确的中止程序处理形成连续的数据问题。在某些状况下,时刻和数据信息仿制到RAM中去了,而且仿制不是同步的。最终,在电路仿真(IEC)硬件装备不妥,可以形成古怪的行为。

晶振问题

时刻不能添加的最遍及原因是晶振没使能。许多FS时钟芯片有一个在晶振作业前须置1的操控位(一般坐落第二个存放器)。

为延伸电池运用时刻,振荡电路规划成低功耗。晶振的衔接问题能下降闭环增益,阻挠晶振作业。接到晶振的外部%&&&&&%也削减闭环增益,添加启振时刻或阻挠振荡。示波器的探头也可以阻挠振荡。带45K以上的等效串行电阻(ESR)的 晶振也将削减闭环增益。最终,留在电路板上的焊锡清洁剂或许阻挠晶振起振。