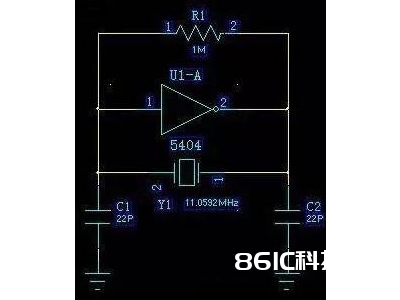

许多MCU开发者对MCU晶体两头要各接一个对地电容的做法表明不理解,因为这个电容有时能够去掉。笔者参阅了许多书本,却发现书中解说的很少,说到最多的往往是:对地电容具安稳效果或相当于负载电容等,都没有很深化地去进行理论剖析。而别的一方面,许多爱好者都直接疏忽了晶体周围的这两个电容,他们以为按参阅规划做就行了。但事实上,这是MCU的振动电路,又称“三点式电容振动电路”,如图1所示。

图1:MCU的三点式电容振动电路

其间,Y1是晶体,相当于三点式里边的电感;C1和C2是电容,而5404和R1则完成了一个NPN型三极管(我们能够对照高频书里的三点式电容振动电路)。

接下来将为我们剖析一下这个电路:首要,5404必需搭一个电阻,否则它将处于饱满截止区,而不是扩大区,因为R1相当于三极管的偏置效果,能让5404处于扩大区域并充任一个反相器,然后完成NPN三极管的效果,且NPN三极管在共发射极接法时也是一个反相器。

其次将用浅显的办法为我们解说一下这个三点式振动电路的作业原理。众所周知,一个正弦振动电路的振动条件为:体系扩大倍数大于1,这个条件较简略完成;但另一方面,还需使相位满意360°。而问题就在于这个相位:因为5404是一个反相器,因而已完成了180°移相,那么就只需C1、C2和Y1再次完成180°移相就能够了。刚好,当C1、C2和Y1构成谐振时,就能完成180移相;最简略的完成方法就是以地作为参阅,谐振的时分,因为C1、C2中经过 的电流相同,而地则在C1、C2之间,所以刚好电压相反,然后完成180移相。

再则,当C1增大时,C2端的振幅增强;当C2下降时,振幅也增强。有时即便不焊接C1、C2也能起振,但这种现象不是由不焊接C1、C2的做法形成的,而是由芯片引脚的分布电容引起,因为C1、C2的电容值原本就不需求很大,这一点很重要。

那么,这两个电容对振动安稳性到底有什么影响呢?因为5404的电压反应依托C2,假定C2过大,反应电压过低,这时振动并不安稳;假定C2过小,反应电压过高,贮存能量过少,则简略受外界搅扰,还会辐射影响外界。而C1的效果与C2的则刚好相反。在布板的时分,假定为双面板且比较厚,那么分布电容的影响则不是很大;但假定为高密度多层板时,就需求考虑分布电容,尤其是VCO之类的振动电路,更应该考虑分布%&&&&&%。

因而,那些用于工控的项目,笔者主张最好不要运用晶体振动,而是直接接一个有源的晶振。许多时分我们会选用32.768K的时钟晶体来做时钟,而不是经过单片机 的晶体分频来做时钟,其间原因想必许多人也不明白,其实上这是和晶体的安稳度有关:频率越高的晶体,Q值一般难以做高,频率安稳度也比较差;而32.768K晶体在安稳度等各方面的功能体现都不错,还构成了一个工业规范,比较简略做高。别的值得一提的是,32.768K是16 bit数据的一半,预留最高1 bit进位标志,用作守时计数器内部数字核算处理也十分便利。