1 导言

跟着数字电视及视频会议的开展以及运用,H.264由于其更高的压缩比、更好的图画质量和杰出的网络习惯性而备受重视。

根据上下文的自习惯二进制算术编码(CABAC)则作为H.264编码器体系的终究一环,对整个编码功能影响较大。CABAC充分考虑视频流的相关性.能习惯信号核算特性的改动,简单到达渐进功能,编码速度较高,但复杂度大,这形成单纯用软件编码难以到达很高的功能,特别是关于高清晰度视频(HDTV)不能完结实时编码,这就需求硬件加快或规划专门的硬件编码电路。

现在,已有相应的硬件加快电路规划面世,但首要是对算术编码部分进行规划,全体功能仍不行抱负。这儿在对以往加快电路剖析的基础上,掌握CABAC整个编码原理,首要对其间的二进制化部分进行优化,对相应的二进制化办法进行归类优化,选用并行运算的计划,终究在FPGA上以较优的速度和资源完结硬件编码。

2 二进制化原理

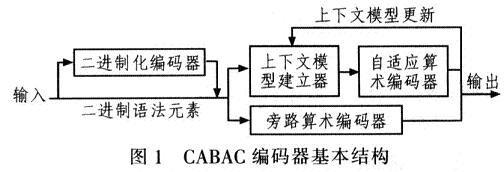

CABAC完结计划包含3个进程:语法元素的二进制化、上下文建模、自习惯算术编码,图1是CABAC编码器根本结构。

二进制化是CABAC编码的第1步,进步二进制化模块的编码速度有助于整个体系速度的进步。在二进制化进程中,一个给定的非二进制语法元素被仅有地映射到一个二进制序列(Bin String),其间的每一位称为Bin。

假如输入为给定的二进制语法元素,则此步就可以跳过,随后的过程由编码办法决议。

在H.264规范中。语法元素较多,约有20多种,而二进制转化使这些语法元素的二进制表明挨近最小冗余编码,以削减码流。

CABAC中二进制转化有4种根本类型:一元(U)编码、切断一元(TU)编码、指数哥伦布(EGK)编码和定长(FL)编码。别的,还可经过这几种编码办法的串联进行二进制化转化。

2.1 一元(U)二进制转化计划

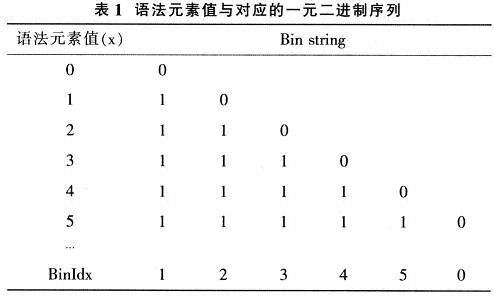

关于一个无符号语法元素x≥0,CABAC中的一元码字是由x个“1”串连并在结尾处加上“0”,因而一元二进制化的长度是x+1,如表1所示,其间Binldx表明字符串的索引。一般来讲,U二进制转化首要用于参阅帧行列猜测语法元素的编码。

2.2 切断一元(TU)二进制转化计划

切断一元二进制化对语法元素的值有要求,只对不大于某个界限值(S)的语法元素进行二进制化。若语法元素值小于S,则其二进制化成果同一元二进制化;若语法元素值等于S,则其成果为S个“1”。一般,TU二进制转化首要用于帧内色度猜测办法的编码。

2.3 指数哥伦布(EGK)二进制转化计划

EGK编码开始由Teuhola在上下文操控长度编码计划中提出,是由Golomb编码派生的。EGK编码由一个前缀和后缀码字串联构成,其前缀部分由一元码字l(x)=[log2(x/2k+1)]的值组成,其后缀部分由x+2k(1-2l(x))核算得出。一般,EGK二进制转化首要用于残差以外数据的编码,详细景象视编码器的设置而定。EGK二进制化随后取值的不同而不同,k的取值为非负整数。

2.4 固定长度(FL)二进制转化计划

固定长度二进制化适用于语法元素值x小于界限值S的状况。办法为直接用x值的二进制表明办法作为其二进制化成果,长度同定为:lFL=[log2S]的向上取值。一般,FL二进制转化被用于统一分配的语法元素,编码块的图形符号部分关系到亮度残差。

2.5 根本二进制转化的串联计划

由以上各种二进制办法可以再推导出3种根本的二进制转化计划。第1种是4位FL前缀与TU后缀(S=2)的串联,而第2和第3种计划来自TU和EGK二进制转化,称为UEGK。这些计划被用于运动矢量微分和改换系数取绝对值。别的语法元素mb_type和sub_mb_type二进制化运用遍历二叉树办法,对应的二叉树已在参阅文献中给出。

3 二进制化编码计划优化

H.264规范中的二进制化编码流程是串行的,合适软件的完结,但由于待编语法元素较多,导致履行速度慢且功率低下。而硬件完结的最大优势在于其并行性,可大大进步履行功率。因而,为进步编码速度,在不改动算法本质的前提下,对规范中的编码流程进行相应优化,以利于硬件完结。首要提出以下优化办法:

(1)将语法元素归类依照根本的编码办法及H.264对各语法元素的要求,可将20余种语法元素的二进制编码办法归为6类,包含U二进制化、UEGKO二进制化(k=0,uco-eff=14)、UEGK3二进制化(k=3,ucoeff=9)、宏块/子宏块类型二进制化、宏块量化偏移二进制化,定长与切断串联的二进制化。将语法元素归类,将有用减小编码进程中的冗杂和无序性,有利于编码正常完结。

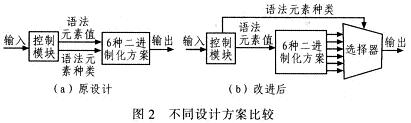

(2)并行化规划语法元素的二进制化办法可归为8类,在规划中,选用操控单元区分相应的语法元素,并送入二进制化模块进行编码。但依照H.264规范规划,二进制化单元的进口地址不只取决于语法元素的值,还取决于语法元素的品种,这种数据依存关系无疑增加了运算量。且输出是串行,不利于流水线规划,这样就将下降体系的时钟频率。故选用一种并行规划计划,以语法元素值为输入,成果得到6个不同的输出,将它们锁存后,运用多路挑选器以语法元素品种作为操控端选出所需的值。两种不同的完结办法见图2。

4 二进制化编码的FPGA完结

改善后的二进制化编码首要包含:操控单元、二进制化编码单元及挑选输出单元,如图3所示。

电路首要分为5级流水线完结。在第1级流水线中,语法元素(SE)、时钟信号(clk)、上下文模型参量(a、b)等输入数据进入操控单元。操控单元选用比较器完结,经过比较给定数值与输入数值的规模确认语法元素的品种,经过品种信号(selector)输出挑选所采纳的二进制化办法。

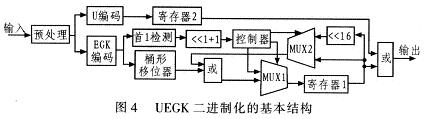

第2级流水线包含6个模块,别离代表6种二进制化办法。其间U编码、mb_type/sub_mb_type语法元素编码模块较易完结。由于输入语法元素的位宽为6位,数据量不大,别离依照其编码办法制成码表,且此码表所耗资源不多,在硬件完结时以RAM的办法完结,速度较快。关于UEGK0和UEGK3 编码模块的完结,则需选用U编码和EGK编码相结合的硬件办法完结,详细根本结构如图4所示。

图4中,首先由预处理器判别现在比特所进行的编码,在EGK编码中,首要选用首一检测及桶形移位技能完结,终究将两种编码相加输出。

关于UEGK0和UEGK3编码模块,只需选取不同阈值可完结。关于语法元素mb_qp_delta,选用有正负符号的EGK编码,正负号由语法元素值的奇偶性决议。关于语法元素coded_block_patterm,则选用FL与TU相结合的编码办法,因FL与TU编码的数据量均不大,故选用查表办法完结,这样可进步速度,其间FL编码的界限值为15,TU编码的界限值为2。

第3级流水线的首要功能是挑选。第2级输出包含已编元素(binary_value)和上下文模型参量(ctxOffset0、ctxOff-set),在第3级中,经过挑选信号(selector)对不同输出作以挑选。第4级流水线为32位先进先出(FIFO)存储器。对成果进行缓存,有利于下一级处理。

第5级为串行化器,首要对二进制化的数据进行处理,使其按位输出,并将二进制化后的每一位参加其对应的上下文模型,以便后续处理。整个体系的输出即为二进制化后的每位数据(sda)及其偏移(ctxIdxl)。

5 电路仿真及功能剖析

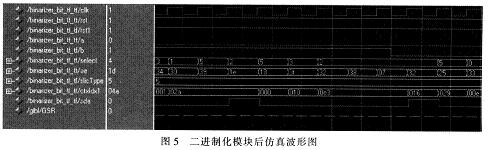

该算法经VC++仿真验证,可对H.264规范中的首要层次视频码流进行编码,其成果与H.264规范程序JM8.6相同。电路结构选用Verilog言语进行RTL级描绘,并用mod-elsim6.0软件仿真,后仿真波形如图5所示。

由图5可看出,每个周期中,在使能信号有用的状况下,在时钟的上升沿,可发生1 bit数据sda及相应的偏移量ctx-Idx1,满意规划时序要求。电路在Spartan3 FPGA上归纳、布局布线,运用Synplify丁具进行归纳,最高时钟频率为100 MHz,影响时钟频率的要害途径为先进先出存储器模块。将归纳好的edif电路网表文件输入到后端FPGA厂商Xilinx的Foundation软件进行布局布线,生成二进制流文件,逻辑单元为171,占总资源的4%。运用规划的电路对H.264规范中一些规范视频序列进行测验,序列质量为QP=28,并与H.264规范程序JM8.6中二进制化部分的编码时刻比较,成果如表2所示。

综上,本文对H.264编码器二进制化部分的优化使其在速度上较软件完结有较大提高,资源占用率也较少。二进制化部分的硬件规划不只能完结H.264规范中根本层次的编码,还有望运用于更大尺度更高质量的实时视频压缩编码。

6 定论

在对H.264规范中二进制化部分研讨和剖析的基础上,提出其FPGA电路结构,选用并行结构及流水线办法规划电路。该结构经Spartan3 FPGA完结,其吞吐量为每周期1 bit,最大时钟频率为100 MHz,可以满意H.264中第3级及其以上层次实时视频编码的要求。