8.1根据FPGA的SOPC体系组成原理和典型计划

8.1.1SoC及SOPC简介

1.SoC

SoC即SystemOnChip,是片上体系简称。它是IC规划与工艺技能水平不断提高的成果。SoC从整个体系的视点动身,把处理机制、模型算法、芯片结构、各层次电路直至器材的规划严密结合起来,在单个(或少量几个)芯片上完结整个体系的功用。所谓完好的体系一般包含中央处理器、存储器以及外围电路等。

SoC一般运用于小型的、日益杂乱的客户电子设备。例如,声响检测设备的体系芯片是在。单个芯片上为一切用户供给包含音频接纳端、模数转换器(ADC)、微处理器、必要的存储器以及输入/输出逻辑操控等设备。

SoC的规划以IP核为根底,以分层次的硬件描绘言语为体系功用和结构的首要描绘手法,借助于以计算机为渠道的EDA东西进行。

研讨标明,与IC组成的体系比较,因为SoC规划能够综兼并全盘考虑整个体系的各种情况,因此能够在相同的工艺技能条件下,完结更高功用的体系方针。SoC技能也大大促进了软硬件协同规划以及计算机体系规划自动化的开展。

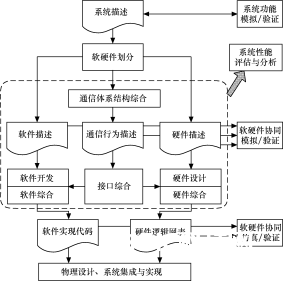

现在,在软硬件协同规划中最为活泼的研讨工作包含体系描绘、软硬件区分、软硬件协同归纳以及软硬件协同模仿与验证等。如图8.1所示为一个较为遍及的面向SoC软硬件协同规划流程。

SoC体系级规划办法根本选用层次化的规划思维和正交性的规划准则来完结体系级规划。现在,在学术界和工业界比较认可的SoC体系级规划办法学,从性质上根本可分为3大阵营:自顶向下,自底向上,上下结合和中心相遇。

图8.1软硬件协同规划流程

2.SOPC

SOPC(SystemOnaProgrammableChip:可编程芯片体系)是Altera公司提出来的一种灵敏、高效的SoC处理计划。它将处理器、存储器、I/O端口、LVDS、CDR等体系规划需求的部件,集成到一个PLD器材上,构建成一个可编程的片上体系。

它是可编程体系,具有灵敏的规划方法,可削减、可扩大、可晋级,并具有软硬件在体系可编程的功用。可编程器材内,还具有小容量高速RAM资源。因为商场上有丰厚的IPCore资源可供灵敏挑选,用户能够构成各种不同的体系,如单处理器、多处理器体系。

有些可编程器材内还能够包含部分可编程模仿电路。除了体系运用的资源外,可编程器材内还具有满足的可编程逻辑资源,用于完结其他的附加逻辑。

SOPC是PLD和ASIC技能交融的成果。集成了硬核或软核CPU、DSP、存储器、外围I/O及可编程逻辑的SOPC芯片在运用的灵敏性和价格上有极大的优势。所以,SOPC代表了半导体工业未来开展的方向。

下面介绍一下Xilinx及Altera两家公司的SOPC的处理计划,其中将要点介绍Altera的处理定案。

8.1.2Xilinx的SOPC处理计划

Xilinx公司不只供给高端32位MicroBlazeCPU软嵌入式处理器芯核,也供给免费的低端8位PicoBlazeCPU软嵌入式处理器芯核。

一般的C穿插汇编程序和用户定制的VHDL/VerilogHDL源代码,还有许多的运用阐明和参阅规划,均可从Xilinx公司网站下载取得,它们均适用于CoolRunner-I%&&&&&%PLD以及各种Spartan和VirtexFPGA系列。

Xilinx公司宣称,该CoolRunner-II版别只占用107个宏单元,而适用于Spartan-IIE的PicoBlaze则需占用76个逻辑片。适用于Virtex-II系列FPGA器材的PicoBlaze,其功用可达55MIPS。

运用MicroBlaze软处理器处理计划,Xilinx充分发挥出了嵌入式FPGA规划的悉数潜能。MicroBlaze核是一个32位哈佛RISC架构,具有丰厚的针对嵌入式运用而优化的指令集。处理器是软核,意味着它是经过运用通用逻辑基元而非FPGA中的硬专用模块来完结的。

Xilinx的Spartan和Virtex系列FPGA产品支撑MicroBlaze软处理器。MicroBlaze处理计划被规划得很灵敏,能让用户操控许多特性,如缓存巨细、接口和履行单元。为了以尽可能低的本钱点到达面向方针运用的必要功用,可装备性答应用户对巨细进行折衷来交换功用。

MicroBlaze软核被授权成为Xilinx嵌入式开发套件(EDK)的一部分。EDK是包含外围IP核库、曾荣获大奖的XilinxPlatformStudio东西套装(可用于生成直观的硬件体系)、根据Eclipse的软件开发环境、GNU编译器、调试器以及更多东西在内的完好的嵌入式开发处理计划。MicroBlaze处理器也为第三方开发东西和实时操作体系(RTOS)所支撑。

关于更高的功用要求,Xilinx在Virtex-II系列渠道FPGA中植入了32位PowerPC内核来供给DMIPS功用。合作Virtex-IIProFPGA在450MHz时钟频率下的32位PowerPC内核可供给超越680DMIPS的功用。因为处理器简化了规划,所用的芯片面积也十分小。例如,一个高效的规划仅运用了Xilinx2VP50器材中不到2%的片芯面积。