项目布景及可行性剖析

1.项目名称、项意图主要内容及现在的发展状况

项目名称:数字WCDMA体系数字频域搅扰抵消器;

项意图主要内容:用FPGA规划完结一个适用于WCDMA体系的搅扰抵消器。

现在的发展状况:有齐备的算法资源和测验数据,现已开端相关模块的完结。

2.项目关键技能及立异点的论说

立异点(1):运用频域搅扰抵消极大地降低了算法复杂度

该办法运用频域快速傅立叶改换的思路,将时域的自适应滤波进程转化到频域中来完结,然后自适应抵消输入信号中的搅扰。本发明不只有效地提取出有用信号,确保了算法的收敛性,而且与时域的搅扰抵消办法相比较,大大降低了算法复杂度。

下面临频域搅扰抵消办法和传统的时域搅扰抵消办法的算法复杂度进行比较。选用硬件完结时,核算复杂度往往决定于乘法运算的次数,因而可以比较上述两种办法的乘法个数。关于有M个滤波器抽头的时域搅扰抵消办法,由于每个数据块有M个数据,则一共需求2M2次乘法运算;而关于有M个滤波器抽头的频域搅扰抵消办法,总的乘法次数为 。那么频域搅扰抵消办法和时域搅扰抵消办法的算法复杂度比值约为

。那么频域搅扰抵消办法和时域搅扰抵消办法的算法复杂度比值约为 。因而,在滤波器抽头系数很大时,频域搅扰抵消办法的核算复杂度要远远低于时域搅扰抵消办法。

。因而,在滤波器抽头系数很大时,频域搅扰抵消办法的核算复杂度要远远低于时域搅扰抵消办法。

立异点(2):运用自适应滤波器来抵消多径信号的搅扰,功用优秀。

关于改换域和时域算法的理论比较可以参看相关文献,下面以一个仿真试验来阐明频域搅扰抵消算法的功用。将选用本发明办法在频域完结搅扰抵消的体系与没有搅扰抵消的体系功用进行比较。假定一个5MHz带宽的单载波WCDMA体系中,两个天线间信号传达时延为6微秒,且假定该两个天线之间的信道为两径式微信道,迭代步长 。但载波信号采样率为2,自适应滤波器抽头长度为64,FFT长度为128。功率放大器PA(power amplifier)为维纳模型,信干比界说为接纳天线端码片信号功率与搅扰功率的比值。以功率谱密度PSD(power spectral density)的阻带下降dB值和星座图的差错向量起伏EVM(error vector magnitude)作为功用指标进行比照。图1中的粗虚线表明信源的功率谱密度,细虚线表明有搅扰信号直接经过PA的功率谱密度,实线表明有搅扰信号经过本发明A%&&&&&%和PA处理后的功率谱密度,点划线表明没有搅扰的信号经过PA的功率谱密度。

。但载波信号采样率为2,自适应滤波器抽头长度为64,FFT长度为128。功率放大器PA(power amplifier)为维纳模型,信干比界说为接纳天线端码片信号功率与搅扰功率的比值。以功率谱密度PSD(power spectral density)的阻带下降dB值和星座图的差错向量起伏EVM(error vector magnitude)作为功用指标进行比照。图1中的粗虚线表明信源的功率谱密度,细虚线表明有搅扰信号直接经过PA的功率谱密度,实线表明有搅扰信号经过本发明A%&&&&&%和PA处理后的功率谱密度,点划线表明没有搅扰的信号经过PA的功率谱密度。

图1 频域搅扰抵消算法的功用示意图

关键技能(1):快速傅立叶改换的完结;

关键技能(2):频域搅扰抵消算法的完结。

3.技能老练性和可靠性论说

咱们已经过MATLAB仿真试验证明,该办法不只有效地提取出有用信号,而且大大降低了核算的工作量和复杂度。

VirtexII系列的FPGA有很多的存储单元和乘法器,便于完结数字信号处理功用,可以有效地完结频域搅扰抵消自适应滤波器。团队成员均有比较厚实的FPGA根底和规划功底,和信号处理方面的专业知识,彻底有才能确保该项意图顺畅施行,终究完结项目。

项目施行计划

1.计划基本功用框图及描绘

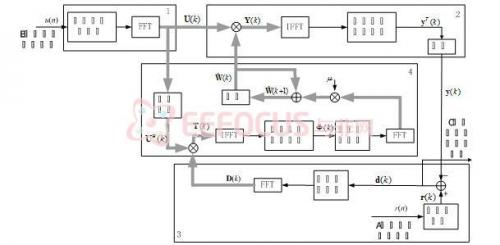

该办法依据时域中的数据块最小均方差错(Block LMS,block least mean square)核算办法和该块LMS算法中存在线性相关和线性卷积的进程,经过1/2堆叠保留法的快速傅立叶改换FFT(fast fourier transforms)在频域以直接相乘的核算方法完结快速相关和快速卷积,运用自适应滤波器在频域完结LMS算法;包含以下循环履行的操作过程:

(1)对自适应滤波器的频域抽头系数作初始化设置,并对该滤波器的时域输入信号做N点离散快速傅立叶改换FFT处理,使其转化为频域信号,用作自适应滤波器的输入信号;其间N是该滤波器的抽头个数M的2倍;

(2)将输入的频域信号经过自适应滤波器进行自适应滤波处理,并对该滤波器的输出信号进行快速傅立叶逆改换IFFT(inverse fast fourier transforms)处理,使其转化为时域信号,作为搅扰的估计值;

(3)核算被搅扰信号和滤波器输出的时域信号之间的差值,作为有用信号;再发生有用信号的频域值;

(4)运用频域信号进行最小均方差错LMS核算,即依据有用信号和滤波器输入信号的频域值对滤波器抽头系数进行更新,以便在回来履行上述过程(2)时,运用该更新后的抽头系数对来自过程(1)新的频域输入信号循环往复地持续履行相关的自适应滤波处理。

图2 计划基本功用框图

2.需求的开发渠道

所需求的开发渠道为VirtexII Board。由于用自适应滤波算法以及大点数的FFT改换需求很多的乘法器和存储器,不需求其它配套的开发东西。需求USB和EMAC接口进行终究的测验验证。

3.计划施行进程中需求开发的模块

本计划需求完结大点数的FFT改换以及相应的串并、并串转化模块,因而将规划分为7个大的模块,顶层模块,数据处理,FFT模块,串并转化模块是并串转化模块,推迟补偿模块,还有体系控制模块。

FFT模块运用Xilinx公司的IPCore来完结;串并、并串可以运用块RAM完结;数据处理模块尽可能的适用SRL16结构来完结,以节约资源;

4.体系终究要到达的功用指标

用FPGA规划一个适应于单载波的搅扰抵消器,可以抵消至少6径搅扰,满意WCDMA相关规范的要求:

需求的其它资源

1.测验设备

在计划施行进程中,需求Xilinx内嵌的逻辑剖析仪,以及与安捷伦逻辑剖析仪相配套的虚拟管脚的相关运用阐明和技能支持。

2.仿真、开发东西

在计划施行进程中,需求的仿真、开发东西有仿真东西Modelsim、开发东西ISE等。