多年来,宽同步并行总线已成为数字设备之间进行数据交换的首要技能手法。经过并行移动多个比特,这些数据总线技能如同比串行(次序)传输技能的通讯速度更快。但惋惜的是,并行总线守时同步(时滞)在时钟频率和数据传输率较高时存在严峻的问题,这显着约束了并行总线传输的速度。

此外,这一技能在支撑长距离、施行本钱和终究用户本钱方面也面对严重应战。经过比较,串行总线只发送一个比特流并具有“自时钟”机制,因而数据和时钟之间没有时序误差(即一起传输的比特抵达时刻之差)。凭借串行传输,消除了信号同步问题,并且全体功用更强。

但是,跟着技能进步,这个功用阻碍得到解决,另一个问题又呈现在人们面前。速度更快的新技能在化解此项应战的一起,也使规划更趋杂乱,并且继续改变的标准也发生了更多新的规划难题,这会阻碍产品快速上市并添加开发本钱。包含 PCI-Express、XAUI、RapidIO、USB, HDMI 和 SATA 在内的一些新的串行数据总线架构所带来的数据处理量比几年前要大好几个数量级。

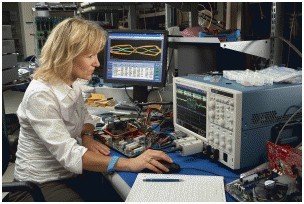

为了保证产品开发的一切阶段之间的交互操作性,标准化势在必行。抢先的技能公司现已将2.5-Gbit/s 和 3-Gbit/s的规划产品化,而5-Gbit/s 技能也行将问世,一起,10Gbs 现已用于网络通讯的规划。在如此杂乱多变的环境下,工程师极需一些测验解决方案,协助其敏捷轻松地发现和纠正规划中的问题。在此,泰克供给了齐备的串行数据测验解决方案,有助于工程师开发产品,并可以保证契合最新的串行数据测验要求。

测验高速串行数据总线

在规划进程中,工程师需求承认高速串行总线可以正确传送数据,一起串行传输问题也不会给其他体系元件带来晦气影响。最新标准具有更快的边际速率和更窄的数据脉冲,对验证、调试和测验进程提出了一些一起且严厉的要求。

跟着数千兆数据传输率在数字体系中层出不穷,信号完好性(即集成电路正确运转所具有的信号质量)也逐步成为规划人员重视的要点。数据流中一个比特的过错都会对指令或数据交换处理的成果发生巨大的影响。

或许会对传输信号质量形成危害的要素包含:

千兆信号速度:超高速传输率、低电压差分信号和多级信号传输更简略引起信号完好性问题、差分时滞、噪音和模仿搅扰的问题。因为串行总线可认为单通道架构,也可认为多通道架构以提高数据量,此刻将形成全体规划更杂乱并或许引起通道时滞守时搅扰问题。

颤动:因为较高的数据速率和嵌入的时钟的影响,现代串行设备会很简略遭到颤动的影响,颤动会发生传输过错并导致比特差错率,功用下降。颤动一般使信号违背抱负的时刻。颤动一般源自串扰、体系噪音、同步开关输出和一些其他的常见搅扰信号。

传输线影响:传输线作为电源和信号传输的中介,可所以简略的无源线路元件,如电线、电缆和芯片印刷电路板(PCB)互连。凭借串行数据技能,信号发送器、传输线和接收器一起构成了串行数据网络。而由此带来的传输效应(如反射和阻抗不接连)会严峻影响信号质量并导致传输过错。

噪音:噪音是在采样数据中呈现的任何剩余的信号。噪音来自外源(如 AC 电源线)和内源(如数字时钟、微处理器和开关电源)。噪音或许是瞬时的,或许是宽带随机噪音,但都会引起颤动和信号完好性问题。

带有嵌入式时钟的高速数字信号具有越来越像模仿体系的特征,使规划验证和体系集成面对更严峻的应战。因为信号即便在很小的失真或颤动下都或许使体系变得不稳定,这令用户在各种条件下施行准确验证、特征描绘和强度测验都要面对新的问题。

高速串行数据测验进程

受消费需求的推进,规划工程师常常需求将新功用集成到选用抢先技能的体系规划中。为了便于工程师运用,每种串行数据技能的规划和操作都会在仅有的标准文档中进行界说,该文档一般由职业委员会编写。每个标准还必需经过专业丈量和一致性测验进程,这就给现有杂乱的规划使命又添加了新的作业。这些标准针对高速数据信号传输和编码、封装、时钟嵌入、传输特点和一致性测验进程。规划人员依据清晰的高速串行技能标准和测验程序,方可以创造出具有杰出互操作性的产品。

典型的高速串行数据测验进程包含:

- 规划验证:规划和测验工程师需求验证其规划在实践的操作中是否契合规划仿真、技能指标以及具有悉数功用。这需求在实际和极限强度条件下进行全面的特征描绘、调试和剖析。

- 特征描绘:在元件的初始测验中,规划人员将描绘功用特征,然后承认信号行为是否契合标准。一般需求进行很多地准确丈量,然后承认高速总线是否作业正常。特征描绘一般包含丈量上升/下降时刻、边际到边际时刻、颤动和颤动容限、信号途径的时滞、总线树立时刻和数据途径改变。

- 排除毛病:关于任何被发现的特征描绘或操作问题,工程师都需求进行调试并查出毛病或反常条件,如硬件时刻、串扰、信号质量和/或软件规划问题等。

- 一致性测验:为保证多个供货商和产品之间可以即插即用,彼此兼容,规划师必需承认终究规划契合职业特定的串行数据标准。一致性测验是一个杂乱且比较消耗时刻的环节,并且一般需求高档测验和剖析功用。在串行标准的一致性测验标准中,一般包含起伏、守时、颤动、阻抗和眼图丈量。

一般工程师需求全面评价芯片和体系功用。在千兆赫速度下,颤动、发射器和接收器之间的阻抗不接连,或许硬件和软件之间的体系级搅扰都会引起守时问题。每个规划阶段都需求全方位的剖析东西进行更深化的调查,从而全面描绘特征并发现阻隔边际规划或体系影响。

抢先的规划、缩短产品开发周期、扩展供应链和契合特定技能标准都必需求经过优异的验证和测验东西完成。凭借先进的数据剖析才能,泰克的测验和丈量仪器是用户在开发进程前期发现规划问题,缩短串行数据产品的规划周期,加速进入市场的时刻以及降低本钱的有用手法。敬请重视下一篇博文:首要的高速串行接口技能及测验解决方案