作者/ 曾楠1 周芝梅2,3 赵东艳2,3 靳嘉桢2,3

1.国家电网公司(北京 100031)

2.北京智芯微电子科技有限公司 国家电网公司要点实验室 电力芯片规划剖析实验室(北京 100192)

3.北京智芯微电子科技有限公司 北京市电力高可靠性集成电路规划工程技能研讨中心(北京 100192)

摘要:我国自主研发的斗极卫星导航体系,日益在经济、军事和民用范畴得到越来越广的使用。本文提出并规划了依据Cortex-M3处理器的斗极接纳机基带处理芯片,规划了时域频域二维并行捕获模块,一起论述了依据Cortex-M3处理器的操控流程,包含对捕获引擎、盯梢引擎的调度,电文解谐和定位解算等。本规划最终在FPGA上完结原型验证,定位成果契合算法预期。

导言

我国斗极卫星导航体系(BeIDou Navigation Satellite System,BDS)是我国自行研发的卫星导航体系,是继美国全球定位体系(GPS)、俄罗斯格洛纳斯卫星导航体系(GLONASS)之后第三个老练的卫星导航体系。跟着2013年末我国卫星导航体系管理办公室发布斗极微信导航体系空间信号接口操控文件后,国内外连续开端推出斗极导航处理芯片。

斗极接纳机的信号处理包含三大块内容,首要是射频前端处理,对天线接纳下来的信号进行下变频和A/D转化,转成数字中频信号输入。第二部分基带处理部分对射频模块输入的中频数字信号进行数字信号处理, 首要功用是完结斗极信号的捕获和盯梢,这是整个斗极接纳模块最中心的部分。第三部分是导航定位的解算部分和人机接口,为了进步灵活性,这部分一般由CPU履行软件程序来处理。

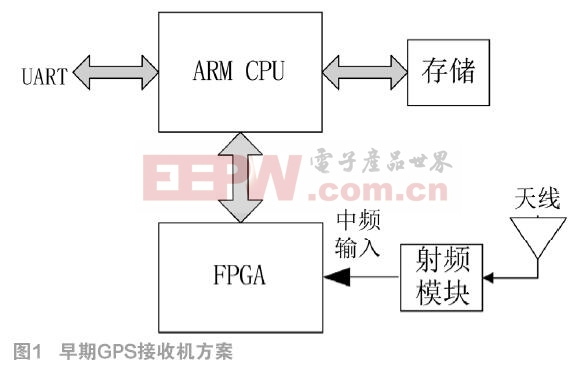

前期导航体系GPS接纳机计划多为独立射频模块衔接天线接纳GPS信号后,射频输出的中频信号输入FPGA完结的捕获盯梢协处理器,捕获盯梢后的数据再输出给一颗外接专用的ARM处理器,完结第三部分的报文接纳和定位解算,体系结构如图1所示[1-2]。

1 斗极接纳机体系

跟着嵌入式CPU的蓬勃发展,导航定位芯片的SoC规划越来越成为可能,集成了嵌入式CPU内核的接纳机芯片,完结信号的捕获盯梢后,导航报文直接由片内CPU解析并处理,完结定位解算,运算的成果数据依照NME0183格局从串口输出,一起送出1PPS秒标信号。

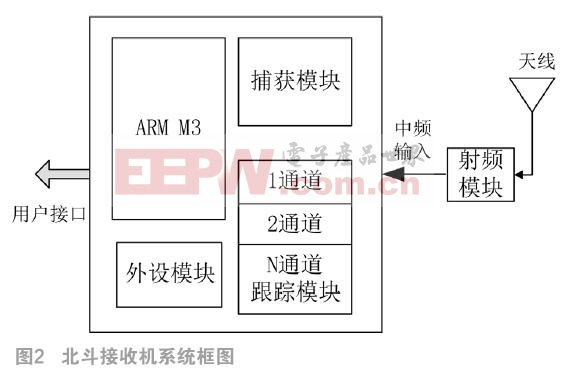

本规划的斗极接纳机体系框图如图2所示,射频模块将斗极信号接纳下来后,经曩昔载波处理和AD采样,转化为中频数字信号,输入到本规划的基带处理芯片。基带处理模块首要完结对斗极信号的捕获、盯梢处理,然后再由主处理器进行定位解算,输出解算成果。

2 斗极基带芯片硬件规划

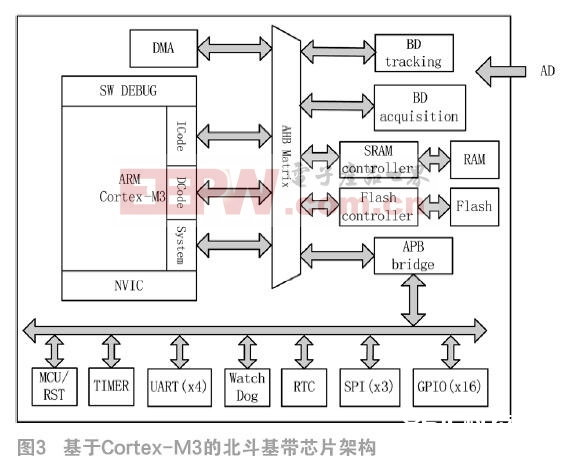

斗极接纳机基带的硬件部分首要包含了ARM Cortex-M3 CPU,担任硬件处理的操控和调度,还有斗极报文的解谐和定位解算;SoC芯片的一些根本单元包含RAM、FLASH的操控器、看门狗、TIMER、RTC以及串口/SPI/GPIO等根本通讯单元;还有基带芯片最中心的斗极基带处理部分,完结斗极信号的捕获和盯梢处理。

2.1 基带芯片体系架构

依据M3的斗极二代基带处理芯片体系架构如图3所示,选用ARM Cortex-M3嵌入式CPU, 二级AMBA总线架构;AHB总线的主设备包含CPU和DMA,从设备包含基带处理模块、SRAM操控器、SPI FLASH操控器和APB 桥。APB总线上挂的首要是低速外设,包含SPI、串口通讯模块、看门狗、TIMER、RTC和GPIO。

Cortex-M3是依据ARMv7-M架构的ARM处理器[6-7],选用哈弗架构,3级流水线规划,能用分支猜测,有单周期乘法和硬件触发功用。 Thumb2指令集结合非对齐数据存储和原子位处理等特性,能以8位、16位器材所需的存储空间完结32位功用。内置的嵌套向量中止操控器完结低推迟的中止处理,Cortex-M3处理器是寻求低成本、低功耗和高能效的使用场景抱负的CPU。M3包含三条总线,指令总线、数据总线和体系总线[8-9],与DMA共同为芯片AHB总线的主设备。

ARM CPU对盯梢和捕获模块的操控首要包含对星号、频点的设置,设置门限、捕获灵敏度和频率查找规模,依据捕获成果装备盯梢通道、载波和码频率等。

2.2 捕获盯梢模块规划

导航信号处理模块的功用,首要包含生成本地载波和C/A码,接纳输入的数字中频信号,对卫星信号进行捕获和盯梢[4-5]。

斗极信号选用直接序列扩频办法(DSSS)对调制数据进行扩频,信号的CA码速率为2.046Mbps,码长2046[3]。捕获模块接纳到数字中频信号后,与本地NCO生成的载波信号相乘,得到基带信号。基带信号经过降采样滤波器后得到4M采样率的基带信号(挨近CA码的半码片速率)。然后将此基带信号与本地生成的相同采样率的伪码,一起输入匹配滤波器组,然后完结对导航数据的解扩,这个进程叫伪码捕获。因为斗极卫星与接纳机之间具有相对速度,所以存在多谱勒频移。要得到卫星信号中的导航数据,有必要获取到卫星信号的多普勒频移的数值。这个进程叫频率捕获。所以,斗极信号的捕获是一个伪码和频率的二维捕获进程,捕获的意图便是使本地载波和接纳到的信号载波频率根本共同,而且使本地复现伪码和接纳到的卫星信号的码速率根本共同,码相位差小于一个码片宽度,然后完结本地信号与中频输入信号的粗同步。

本规划选用的是短时匹配滤波器组结合FFT的捕获结构,短时匹配滤波器将总的相干积分时刻Tcoh分红等距离的M段,每段积分时刻为Tcoh/M。短时相关结合FFT的捕获进程为:降采样至4MHz的数字中频信号进入匹配滤波器组,与本地生成的相同采样率的伪码做相关,得到M个短时相关值;一起,对输入信号进行半码片平移,然后持续相关,直到1ms后得到Mx2046个短时相关值,完结码域的全并行查找。然后对每个码相位上的M个短时相关值做FFT运算,得到其间的频域信息,完结频域的并行查找。

整个捕获功用模块如图4所示,首要包含数字下变频、载波发生器、去载波电路、降采样电路、码发生器、匹配滤波器阵列、相干/非相干累加模块和捕获引擎操控等模块。

盯梢模块的结构与捕获模块相似,仅仅依据捕获模块的粗同步信息,盯梢模块可以对卫星信号进行更精密的C/A码和频率盯梢。

3 基带芯片软件规划

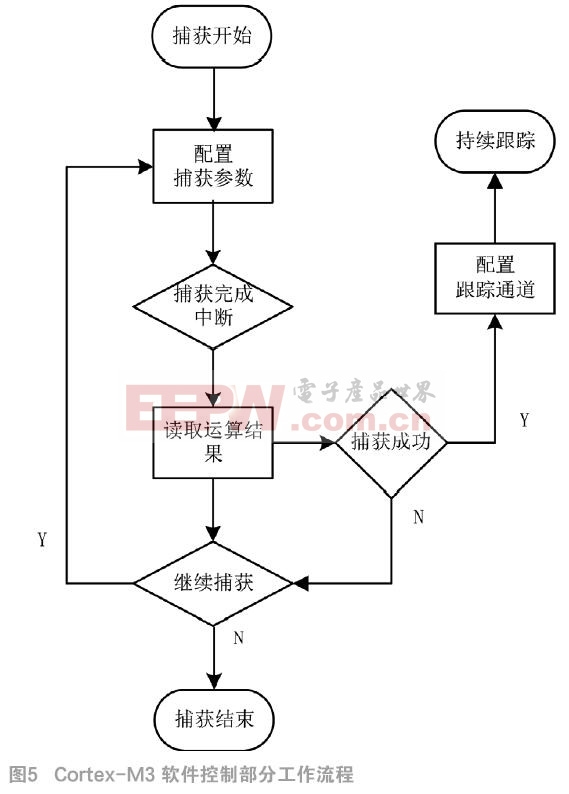

Cortex-M3 CPU作为基带芯片的主设备模块,首要完结芯片的发动和初始化,后续履行的软件依照功用首要分为两部分,一是对捕获盯梢模块的操控调度,具体工作流程如图5所示。先依据需要捕获的星号对捕获模块进行相关参数的装备,发动捕获进程;接纳到捕获完结中止后,依据捕获成果,判定是否成功捕获,并持续装备捕获下一颗卫星或许替换装备参数从头捕获本颗卫星;依据捕获成功得到的码相位和多普勒频偏值,装备相应卫星的盯梢通道,发动卫星的信号盯梢。

当盯梢通道成功盯梢4颗以上卫星后,可以对相应卫星的导航电文进行解调,然后依据取得的导航电文进行定位解算。

4 总结

本文规划的斗极基带处理芯片,内嵌ARM Cortex-M3 CPU,集成了斗极的捕获模块和16路斗极盯梢模块。经过ARM CPU的软件调度,本规划完结导航信号的捕获和盯梢,并由M3完结报文的解谐和定位解算,最终经过串口输出定位信息。该规划最终在Xilinx FPGA Kintex-7系列xc7k325t上完结原型测验,对斗极B1信号完结了成功捕获和盯梢,定位精度也能契合使用需求。

参考文献:

[1]邢增强,李金海,梁华庆,等.依据ARM+FPGA的GPS接纳机规划[J].传感器与微体系,2011.

[2]刘竞超,邓中亮.依据ARM+FPGA斗极接纳机规划[J].软件,2012.

[3]我国卫星导航体系管理办公室.斗极卫星导航体系空间信号接口操控文件

[4]李金海.高动态GPS接纳机基带算法研讨与规划[D].北京:我国科学院研讨生院,2007.

[5]廉保旺,刘慧红,毛得明.依据匹配滤波器和FFT的伪码快速捕获办法及功用剖析[J].测控技能,2009.

[6]ARMv7-M Architecture Reference Manual ARM Limited.

[7]ARMv7-M Cortex-M3 User Guide Reference Material ARM Limited.

[8]Cortex-M3 Technical Reference Manual ARM Limited.

[9]Cortex-M3 Integration and Implementation Manual ARM Limited.

本文来源于我国科技期刊《电子产品世界》2016年第10期第59页,欢迎您写论文时引证,并注明出处。