摘要:为了便利对1553B设备进行测验,介绍了一种根据ARM9渠道和FPGA的1553B总线测验体系的规划与完结办法。该体系以LPC3250作为微处理器,以CYCLONE I系列的EP1C6Q240C8芯片完结ARM与1553B协议芯片的接口逻辑。在Linux操作体系2.6群讼率迪1553B的驱动程序。15 53B协议芯片选用BU-64843T8,以完结体系的便携性。

跟着航空电子体系的开展,多路数据传输数据总线在航空电子体系中起着越来越重要的效果,其首要特色是集中操控、实时性要求高、散布处理。1553B总线以其具有较高的牢靠性和灵活性,广泛运用于军事、航空航天体系。传统的1553B测验设备选用一般计算机或工控机作为测验渠道,通过PCI总线与被测设备通讯,这对测验设备的带着形成极大不便利。本文所论述的测验体系以ARM9作为中央处理器,以DDC的BU-64843T7作为1553B协议芯片,然后完结体系的小型化和便携化,运用FPGA完结ARM时序与1553B时序的转化,并选用Linux操作体系以保证体系安稳牢靠。

1 ARM与FPGA数据通讯接口规划

1. 1 体系硬件介绍

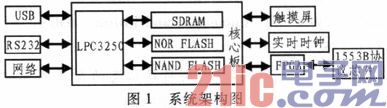

该体系硬件由LPC3250中心板、外扩接口电路、FPGA和1553B协议芯片组成组成。体系架构如图1所示。

LPC3250微处理器面向低功耗、高性能的运用,选用ARM926EJ-S CPU内核,完结5级流水处理并选用哈佛结构,可作业在266 MHz的频率下,数据处理才能强壮。

本体系外扩USB、RS232和网络接口,用于操作体系的烧写和驱动程序、运用程序的调试,而且装备实时时钟,可以掉电坚持。为添加其牢靠性,本体系在多处添加ESD芯片,以增强体系的抗静电才能。

FPGA选用Altera公司的Cyclone I系列的EP1C6Q240C8芯片,该系列芯片具有20 060个逻辑单元以及288 kb RAM,支撑3.3V LVTTL/CM OS IO规范,可直接与ARM通讯,无需进行电平转化。

1553B协议芯片挑选DDC公司的BU-64843T8芯片。该芯片是世界上第一个将1553B协议芯片和阻隔变压器集成到一体的芯片。因而,在布PCB时,会节约很大空间,然后使体系细巧,便利带着。

1.2 接口电路规划

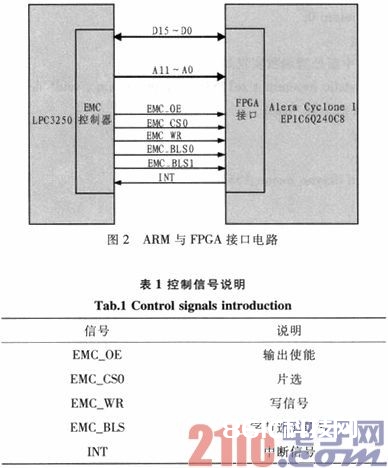

LPC3250包含3个外部存储器接口,别离是NAND Flash操控器、Secure Digital操控器和外部存储器操控器(External memory controll er,简称为EMC)。EMC供给了体系总线与片外存储设备之间的接口功用,可完结与SDRAM、DDR SDRAM和SRAM设备的通讯。该体系选用EMC的静态RAM接口与FPGA进行通讯,该接口具有时序操作简略,接口速度快等特色。运用FPGA模仿静态RAM,并进行时序转化,然后完结ARM对1553B芯片的拜访。图2为ARM与FPGA的接口电路图,因为1553B芯片内部RAM为4K*16bit,因而数据线选用16位,地址线选用12位。通过EMC静态存储器操控器的装备寄存器,可将数据总线别离设置为8位、16位、32位。该体系需将装备寄存器的低两位设置为01,即16位总线。其他操控信号阐明见表1所示。

1. 3 FPGA逻辑规划

若想成功拜访1553B设备,有必要严厉依照1553B时序进行操作,但是EMC的时序与1553B的时序差异很大,因而需求进行时序转化,这通过一片FPGA来完结。BU-64843T8的操控信号首要包含,TRANSPARENT/BUFFERED*、STRBD*、SELECT*、RD/WR*、MEM/REG*、IOEN*、READYD*、ADDR_LAT/MEMOE*.RT_AD_LAT*,INT*等信号。

TRANSPARENT/BUFFERED*信号用于设定芯片作业在通明形式仍是缓冲形式,该体系的1553B不需外扩存储器,作业在缓冲形式下即可,因而MEMOE*等信号可以不做考虑;STRBD*和SELECT*可接到一同,作为芯片的片选信号;RD/WR*为读写信号;MEM/REG*用来区别拜访内部4K存储器资源仍是寄存器资源;IOEN*有用时,标志芯片正在处理外部的拜访;READYD*信号在本体系中十分重要,当ARM写时,READYD*有用表明数据成功写入芯片中,当ARM读时,READYD*有用表明数据线上的数据有用,可以运用;ADDR_LAT为地址锁存信号,关于总线未复用的处理器,该信号置为高;RT_AD_LAT*信号为RT地址锁存信号,该信号呈现上升沿,即可将RT地址上的数据锁存到芯片内部,因而RT地址无需一向坚持着。INT*信号用于中止ARM,该信号通过FPGA与ARM的GPIO引脚相连,相应的GPIO引脚被装备为外部中止引脚。

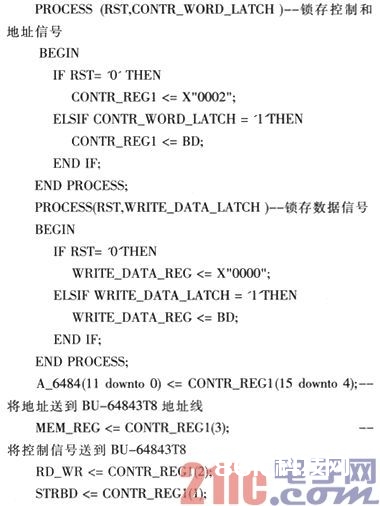

FPCA的逻辑规划选用锁存的方法,即一切的地址信号、数据信号、读写、片选、EME/REG*信号通过锁存器直接打到总线上,这些信号在ARM拜访期间一向有用。因而ARM需求进行屡次写操作:先把要写的数据送出,再把要拜访的地址和操控信息送出,之后循环读取READYD*信号,直到其有用,再进行下一次读写操作。相关的VHDL代码如下:

2 1553B驱动程序的开发原理与完结

2.1 文件操作接口

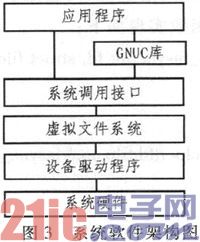

设备驱动程序在Linux内核中扮演着特别的人物。它们是独立的模块,使某个特定的硬件呼应一个界说杰出的内部编程接口,用户的操作通过一组规范化的调用履行,而这些调用独立于特定的驱动程序。将这些调用映射到效果于实践硬件的设备特有操作上,则是设备驱动程序的使命。体系软件架构如图3所示。

Linux驱动程序支撑3种类型的设备:字符设备、块设备和网络设备。字符设备是个可以像字节省相同被拜访的设备。字符设备驱动程序一般要完结open、close、read、write体系调用。本体系的1553B设备归于字符设备,它的驱动程序首要包含以下几个模块:初始化模块、翻开封闭模块、读写模块、中止处理模块。

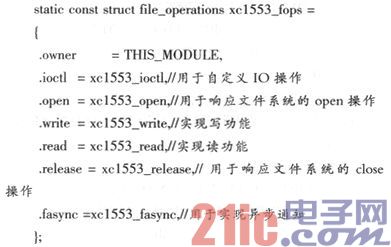

驱动程序与运用程序的通讯首要通过体系函数调用,Linux为一切设备文件供给一致的操作函数接口,咱们的驱动程序中只需完结struct file_operations中相应的函数即可,首要包含ioctl、read、write、open、release、fasync函数。详细C言语代码如下所示:

当用户加载驱动模块时,一系列初始化作业在static int_init xc1553_init(void)函数中完结,包含设备注册,物理地址到虚拟地址的映射,EMC形式的装备,中止处理函数的注册。

当用户卸载驱动模块时,需求在static void_exitxc1553_exit(void)函数中进行驱动模块和设备的卸载,以及中止号的开释。

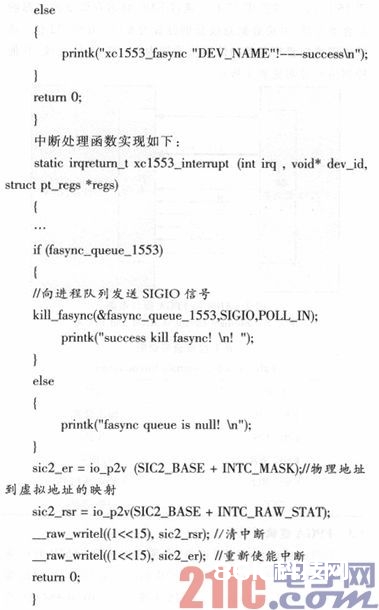

2.2 中止处理模块的完结

当1553B发生中止时,由xc1553_init函数中注册的中止处理函数进行处理,而且告诉上层运用程序进行读写操作。驱动程序与运用程序的通讯通过异步告诉的方法完结。为了完结异步告诉,在驱动程序中需求完结int fasync_helper(int fd,struct file*filp,int mode,stru ct fasync_struct**fa)和voidkill_fasync(struct fasync_struct**fa,int sig,int band)函数。

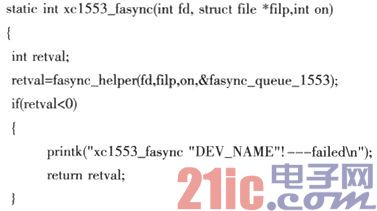

fasync_helper函数在xc1553_fasync中完结,效果是为当时进程创立一个fasync_struct结构体,然后挂入方针设备的fasync行列,最终在设备驱动的中止处理程序中,运用kill_fasync函数向该行列发送信号,告诉上层运用程序。

xc1553_fasync函数完结如下:

3 结束语

1553B总线广泛运用于航空范畴,根据1553B总线的测控设备遍及体积大,带着不便利利,本文所论述的测验体系彻底可以完结传统测控设备的功用,而且极大的缩小了设备的体积,便利带着。通过测验,该体系实时性高、作业安稳,可以满意军工要求。