介绍一种依据ARM的高精度多路同步的数据收集与输出操控体系的规划办法。规划选用德州仪器公司出产的AD芯片ADS8556和DA芯片 DAC8574,别离选用SPI接口和IIC接口与ARM9芯片S3C2440衔接,说明其硬件规划与软件规划办法。体系可完成多路且同步、高速高精度的数据收集与输出操控功用。

ARM处理器是一种32位精简指令集RISC微处理器,片内集成了丰厚的硬件资源,广泛的运用于许多嵌入式体系中。S3C2440是一款依据ARM920T内核的32位RISC嵌入式处理器,运转主频可达400MHz。本文论述选用S3C2440处理器规划的一种同步、高速、高精度、多通道的数据收集与信号输出体系的规划办法。

1 多路同步A/D规划

1.1 ADS8556的功用

体系选用TI公司出产的16位6路同步逐次迫临型模数转化芯片ADS8556。输入模仿信号电压规模为-12V~+12V。惯例运用下功耗为 251.7mW,最大功耗为298.5mW,信噪比可达91.5dB。ADS8556芯片内部包含6个独立的采样坚持模块和对应的6个独立的模数转化模块,可完成对6路信号的一起同步的模数转化。ADS8556作业形式分为硬件形式和软件形式,本规划选用硬件形式。在硬件形式下ADS8556的功用设置 (如每对通道的转化使能、参阅电压挑选等)都是经过对相关引脚设置凹凸电平完成的。ADS8556支撑并行和串行接口方法,本规划选用串行SPI接口与 S3C2440衔接。选用串行接口的长处是节省S3C2440的引脚资源,S3C2440绝大多数引脚是功用复用的,若选用并行接口会占用其16个I/O 引脚资源。

ADS8556具有3个串行数据输出端口SDO_A、SDO_B、SDO_C,转化成果经过端口使能可挑选这3个串行端口中的1个、2个或3个作业。当3个端口都选用作业时,每个串行端口上输出对应2路每路16位共32位的转化成果,输出时刻需求32个时钟周期,每路最大采样率可达450kS/s。当挑选2个串行端口时,每个端口输出3路共48位转化成果,输出时刻需求48个时钟周期,每路最大采样率可达375kS/s。因为 S3C2440只要2个SPI串行接口,所以至多挑选ADS8556的2个串行输出端口与其衔接。

1.2 ADS8556与S3C2440接口电路规划

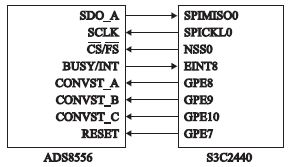

本规划选用ADS8556的1个SPI 串行输出端口SDO_A与S3C2440的1个SPI接口SPI0衔接,SDO_A端口输出悉数6路共96位转化成果,输出时刻需求96个时钟周期,每路最大采样率可达250kS/s。SPI串口以主从方法作业,S3C2440作为主机,ADS8556作为从机,需求4根或3根线衔接,3根用于单向传输,4根衔接线别离是MOSI(主机输出/从机输入),MISO(主机输入/从机输出),SCLK(时钟信号),CS(片选使能),衔接方法如图1所示。其间SPI0接口只用了3根衔接线SPIMISO0、SPICLK0和NSS0,未运用SPIMOSI0,这是因为本规划挑选ADS8556作业于硬件形式,S3C2440没有给ADS8556输入数据,其功用的设置(如每对通道的转化使能、参阅电压挑选等)都是经过对相关使能引脚设置凹凸电平完成的。若在软件形式下,这些功用的挑选是由S3C2440经过SPIMOSI对ADS8556内部相应寄存器进行赋值完成的,此刻其相关使能引脚均接地。

图1 ADS8556与S3C2440接口衔接示意图

1.3 ADS8556的接口程序规划

S3C2440作为主机,ADS8556作为从机,程序中要对S3C2440的SPI串行端口进行初始化设置,表1所示为相关引脚装备。

表1 ADS8556与S3C2440的接口引脚装备

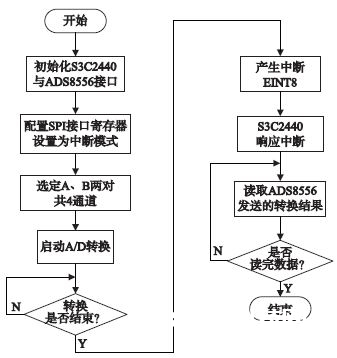

图2所示为ADS8556的采样程序流程图。S3C2440的SPI接口作业于主形式,数据传输选用中止形式。本规划只运用了ADS8556的6路转化通道中的4个通道。

图2 ADS8556作业程序流程图

2 多路同步D/A规划

2.1 DAC8574的功用

DAC8574是带有IIC接口的16位4路同步数模转化芯片。DAC8574带有一个IIC串行接口,包含SCL串行时钟输入和SDA串行数据输入两个引脚。输出四路模仿电压为VOUTA、VOUTB、VOUTC、VOUTD,电压规模为+2.7~+5.5V。由外部供给参阅电压VREFH、 VREFL。A0、A1为IIC地址挑选,A2、A3为扩展地址挑选,A1、A0、A3、A2共可承认16个地址,在IIC总线上最多可扩展16个 DAC8574。本规划在IIC总线上只运用一个DAC8574,则设置地址A1A0A3A2=0000。LDAC为同步输出电压更新。

DAC8574有三种作业形式:规范形式、快速形式、高速形式。规范形式时传输速率为100kbit/s,串行时钟频率fscl=100kHz,更新率为5.3kS/s;快速形式时传输速率为400kbit/s,fscl=400kHz,更新率为22.22kS/s;高速形式时传输速率为3.4Mbit /s,fscl=3.4MHz,更新率为188.88kS/s。规范形式和快速形式传输线协议根本相同,高速形式不同于规范和快速形式。DAC8574与 S3C2440经过IIC总线衔接时,DAC8574作为从机,S3C2440作为主机。本规划将DAC8574设置为高速形式。

2.2 DAC8574与S3C2440接口电路规划

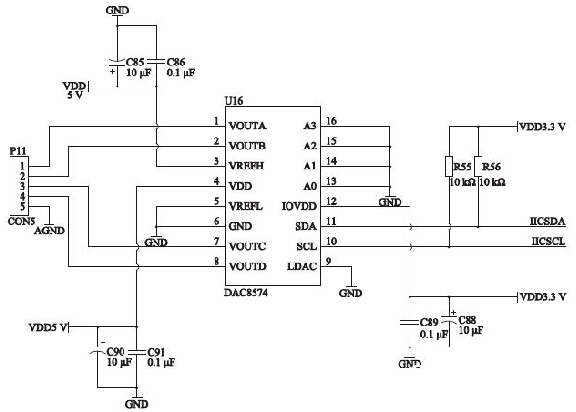

DAC8574经过I%&&&&&%接口SDA、SCL引脚与S3C2440衔接,其作业形式挑选、通道使能、LDAC功用是由S3C2440经过SDA输入设定的。如图3所示,电源电压+5V,参阅电压+5V,IOVDD为+3.3V、LDAC接地。

图3 DAC8574接口电路

2.3 DAC8574的接口程序规划

DAC8574作为从机,S3C2440作为主机,依据高速形式传输协议编写DAC8574的接口程序。图4所示为规划的DAC8574接口程序的流程图。主机先发生一个开端状况,随后发生高速主机编码的串行数据00001XXX。从机设备不需求承认高速主机编码,但有必要能够辨认并改动本身内部设置以支撑3.4Mbit/s的高速传输。主机发生一个重复开端状况,接着发送一个有用的从机地址字节,本规划的从机地址字节为10011000,包含7位 DAC8574的地址1001100和1位读写操控位0(主机写入从机)。地址匹配的从机辨认地址后发生承认信号。本规划将操控字节设置为 00010000,主机发送操控字节设置从机运转形式后,从机发生承认信号。随后,主机发送数据最高有用位MSB,从机发生承认信号,主机再发送数据最低有用位LSB,从机发生承认信号并开端数据更新,这样DAC8574就完成了一次数据接纳与数模转化。之后主机能够持续向从机发送数据,最终主机发生中止状况完毕当时的数据传输。