(来历:微计算机信息,作者:魏军辉,王福源,周子昂,侯维岩 )

键盘作为嵌入式体系的一种最常用人机接口设备,在嵌入式体系中有着适当广泛的运用。但开发者一般均选用自行规划的简易矩阵键盘,这类键盘仅仅是按行、列摆放起来的矩阵开关,往往需求独自规划并制造,通用性不强。当需求较多的按键时,则会占用较多的 I/O端口,在软件上则要进行上电复位按键扫描及通讯处理,并且还要加上按键的去颤动处理,增大了体系的软硬件开支。而 PS/2键盘,内嵌主动去除按键颤动的规划,主动地辨认键的按下与开释,软硬件可发简洁,价格便宜,安稳牢靠,将 PS/2键盘作为嵌入式体系的输入设备已经成为可行的计划。而现在关于 PS/2键盘操控的运用大部分选用单片机操控,与单片机比较,FPGA具有比单片机愈加灵敏,集成度更高,简略移植等特色。

本文在剖析 PS/2协议和 PS/2键盘作业原理与特色的基础上,给出了在 ALTERA FLEX10K上对 PS/2键盘接口的完成办法。

1 PS/2接口协议

1.1 PS/2物理特性

PS/2设备接口用于许多现代的鼠标和键盘,它开端由 IBM开发,最常见的为 6脚 mini-DIN,其引脚结构和外形如图 1 所示。

PS/2设备有主从之分,现在广泛运用的 PS/2键盘鼠标均作业在从设备办法下。 PS/2接口的时钟与数据线都是集电极开路结构,有必要外接上拉电阻,一般上拉电阻设置在主设备中,主从设备之间的数据通讯选用双向同步办法传输,时钟信号一般由从设备发生。

1.2数据包的结构键盘的状况每改动一次,键盘至少会宣布三个字节的数据包,在有键按下时会向主机发送该键的通码(Make Code),当键开释时发送断码( Break Code)。例如:键“ A”的通码为 0x1C,键“A”的断码为: 0xF0, 0x1C,因而当要传送键“ A”时,键盘发送的数据包的代码是:0x1C,0xF0, 0x1C。

1.3接口的时序逻辑

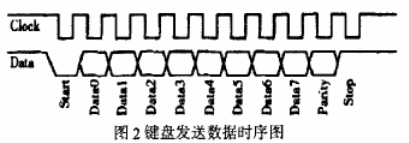

PS/2协议是一种双向半双工串行通讯协议,时钟信号由键盘发生,最大时钟频率为 33kHz,引荐频率在 15kHz。通讯两头经过 Clock同步,经过 Data 交流数据,任何一方假如想制止另一方通讯时,只需将 Clock拉到低电平。其传输时序依据传输的方向不同分为发送和接纳两个不一起序逻辑,图 2是从键盘到主机的时序图。

其间:Start:开端位,总为‘0’(低电平)

Data0~Data7:8位数据位(低位在前,高位在后)

Parity:奇偶校验位(为奇校验)

Stop:中止位,总为‘ 1’(高电平)

当键盘要向主机通讯时,键盘总是首要查看时钟线是否为高电平,假如不是则标明是主机正在通讯,有必要缓冲要发送的数据直到从头取得总线的操控权(键盘有 16个字节的缓冲区),即比及时钟线是高电平才干发送数据。并且从键盘到主机的数据只能在时钟的下降沿时才干被读取。

当主机到键盘进行通讯时,主机会首要把时钟线和数据线设置为“恳求发送”状况。详细办法为:首要下拉时钟线至少 100μs来按捺通讯,然后下拉数据线“恳求发送”,最终开释时钟。在此进程中,键盘在不超越 10μs的距离内就会查看这个状况。当键盘查看到这个状况时,就开端发生时钟。和键盘发送的数据读取办法不一样,主机发送的数据有必要在时钟的上升沿读取。

2 PS/2接口的规划完成

2.1逻辑仿真

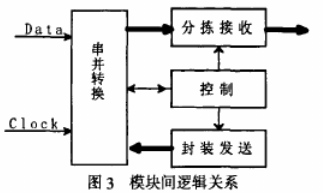

本次规划选用了自上而下的模块规划办法,考虑需求规划以下几部分模块:串并转化模块,分拣接纳模块,操控模块,封装发送模块等。这几部分的逻辑关系如图 3所示:

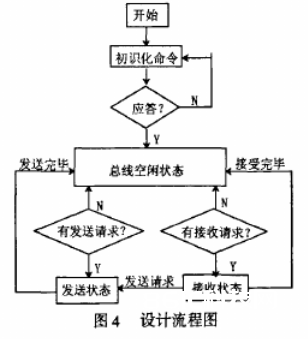

串并转化模块主要是接纳和发送传输数据,能够把串行数据转变成所需求的并行数据。分拣接纳模块功用是把串并转化模块传过来的数据包依照必定的要求进行分拣提取,然后得到有用的信息。操控模块是规划的中心, PS/2接口是半双工串行总线,因而其发送和接纳不能一起进行,需求操控模块对其时序进行严厉的操控。操控模块担任和谐整个规划的全进程,在本规划中选用了状况机的规划思路。封装发送模块和分拣接纳模块相似,只不过是把要传送的指令数据转变成 PS/2协议要求的发送数据包的格局。整个规划的流程图如图 4 所示:

当体系上电或复位时,主设备首要向键盘发送初始化信号,在得到键盘的应对信号后,体系进入到了总线闲暇状况,能够进行数据的发送和接纳,但主设备具有更高的优先级,正处在接纳状况时假如得到发送恳求,会中止数据接纳,直接进入数据发送状况。

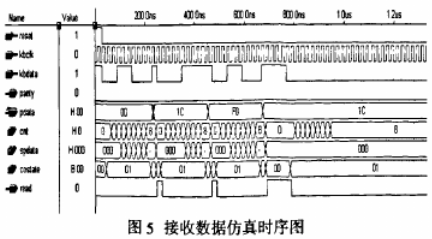

运用 MAX+plusⅡ 10.2对规划进行了软件仿真,依照模块化的规划思路分别对每个模块独立进行了仿真。图 5是接纳数据模块的仿真时序图。

2.2 硬件验证

硬件验证在 GW-48试验箱完成,在体系中用到复位电路,电源电路,FPGA芯片,程序下载电路,PS/2接口电路,数码显现电路等。

选取 FLEX10K系列 EPF10K10LC84-3 型 FPGA器材进行归纳,将归纳后的配置文件下载到开发板之后,体系上电,PS/2设备初始化后在试验箱正确调查到了键盘的输入。

3、结束语

FPGA的硬件验证标明,规划的各个模块成功地完成了复位后的数据传送进程,达到了预期的方针。VHDL言语的通用性决议了其具有移植性强的特色,对实践的运用具有必定的参考价值。

本文作者立异点:本文所作的研讨是在使用单片机完成 PS/2接口的基础上,从头用 FPGA完成了对 PS/2接口的操控。该办法较传统的单片机完成办法具有完成简略,移植性强,便于集成等特色,该办法具有很好的推行价值。

责任编辑:gt