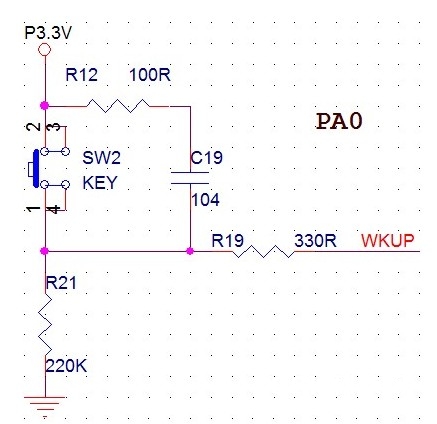

曾经GPIO上接的电路都是低电平触发的那种,新画了个板子有一个按键规划的是高电平触发,成果IO口设置成上拉输入后,怎样读都不正确,按键电路如图1。无法只能去调试一下,发现当设置为上拉输入后,其ODR(GPIO输出数据寄存器)相应的也置为1,百思不得其解。

图1 按键电路

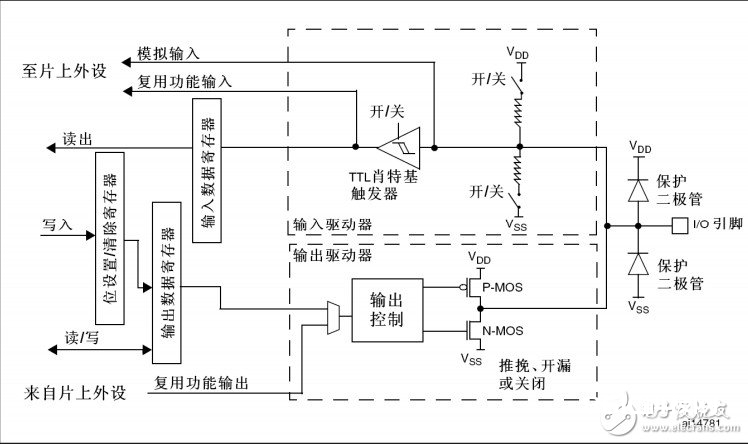

所以去看一下GPIO的结构图:

由图能够发现其实输出寄存器与输入寄存器之间在I/O引脚处是线与状况,在GPIO设置成上位输入时,其上拉电阻闭合,这时假如输出寄存器设置为0那么在IO口内部就会自己损耗电流,而这些电流的损耗是会添加功耗的。因而当GPIO设置成上拉输入时,相应的输出寄存器也设置为1.

将按键电路与I/O引脚结构图连起来看,就明晰多了,当GPIO设置为上位输入时,上拉电阻与按键的330欧、220K欧串联,这时IO口所读到的电平便是330欧与220K欧电阻分压的总合,因为这两个电阻阻值过大,因引读出的电压大于逻辑‘1’的阀值。OK问题找到了,所以将IO设置成下拉输入,问题就处理了。因而这儿得出一个定论,IO口是上拉仍是下拉要根据,IO口外部接的闲暇电平有关,如按键不按下时是低电平,则应该设置为下拉输入。

在调试时还发现另一种方法能够让代码正常运转,便是当设置上拉输入时,将其输出值设置为0,这样电平就被直接拉低了,按键的接地电路根本就不起作用了,但这样做有一个害处,前面现已说过了,这种状况会导致上拉电阻直接接地了,添加了不必要功耗,并且将3.3V电压直接加在了输出驱动器的N-MOS上,时刻长了之后可能会形成芯片损坏!