异或门的逻辑功能

异或门(XOR gate)是数字逻辑电路中常用的一种逻辑门。它的作用是对两个输入信号进行逻辑运算,输出一个结果。

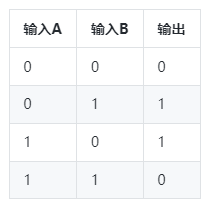

异或门的真值表如下:

异或门的逻辑运算规则为:如果输入的两个信号不相同,则输出为1;如果输入的两个信号相同,则输出为0。

异或门可以使用不同的逻辑元件来实现,最常见的是使用电子元件,如晶体管或集成电路中的逻辑门芯片。在数字电路设计中,异或门被广泛应用于数值计算、电信号处理、编码解码等领域。

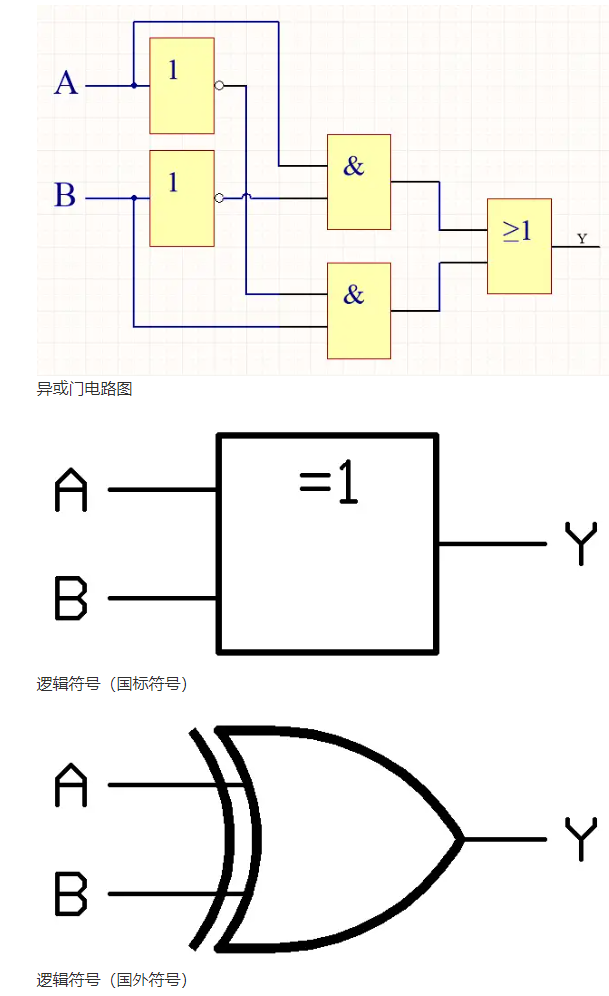

异或门的符号表示是一个带有一个加号和一个圆圈的箭头,如 ⊕。在电路图中,我们常常用逻辑门符号表示异或门。

异或门的特点是在输入的信号中只有一个为高电平(1)时,输出才为高电平;当输入的信号全为低电平(0)或全为高电平(1)时,输出为低电平(0)。这种特性使得异或门在实际应用中能够实现诸如二进制加法器、校验和计算、数据传输等功能。

异或门是由哪些逻辑电路组成

异或门可以由几种简单的逻辑门组成,其中最常见的是使用与门(AND gate)、非门(NOT gate)和或门(OR gate)。

一种常见的实现异或门的方式是使用两个与门、一个或门和一个非门。基于这种实现方式,可以按照以下步骤进行构建:

1. 将输入信号 A 和 B 分别连接到两个 AND 门的输入端。

2. 将输入信号 A 和 B 分别连接到一个 OR 门的输入端。

3. 将两个 AND 门的输出信号分别连接到一个 OR 门的输入端。

4. 将 OR 门的输出信号连接到一个非门。

这样构建的电路就是一个异或门,它可以根据输入信号 A 和 B 的逻辑关系输出相应的结果。

还有其他一些电路设计可以实现异或门,如使用 NAND 门和 NOR 门的组合,或者使用仅含有异或门的专用集成电路等。这些实现方式在逻辑功能上等效,只是使用不同的逻辑门组合。选择哪种方式取决于具体的电路设计和应用需求。