与门真值表

与门(英语:AND gate)又称“与电路”、逻辑“积”、逻辑“与”电路。是履行“与”运算的根本逻辑门电路。有多个输入端,一个输出端。当一切的输入一起为高电平(逻辑1)时,输出才为高电平,不然输出为低电平(逻辑0)。

根本功能及真值表

与门是完成逻辑“乘”运算的电路,有两个以上输入端,一个输出端(一般电路都只要一个输出端,ECL电路则有二个输出端)。只要当一切输入端都是高电平(逻辑“1”)时,该电路输出才是高电平(逻辑“1”),不然输出为低电平(逻辑“0”)。[1] 其二输入与门的数学逻辑表达式:Y = AB,对应的真值表如下

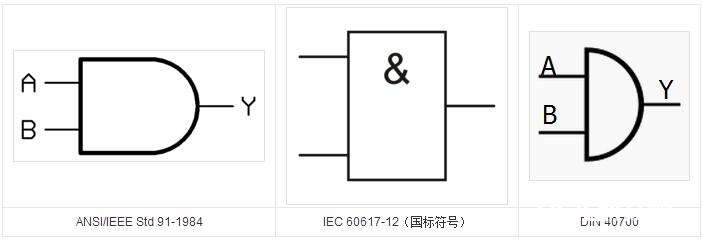

逻辑符号

与门有3种逻辑符号,包括:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)、DIN符号(DIN 40700)。

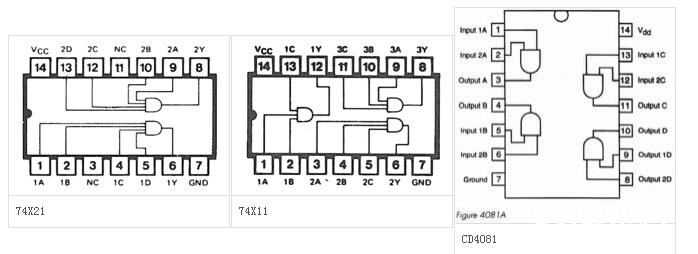

集成电路

与门是根本的逻辑门,因此在TTL和CMOS集成电路中都是能够运用的。规范的74系列CMOS集成电路有74X08、74X09(OC),包括四个独立的2输入与门;74X11,包括三个独立的3输入与门;74X21,包括两个独立的4输入与门。CD4000系列集成电路有:CD4081,包括四个2输入端与门;CD4082,包括两个4输入端与门。

引脚分配如下:

与非门真值表

与非门是与门和非门的结合,先进行与运算,再进行非运算。与非运算输入要求有两个,假如输入都用0和1表明的话,那么与运算的成果便是这两个数的乘积。如1和1(两头都有信号),则输出为0;1和0,则输出为1;0和0,则输出为1。与非门的成果便是对两个输入信号先进行与运算,再对此与运算成果进行非运算的成果。简单说,与非与非,便是先与后非。

电工学里一种根本逻辑电路,是与门和非门的叠加,有两个输入和一个输出。

CMOS电路中的逻辑门有非门、与门、与非门、或非门、或门、异或门、异或非门,施密特触发门、缓冲器、驱动器等。

与非门则是当输入端中有1个或1个以上是低电平时,输出为高电平;只要一切输入是高电平时,输出才是低电平。与非门芯片:74ls系列:74ls00、74LS20,CMOS系列:CD4011

与非门真值表

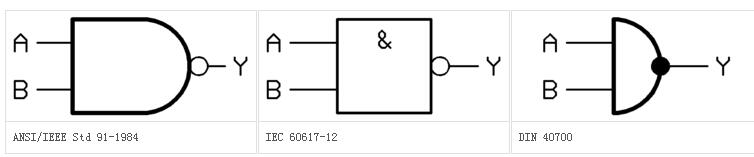

逻辑符号

与门真值表和与非门真值表的差异

与门真值表:有0出0,全1出1

与非门真值表:有0出1,全1出0