FPGA是英文Field Programmable Gate Array 的缩写,即现场可编程门阵列。FPGA利用它的现场可编程特性,将本来的电路板级产品集成为芯片级产品,缩小体积,缩短体系研发周期,便利体系升级,具有容量大、逻辑功用强,进步体系的稳定性的一起兼有高速、高可靠性。能够在数字体系规划中完全由用户经过软件进行装备和编程,然后完结某种特定的功用。要研讨的是Altera 公司推出的一款FLEX10K 系列芯片,经过学习该芯片的作业原理和运用特性,规划一个依据FLEX10K 芯片的最小体系,经过对该最小体系的规划让我们能够更好的了解FPGA,并对其发生稠密的爱好,为更多想要了解学习FPGA 的人们做个很好的最初。

复位和晶振电路原理图规划

一个芯片,尤其是可编程芯片,一般在上电的瞬间需求一个时刻短的时刻进行内部参数的初始化,这个时分芯片无法当即进入作业状况。一般称上电初始化这些作业为复位,完结这个功用的电路称之为复位电路。本FPGA 芯片运用的是低电平复位,支撑上电复位和手动复位,RESET 按下之后发生低电平。

图4-2 复位电路原理图规划

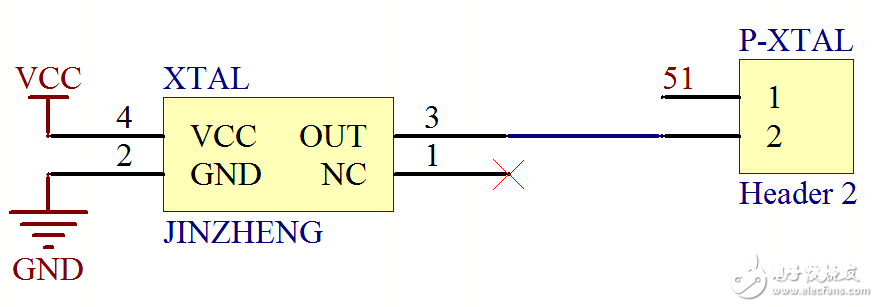

晶振是为电路供给频率基准的%&&&&&%,一般分红有源晶振和无源晶振两个大类,无源晶振需求芯片内部有振荡器,并且晶振的信号电压依据起振电路而定,答应不同的电压,但无源晶振一般信号质量和精度较差,需求准确匹配外围电路(电感、%&&&&&%、电阻等),如需替换晶振时要一起替换外围的电路。有源晶振不需求芯片的内部振荡器,能够供给高精度的频率基准,信号质量也较无源晶振要好。本FPGA 芯片选用50MHZ 的有源贴片晶振作为芯片作业的时钟输入(图4-3)。

图4-3 晶振电路原理图规划

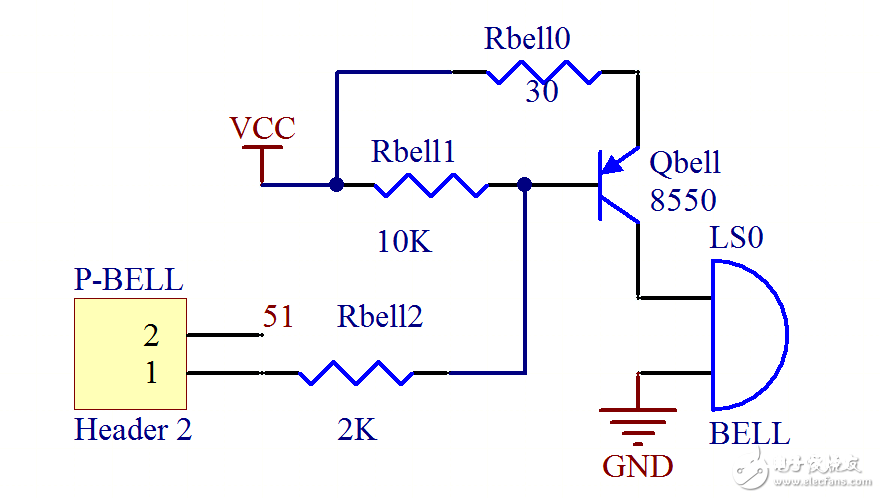

蜂鸣器电路原理图规划

电路很简略,需求阐明的是开发板上运用的是高品质的蜂鸣器,需求脉冲操控其发声。电路图中的晶体管当作开关来运用,当I/O 供给的驱动才能不行的时分,晶体管能增强驱动才能。低电平有用(图4-4)。

图4-4 蜂鸣器电路原理图规划

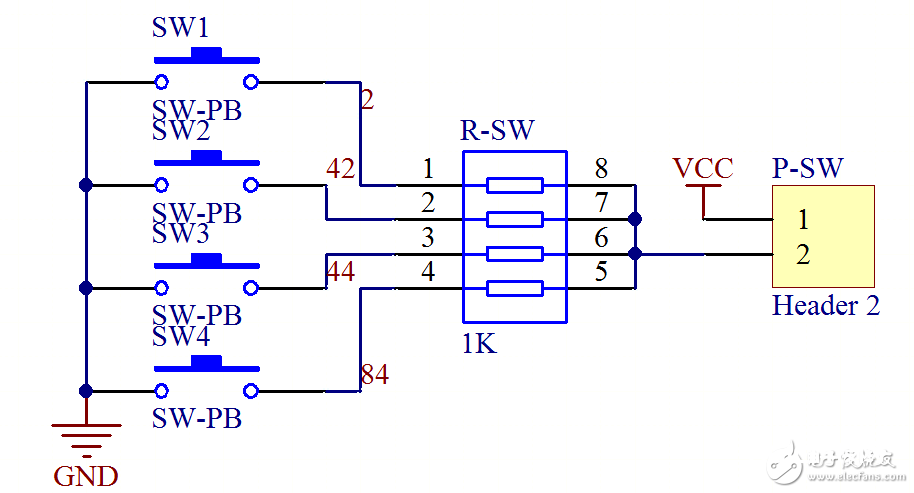

开关电路原理图规划

最小体系板上运用的四腿按键实际上是分两组,每组中的两个是相通的,而两组直接是经过上面的按钮来操控通断状况的。简略了解成开关就能够了,按下去两头就构成短路,松开手就构成开路。短路适当于输入0,开路为1。别的需求阐明的是,因为按键归于机械开关,按动进程不可避免存在颤动的现象,所以用户按下按键的时刻能够略微长一点(图4-5)。

图4-5 按键开关电路原理图规划

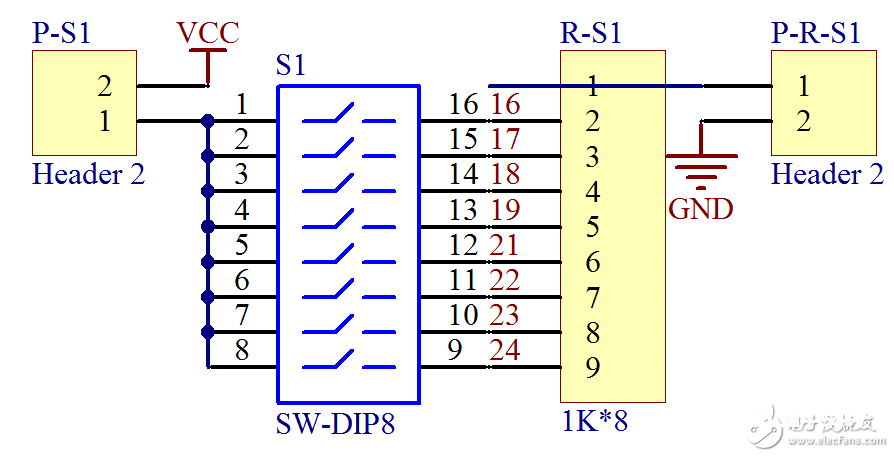

拨码开关便是适当与一个开关量,拨到ON 就表明接通,OFF 便是断开,在数字电路中对 0、1,一般用于二进制输入。本课题最小体系板运用八位拨码开关作为一个字节的输入,拨到ON 时适当于输入“1”,默许输入“0”(图4-6)。

图4-6 八位拨码开关电路原理图规划

JTAG 形式装备电路原理图规划

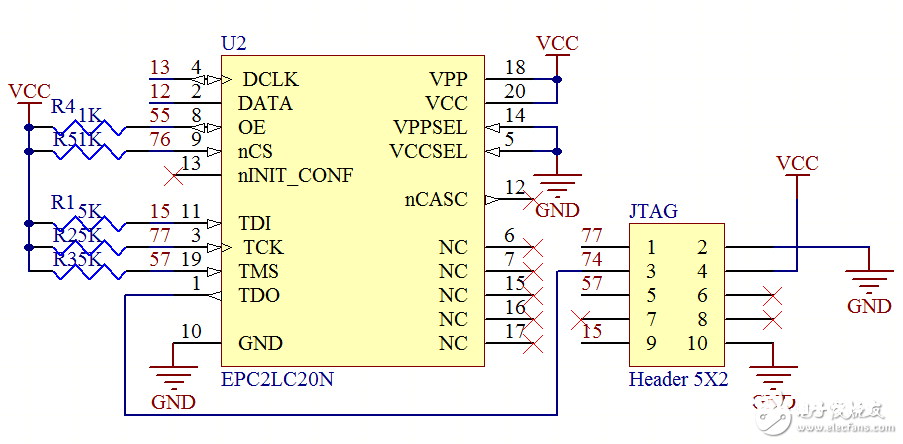

最小体系选用的FPGA 是Altera 公司的FLEX10K10 芯片,所以装备的PROM 选用的型号为EPC2LC20N,是20 脚的PLCC 封装,上拉电阻R4 是1K,其他的上拉电阻均是5K,TDI、TCK、TMS 和TDO 别离于JTAG 标准接口相连,完结装备电路的规划(图4-13)。

图4-13 JTAG 形式装备电路原理图规划

D 型并口下载线电路原理图规划

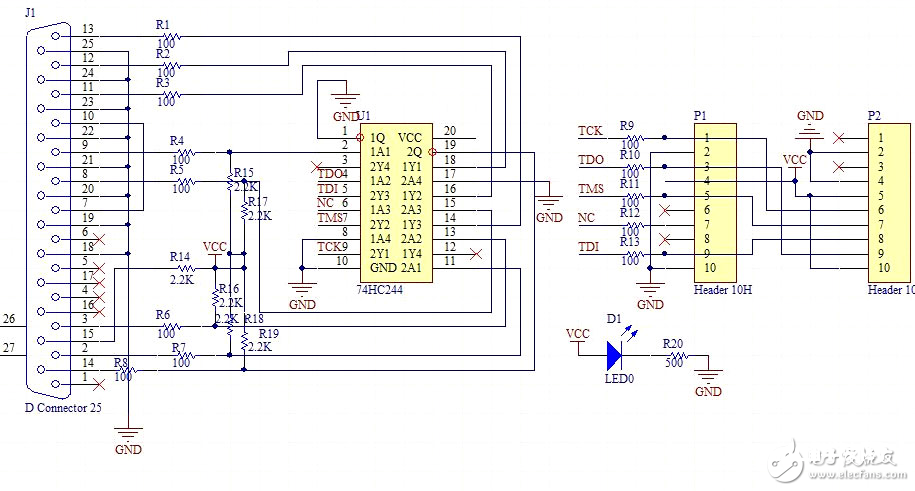

此下载线是由一个D 型25 针的并口与计算机相连接,10 针的一端与电路板相连接,数据的下载经过计算机直接装备,此下载线能够支撑2.5V、3.3V 及5.0V 电压的下载形式,是一种能够通用型的下载线(图4-15)。

图4-15 D 型并口下载线电路原理图规划

最小体系电路规划的整体电路原理图

运用AlTIum 软件规划的电路原理图,FPGA 最小体系板包含时钟电路、复位电路、电源电路、JATG 电路、PROM 装备电路、显现模块电路、开关电路以及各种接口电路(图4-16)。

图4-16 最小体系电路规划的整体电路原理图

本站网技能修改点评剖析:

在当时国内外信息技能高速开展的今日,电子体系数字化已成为众所周知的趋势。从传统的运用中小规划芯片构成电路体系到广泛地运用单片机,直至FPGA 在体系规划中的运用。电子规划技能已迈人了一个全新的阶段。FPGA 利用它的现场可编程特性,将本来的电路板级产品集成为芯片级产品,缩小体积,缩短体系研发周期,便利体系升级,具有容量大、逻辑功用强,进步体系的稳定性,并且兼有高速、高可靠性。越来越多的电子规划人员运用芯片进行电子体系的规划,经过依据FPGA 最小体系开发规划,阐明晰FAPG 芯片研讨的动机和研讨含义。

我们如有问题,欢迎在评论处评论。

——本站网收拾,转载请注明出处!

—————————————-

以连接器材料集锦——观察连接器现状与趋势!