1导言

近些年来,跟着电子技能的开展,无线通讯技能、核算机网络的开展,散布式无线数据收集网络技能开端鼓起,并敏捷的使用到各个范畴。在一些地势杂乱,不合适人类呈现的区域需求进行数据收集的情况下,都可以恰当的挑选无线散布式收集来进行。现有的无线散布式收集体系中,往往运用单片机、DSP等作为体系的主控操控单元。可是因为其本身作业特色,往往关于准确的守时操控以及并行处理才能上比FPGA弱。跟着FPGA等可编程逻辑器件的开展,为无线数据牢靠传输供给了很好的完结渠道。选用FPGA作为时序操控和信号处理的处理器,将使体系电路规划愈加简练、牢靠、灵敏,可有用的缩短开发周期,并下降开发本钱。

为此,依据CycloneIV+STM32规划了一种新式的无线散布式收集体系,完结了数据的高牢靠和同步传输。规划主要由3大部分组成:编码器、译码器、无线收发电台。在对编码器、译码器同步校准后,对待发送数据进行卷积编码,并转化为串行数据。数据转化为串行数据后,在串行数据帧头参加Barker码来完结帧的同步,并运用2条互为备份的数据传送通道一起发送数据。在数据接纳端检测到barker码后,本地对互为备份的双通道数据进行viterbi译码(本文规划的viterbi译码器选用并行结构,大大的下降译码时刻)。译码完毕后,本地对双通道数据进行循环冗余校验,并做出判选,终究履行相应指令。并在规守时刻给出相应反应信号。规划的无线收集体系,即便某一数据通道呈现少数错码,体系仍能有用的恢复出数据,并进行牢靠的数据传输。体系添加了监控模块,实时备份上传的数据并监控,如发现不能正常上传,则启用备用模块确保整个体系正常作业。体系不只能完结数据的高牢靠和同步传输,而且具有很好的适用性,可广泛使用工业中。

2无线散布式收集体系简介

2.1体系硬件简介

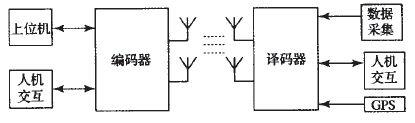

无线散布式收集体系包含编码器、译码器(编码器、译码器硬件完全相同,仅仅装备逻辑不同,可装备为编码器、译码器、中继站)和无线通讯电台。如图1所示,这是一个最简略的一对一式散布式体系。

图1无线散布式收集体系结构

编码器作为上位机与译码器之间的桥梁,经过USB/RS485通道进行发送、接纳指令和数据。译码器接纳编码器发来的指令进行装备和收集,并将数据存储至DDR2中。译码器收到上传指令后,上传数据至编码器。

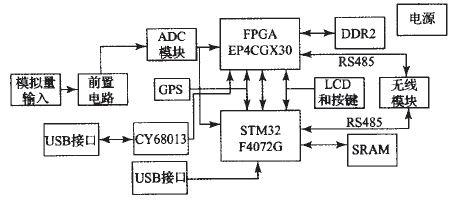

编码器/译码器硬件体系框图如图2所示。本体系主控单元由FPGA完结。FPGA选用Altera公司的EP4CGX30F407,逻辑单元为29440个,80个18×18乘法器,多达290个用户自定义IO.STM32作为监控和备用单元组成体系的根本架构,STM32F407ZG系列是依据高功能的ARM CortexTM-M4F的32位RISC内核,作业频率高达168 MHz,该STM32F407ZG系列选用高速嵌入式存储器(多达1 MB闪存,高达192 KB的SRAM),具有3个12位ADC,2个DAC,1个低功耗RTC,12个通用16位守时器,2个通用32位守时器。人机交互部分由16X2液晶显现字符模块和4个按键组成,其主要功用是经过按键对基站编号设置并显现在LCD上。无线模块选用WSN-03系列无线模块作为收发渠道,作业电压为5 V,传输速率和作业频段等都可装备。现在传输速率最大为115 200b ps,作业频为433 MHz可调。无线模块与FPGA主要以RXD/A,TXD/B,NRST(复位操控),SET(设置模块参数),SLP(休眠操控)信号线衔接。GPS模块选用VKl6U6进行定位,与FPGA以UART接口衔接,波特率定位9600 bps.ADC选用依据△-Σ技能的32 bits高精度低功耗模数转化芯片ADSl282,采样信号电平规模:差分输人一2.5~+2.5 V.单个译码器有6个收集通道,以2 k采样率,采样经常16 S来核算,单个译码器纯数据量为6×2 k×16×24-6144 Kbits.考虑到编码器,一次采样,8个基站的数据经编码后数据总量为98 304 Kbits,所以编码器和译码器需添加l片Micron Technology公司的MT47H256M8HG-37E IT(256Meg×8)作为缓存空间。因为DDR2 SDRAM需求特定的操控读写时序,体系直接选用Quartus II自带的“DDR2 SDRAM High-Performance Controller”IP CORE.USB部分由2个通道组成,一个是由FPGA、CY7C68013和USB接口组成;另一个由STM32(自带USB驱动)和USB接口组成。一起本规划中还添加了RS485串口,使整个体系与上位机能坚持实时通讯,为体系的长途操控供给了或许,并能坚持体系更新。

图2体系结构

2.2体系数据流程

体系的数据流程为:同步校准译码器,设置各个译码器接纳指令后的延时-编码器装备收集参数、指令-译码器收集数据保存至DDR2中一各译码器分时接纳数据上传指令并上传数据-编码器将数据汇总保存至DDR2-数据收集齐后经过USB/RS485上传至上位机。译码器节点合作核算机对各个点的数据进行轮询收集,它包含了无线传输模块和与核算机通讯的USB接口。STM32将组帧后的数据备份并实时监控FPGA,如在规守时刻或未能按指令进行作业,STM32将替代FPGA并使FPGA进入断电状况。

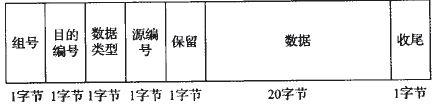

2.3体系组帧格局

编码器与译码器之间是一对多的联系,译码器分时上传数据,译码器有2个通道,译码器有仅有的装备编号。数据帧的格局如图3所示。数据帧中除20字节有用数据之外,还包含组号、意图编号等。

图3编码器、译码器间数据帧格局

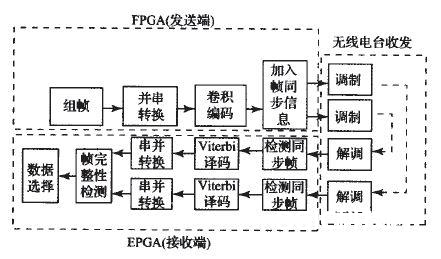

为了改进接纳信号质量,本体系引进信道编码的办法来改进信道质量。详细如图4所示。发送端对数据进行组帧、并串转化、卷积编码、参加同步帧信息后,把数据发送至无线通讯电台进行调制。接纳端的无线通讯电台对信号进行解调后发送数据至接纳端的FPGA.接纳端的FPGA检测到帧同步信息后对接下来的数据保存,并进行Viterbi译码。FPGA对双通道的数据进行冗余校验,并挑选正确的数据履行相关操作。

图4无线数据传输

3无线散布式收集体系数据传输的完结

3.1牢靠性

待发数据经卷积编码,互为备份的双通道发送,Viterbi译码,冗余校验,数据判选,体系可以很好的进行无线收发。

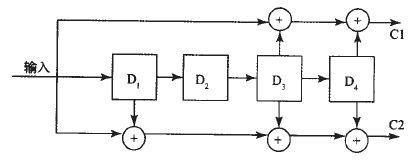

3.1.1卷积编码

数据组帧完结后,由低位至高位进行并串转化,进行卷积编码。卷积编码是一种纠错信道编码,是由接连的输入信息序列经编码后得到接连输出的编码序列口。以(n,k,m)来描绘卷积码,k为每次输入到卷积编码器的bit数,行为每k元组码字对应的卷积码输出n元组码字,m为编码贮存度。卷积编码生成的n元组元不只与当时输入有联系,还与前面m一1个输入的k元组有联系。本体系选用(2,1,4)卷积编码器,如图5所示。图中“+”代表异或。每bit经编码后都有2 bit输出(C1,C2)。

图5(2,1,4)卷积编码器

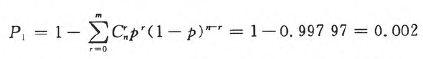

3.1.2 Viterbi译码

接纳端有2个接纳通道,互不搅扰。接纳端对2个通道一起译码。译码选用Viterbi译码。Viterbi译码算法是一种卷积码的解码算法。Viterbi译码依据最大似然算法规矩,能到达最佳译码,特别合适向前纠错。以本规划为例,依据图5,编码器4个延时状况(0,1)组成整个编码器的16个状况(D4D3D2D1),每个状况在编码器输入1或0时,跳转到另一个状况。而且输出也随之改动。译码便是编码的逆进程。算法规矩恣意t时刻收到的数据都要进行32次途径值核算、16次比较,比较后每个状况只保存一个途径值,为接下来核算减少了一半的运算量。重复208次,从16条幸存途径中选出一条途径值最小的,反推出这条途径,得出相应的译码输出。考虑到每次译码后,译码器都能回到初始状况,所以源数据终究加了8 bit的“0”。本规划选用并行处理结构,经214个周期复原出源码。

在规划FPGA逻辑时,根本选用多条并行的流水线技能,译码部分包含4个子模块:加比选模块、回溯模块、存储模块和时钟操控模块。途径值的核算和比较在3个时钟周期内完结,4个模块一起运转,大大的下降了译码时刻。别的,为了进步FPGA功率,体系参加采样触发信号,确保系逻辑可以安稳运转。

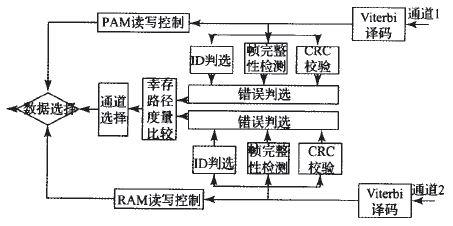

3.1.3数据判选

经译码后,接纳端已接纳到2组互为备份的数据。经实践证明,简略的并联冗余能大大的进步体系的牢靠性。详细挑选流程如图6所示。2路数据经Viterbi译码后,开端接纳一帧数据,并写入RAM中,一起核算CRC校验、帧完整性检测、ID是否契合本地。上述检测都没问题时,对2路幸存途径的度量值进行比较,挑选值小的通道作为终究数据。

图6数据的挑选

3.2同步的完结

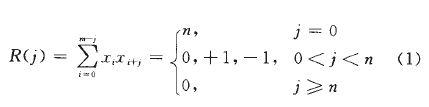

为了确保编码器和译码器之间能严厉完结同步,数据帧需求参加同步帧。完结帧同步的办法一般有2种:起止同步法和会集式刺进同步法。起止式同步比较简略,一般在数据码元的开端和完毕方位参加特定的开端和中止脉冲来表明数据帧的开端和完毕。会集刺进式同步法中插人的同步码要求在接纳端进行同步辨认时呈现伪同步的概率尽或许低,而且要求该码具有尖利的自相关特性以便辨认。7位巴克码作为帧同步码,其部分自相关函数为:

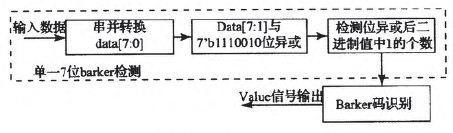

由上公式核算可知,7位巴克码的自相关函数在j一0时呈现尖利的单峰特性。规划中选用2组同步帧头作为同步码,同步帧头由7位巴克码和1 bit的0组成。

到现在为止,待发数据bit数为:208×2+8×2-432 bits.经调制解调后,接纳端检测帧同步信息,同步信息为2组11100100组成。每组同步信息高7位与7位巴克码比较,答应犯错位数在1位以内。设P为码元过错概率,行为同步码组的码元数,m为判定其答应码组中的过错码元最大数,在本体系中行n=7,m=1.在P=0.01时,单一barker码的漏同步概率为:

当2组同步帧都满意时,帧同步树立,接纳端保存接下来的数据。无线通讯电台与FPGA以rs485衔接,如图7所示,FPGA检测X是否为“0”,当检测到“0”,不接纳端对接下来的数据X与本地巴克码对应位进行位异或运算。当检测1 byte barker码,错1位以内时,宣布一value脉冲。当检测到2个value脉冲时,阐明同步已树立,接纳端开端存储接下来的数据。

图7 barler码辨认

4体系监控模块的完结

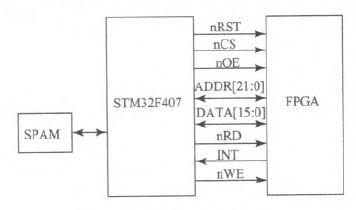

STM32与FPGA衔接如图8所示,因为ARM与FPGA的彼此通讯直接影响着操控器的功能,所以该并行总线的规划就成为一个十分要害的问题。该总线可以包含芯片的地址总线(ADDR[021])、数据总线(DB[015])、操控总线、复位信号(nRST)以及中止信号线(INT),其间操控总线包含使能信号(nOE)、片选信号(nCS)、读信号(nRD)、写信号(nWE),这样做的优点是,将FPGA芯片存储器化,即STM32可经过对特定地址的访问来操控FPGA作业,而且可经过一起的复位信号将STM32与FPGA芯片一起复位,尽量防止总线竞赛和冒险现象的呈现。

图8 STM32与FPGA衔接

STM32与FPGA一起接纳指令,在解析完指令后,FPGA应在规矩的时刻内发送数据,FH认组帧完结时,宣布INT信号至黜2请求中止。假如STM32在规守时刻内没有接纳到FPGA发来的INT信号,将开端计时,计时时刻内未能接纳INT信号,STM32将中止FPGA供电电源作业,由STM32替代FPGA作业,确保整个体系能安稳进行。

5体系测验

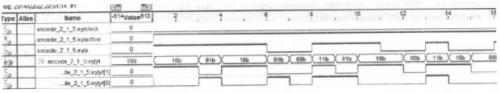

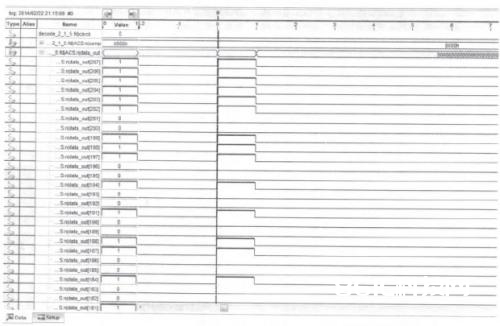

编码器什物如图9所示。测验时建立一对编码、译码器,选用12 V的直流电源供电。待发数据为208 bits,即208b00000000_10010010_01100100_10011001_00100110_01001001_10010010_01100100_10011001_00100110_01001001_10010010_01100100_10011001_00100110_01001001_10010010_01100100_10011001_00100110_01001001_10010010_01100100_10011001_00100111_00111111;图10显现了测验中使用SignalTap II截取经卷积编码后输出的部分信号波形。其间z为串行输人数据,yt为卷积编码后输出的数据。数据经无线发送后,经Viterbi译码,仿真图形如图11所示,编码器发送的数据为208 bit S,data_out为译码输出的部分数据,译码数据与发送端的高低位次序相反。因为数据经发送后,高低位交换,图上只截取了经Viterbi译码后的高27位的译码成果。经屡次测验,数据传输正常,在少数不接连的错码情况下,体系可以主动纠正。

图9编码器什物

图l0(2,1,4)编码器输出

图ll Viterbi译码输出

6定论

在无线散布式收集体系规划中,选用了依据卷积编码、Viterbi译码的编码和互为备份的双通道传输计划,使用了FPGA内丰厚的逻辑资源以及存储资源,完结了数据的远距离同步牢靠传输。参加备份数据通道后,经过FPGA内部逻辑操控,在硬件上完结了对两路数据的实时校验及主动判选,进步了体系的安稳性和牢靠性。比较于“备份-重传”等机制,该办法完结简略、实时性好,即便某一通道不能正常作业,体系仍能正常进行。该无线散布收集体系,满意了现在同步触发和数据量不大情况下的传输。本文提出的互为备份的双通道编解码、数据冗余传输机制,亦可使用相关无线传输范畴,以进步远距离数据传输的牢靠性和安稳性。