问题:

“在测验信号边缘的上升/下降时刻的时分,跟我挑选的存储深度有没有联系。比方我运用40GS/S的采样率测验PCIE CLK,假如在屏幕上显现一个时钟周期测验它的上升下降时刻和我调节时基到8M的存储深度时测验到的上升下降时刻有没有差异?”

答复:

这是一个非常好的问题。其实我在培训时也常问客户别的一个问题:您知道示波器中上升时刻是怎样确认的吗?我在各种讲座会和培训中问这个问题时至今竟然没有得到过一次精确的答案!这涉及到示波器中对上升时刻的算法界说。很多人知道“上升沿”的10%-90%,但“上升沿”是指什么呢?这时分工程师们会用手从波形的下面指到上面。那么从下面到上面是指下面的最小值点到上面的最大值点呢仍是下面的平均值方位到上面的平均值方位呢?

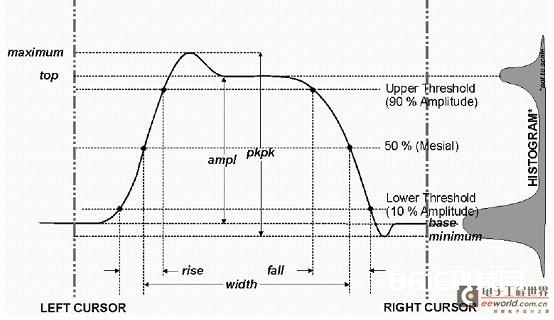

示波器里核算上升沿需求界说“算法”。IEEE界说的算法如图一所示。上升沿的确认取决于参数“top”(基顶)和“base”(基底)的确认。 正 确的确认基顶和基底是正确的参数核算的根底。在剖析的开端,示波器首要核算一个波形数据的直方图,时刻跨度由两个时刻光标之间的时刻值确认,默许状况下光 标是从最左面到最右边。例如,假如波形是在两个状况跃变的,那么其直方图将包含两个波峰。剖析办法将测验辨认包含了最大的数据密度的这两组数据。所以,和 这两组相关联的最大概率的状况将被核算出来,以决议基顶和基底。基顶相对应于上部的最大概率方位,基底相对应于下部的最大概率方位。

图一示波器中一些常用丈量参数的算法界说

一旦确认了基顶值和基底值,上升时刻和下降时刻的核算就很简单了。基顶值减去基底值便是幅值,幅值的90%和10%的门限电平之间的时刻间隔便是上升时刻。 假如用rise@level,能够挑选上升时刻的门限电压。假如挑选肯定设置,上升时刻和下降时刻的核算便是丈量在上升沿或下降沿上两个交叉点的时刻间隔。可是,假如挑选了相对设置,在基顶线和基底线之间的笔直间隔被一个百分比切割(base=0%,top=100%),这样来决议交叉点的笔直方位,在上升沿和下降沿上的交叉点之间的时刻间隔被核算出来以得到上升时刻和下降时刻。

顶 部和底部样本数的多少会影响到基顶和基底确认的精确性。假如示波器上只一个时钟周期,顶部和底部的样本数很少,假如时钟信号上有一点点的过冲或下冲就会影 响到直方图的散布的最大概率状况的确认。因而,在丈量时钟咱们主张屏幕上收集的周期数尽量多一些。至此,上面的问题的答案已是显而易见的了。

值得阐明的是,有时分示波器的参数下方的状况显现中有 的图标,脉冲上的一个十字表明示波器不能够确认基顶和基底,可是,丈量仍然是有用的。

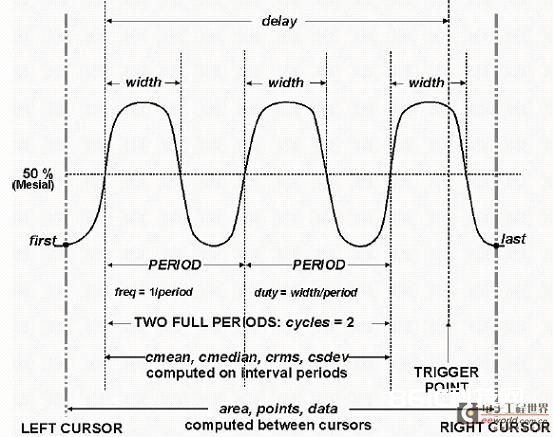

图二一些时刻参数的界说

象宽度、周期和推迟这样的时刻参数都在中心线处丈量(图二)。中心线坐落基底线和基顶线的中心方位(50%)。时刻参数的核算依赖于观察窗内包含的周期的数量。假如周期的数量不是整数,参数的丈量,如有用值(RMS)或均值(MEAN)这样的参数)是有差错的。为避免这种误差,仪器运用周期参数,包含crms 和cmean,这些参数强迫在整数个周期内进行核算。

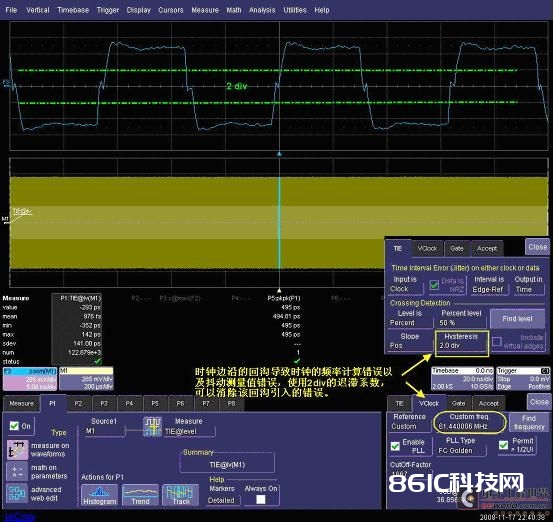

在示波器水平轴丈量中有一个常被疏忽的选项叫Hysteresis(磁滞)。 Hysteresis选项利用了电平之上或之下的约束,这能避免丈量到噪声或其它搅扰。Hysteresis的设置以milli-divisions(千分之一格)为单位指定,其设置的原则是:1. Hysteresis 有必要大于您期望疏忽掉的最大噪声尖峰。 2.可用的最大Hysteresis 值小于从电平到最近的波形极值的间隔。3.除非您知道将在任何周期内产生的最大的噪声和最近的极值电平,不然就在电平的两边留出余量。图三所示为测验频率为61.44MHz时钟的TIE@lv参数,但PLL在核算频率时得到的成果为5.334099599GHz,这是因为缺省时Hystersis系数为500mdiv(即0.5格),示波器中将时钟上升沿和下降沿的回钩都当作了是一个个小的脉冲来核算频率,TIE@lv的测验成果也当然错了。

图三运用TIE的缺省设置,Hysteresis值为500mdiv

因为时钟边缘存在回沟,所以有必要增大迟滞系数,在图四中修正为2div,如下所示,这时示波器找到了正确的频率61.44MHz,TIE颤动的峰峰值为P5=495ps,有用值为P1的sdev 等于141ps。

图四修正TIE的Hystersis设置

在使用一些参数进行丈量时,咱们都应知道这些参数在示波器中是怎样界说的,了解每一个设置菜单是什么意义。老板说,以“知其所以然”的情绪面临问题是做工程师的好习