在一个体系中添加多个安全数字 (SD) 器材的需求日益增长。但是,大多数主机器材(如 Intel PXA270、TI OMAP和Qualcomm MSM处理器)都只供给一个SD接口。走运的是,运用杂乱可编程逻辑器材(CPLD)即可使主机器材支撑恣意数量的SD器材。本文具体叙说一种依据可缩放主动侦测双向多路复用器的规划。

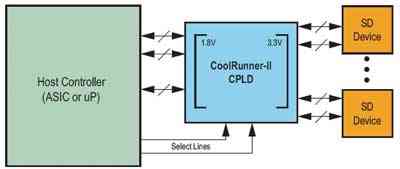

图1所示为通用的CPLD运用模型,可认为仅自带一个SD接口的给定主机器材集成恣意数量的SD端口。CPLD处于主机操控器和SD器材之间。这样,CPLD便起到双向多路复用器的效果,使主机器材可以与选定的恣意SD器材通讯。更重要的是,这种规划没有方向操控引脚,也便是说CPLD主动检测数据流方向。

图1 用CPLD添加SD端口

这种完成办法极端灵敏且可缩放,答应随意增减SD端口数量,还支撑SPI形式、1位数据形式和 4 位数据形式中任一种界说的SD卡形式。

在此类运用中运用CPLD器材,首要意图是为主机操控器供给更多的SD端口,一起在主机器材与SD卡之间完成电平转化和逻辑阻隔。图1所示为主机器材是1.8V而 SD器材是3.3V的景象。业界最新CPLD的待机电流微乎其微,而动态功耗极低。因此,在体系中集成一个杂乱可编程逻辑器材不会明显影响功率预算。

契合SDA标准

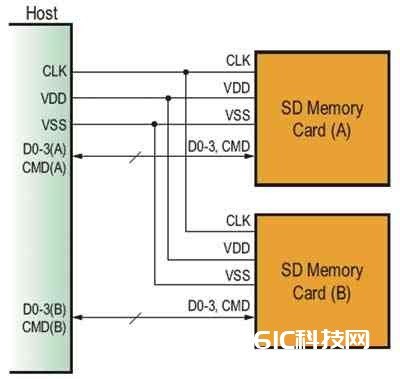

依据SDA(安全数字协会)标准,一条SD总线只能支撑一个SD器材。时钟引脚可以共用,但DAT[3:0]和CMD线则必须由每个SD器材独占,如图2所示。

图2 SD体系总线拓扑结构

此参阅规划完全契合SDA标准。下面介绍当运用只要一条总线的操控器支撑恣意数量的SD 器材时怎么满意上述要求。

CPLD规划

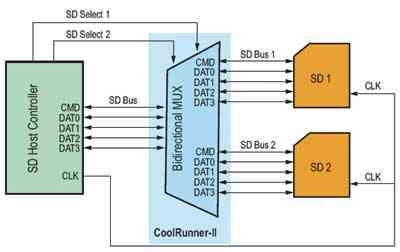

图 3 所示为用此规划完成两个SD器材共用同一SD主机接口时的典型用法。从概念上讲,可以将这种规划视为和用作双向多路复用器。主机器材通过“挑选”信号操控CPLD,然后指示与哪个SD器材通讯。一旦选中某个SD器材,CPLD器材中的逻辑便主动检测数据流的方向,而且让数据相应活动(从主机器材流向SD卡,或许从SD卡流向主机器材)。此规划不需要方向操控引脚,因此运用方便。

图3 模块级图:双向多路复用器

当多路复用器相应切换时,主机器材可别离拜访各SD器材,而不会影响另一SD器材的状况。假如主机器材和SD器材都未驱动数据,则CPLD让体系处于默许的呈弱上拉状况的高阻抗。此电路的首要用途是加强主机器材的SD才能,但也可用此电路供给电平转化和/或逻辑阻隔。

完成细节

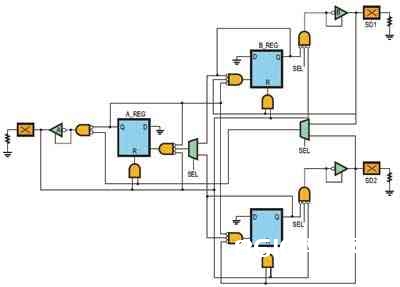

图4所示为1:2双向多路复用器规划的实践逻辑电路,该规划可用VHDL言语描绘。在初始或闲暇状况下,主机器材和SD卡应处于呈弱上拉状况的高阻抗。因此,图4中的电路规划成对 CPLD的输出缓冲器进行三态操控,然后使外部上拉电阻起效果。寄存器A (A_REG)和寄存器B (B_REG)都规划成在上电时初始化为逻辑“0”。

图4 两个SD器材的SD多路复用器电路

通过向 CPLD 输入“挑选”信号来挑选SD卡。当“挑选”信号为逻辑“0”时挑选SD1,而当“挑选”信号为逻辑“1”时挑选SD2器材。为电路叙说简明起见,咱们假设在以下评论中主机器材只挑选与SD1通讯。

此规划的主动方向操控方面的完成方法为:当主机器材与SD1器材二者之一置为低时发动业务。例如,假如主机器材预备向 SD1 器材传送数据,则主机器材通过将A侧置为低来开端传送。在置为低时,电路中的逻辑检测到置低的下降沿,而且通过启用“B”输出缓冲器置为有用来呼应,而“A”输出缓冲器仍坚持无效状况。尤其是当A置为低时,会向A_REG的时钟输入传送一个上升沿。继时钟操控之后,A_REG的Q输出变为逻辑“1”,然后阻挠B_REG接纳时钟操控事情。当A变为低时,逻辑门B1在A_REG时钟操控与触发的一起输出一个逻辑“1”。这样便可启用“B”输出缓冲器,而B最终会跟从A置为低。

反之,当A从低转为高时,逻辑门B1输出一个低信号,对B输出缓冲器进行三态操控。这样便通过外部上拉电阻强制B变为高。一旦A侧和B侧都变为高,则A_REG和B_REG 复位到0。此进程无限次重复。当SD1要向主机器材传送数据时,状况相反。别的,假如主机器材预备与SD2器材通讯,则电路的“挑选”信号输入置为逻辑“1”,其事情次序与上述相似。

对于此电路,用ModelSim进行了广泛的功用和时序仿真,测验鼓励现已包括在VHDL 下载中。图5所示为部分仿真成果。

在图5的榜首部分中,“挑选”信号输入坚持为低。白色虚线指示“弱1”状况,换言之便是表明上拉状况。在榜首个业务中,主机器材测验向SD1传送数据,SD1随即呼应。紧接着,SD1器材测验向主机器材传送数据,主机器材随即呼应。当“挑选”信号输入置为低时,会产生相似事情。主机器材向SD2器材传送数据,然后SD2器材向主机器材传送数据。

图5 仿真成果

2 硬件成果

Xilinx制作了一块SD多路复用器演示板,并用该电路板验证了此双向多路复用规划。图 6 所示为该演示板,在中心方位有一个CoolRunner-II XC2C32A CPLD。沿该板的上边缘是两个SD卡插槽。该板的最下部分是按照SD卡的实践尺度规划的。图7所示为插在USB SD卡读卡器中的演示板。无论是榜首张卡仍是第二张卡,XC2C32A都能使PC与之完美地通讯。

图6 Xilinx SD多路复用器演示板

图7 插在USB SD卡读卡器中的Xilinx演示板

器材资源占用率

表 1 列出了各种完成的器材资源占用率统计数据。如SDA标准中所述,SD卡有三种界说的信令形式,即SPI形式、1位数据传输形式和4位数据传输形式。此规划可轻松地适用于恣意一种选定形式。该规划还答应运用恣意数量的 SD 扩展端口,默许的VHDL代码设置为两个端口。

电压和电流考虑事项

SDA标准对SD卡规则了严厉的电压和电流要求。可编程逻辑器材功耗极低而且具有 I/O分组等功用,因此十分合适这种运用。I/O可以装备成 1.5V、1.8V、2.5V或3.3V,因此可以衔接任何SD器材。CPLD还包括I/O组,因此具有在处理器与SD卡之间进行电压转化的功用。

现有杂乱可编程逻辑器材的极低功耗特性使待机作业电流低达 15μA。在体系中添加一个低功耗CPLD对电流预算影响甚微。

定论

跟着SD器材的推行,将越来越需要用主机操控器支撑多个SD器材。本文针对这一问题供给了一种通过验证的解决方案。此解决方案让规划人员可以灵敏地挑选在一个体系中完成两个或更多SD器材。