跟着航天技能的前进和卫星与高空勘探技能的开展,需求一种高速、可扩展、低功耗、低成本的通用通讯链路接口来满意星载数据传输要求。SpaceWire总线标准便是一种高速的、点对点、全双工的串行总线网络,以IEEE1355-1995和LVDS两个商业标准相结合而提出的一种星载数据总线。本文在研讨SpaceWire总线协议的根底上,剖析了根据PCI接口的SpaceWire节点通讯板卡的硬件完结架构,并侧重剖析硬件体系各个组成部分的功用和规划,为往后SpaceWire总线在其他的运用打下了杰出的根底。

SpaceWire概述

SpaceWire是为更好地满意星载设备间高速数据传输需求而提出的一种高速的(2~400Mbit/s,现在完结的宇航级节点设备之间的速度为200Mbit/s)、点对点、全双工的串行总线网络,在2003年1月正式成为欧空局标准。它致力于航天器有效载荷体系数据和操控信息的处理以满意未来高功用高速数据传输为方针,供给了一种一致的用来衔接传感器、数据处理单元、大容量存储器、遥测子体系以及电地支撑设备EGSE(electronic ground support equipment)的根底架构。

SpaceWire标准详细包含了链路、节点和路由三方面的内容。所谓SpaceWire节点,是指传输包的流出设备或许流向设备,可所以处理器、存储单元、传感器、电地支撑设备(EGSE)或衔接在SpaceWire总线网络上的其它单元。

SpaceWire节点通讯板卡硬件规划

EMBC1000-PCISPW是欧比特公司自主研发的彻底遵从并完结ECSS-E-ST-50-12C协议标准的航天设备间的高速SpaceWire数据总线的节点终端通讯板卡(本板卡完结了200Mbit/s的速率)。此SpaceWire总线节点通讯板卡能够嵌入在航天子体系中,将航天子体系与其它SpaceWire网络之间衔接,确保航天子体系之间高速、实时、确认、可靠地进行数据交换。其硬件规划分为FPGA操控模块、PCI接口模块、MDM9S接口模块和SRAM缓存模块。

1.节点通讯卡整体结构

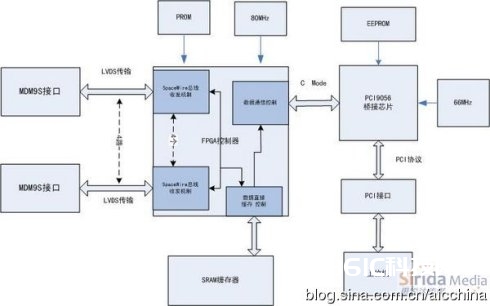

本文规划的SpaceWire总线节点体系硬件架构如图1所示。各模块的功用如下:

FPGA操控模块:完结4路SpaceWire总线通讯协议接口功用,硬件完结LVDS信号传输,完结数据通讯进程中产生的很多数据完结缓存并与PCI9056通讯接口等功用;

SRAM缓存器:存储SPW总线收发机制中产生的大容量高速数据的缓存功用;

MDM9S接口模块:MDM9S接口完结FPGA的LVDS信号与外部SPW设备之间的接口功用;

PCI接口模块:完结PCI总线的接口协议功用,完结FPGA与上位机软件间进行数据的通讯。

2.FPGA操控器

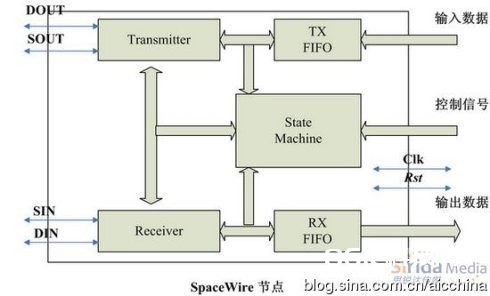

FPGA操控器完结4路SpaceWire总线协议节点操控的悉数功用,包含状况机操控模块、发送模块、接纳模块、产生缓存模块(TXFIFO)、接纳缓存模块(RXFIFO)以及与PCI9056通讯接口模块(PC%&&&&&%TRL)等功用,如图2所示。

本规划中FPGA选用Altera公司的EP3C55F484I7N芯片,时钟频率选用80MHz,一起为了完结SpaceWire总线传输速率,FPGA内部选用了PLL对时钟进行了分频,以满意规划要求。

状况机操控器担任对SPW终端节点的功用操控寄存器、节点状况寄存器、链路地址、时钟分频寄存器、直接存储拜访(DMA)通道操控寄存器等进行参数装备,经过PCI9056地址映射到了上位机的某一段地址空间,因而上位机软件就能够直接经过对其相关寄存器装备即可完结对SpaceWire节点模块的操控。下面分发送和接纳两个方面简略介绍单个SpaceWire总线节点的作业进程:

接纳模块将从MDM9S接口接纳到的选用DS(Data-Strobe)方法传输的LVDS信号进行数据康复,并将其传入到接纳缓存中,再传输至FPGA内部的双口RAM中,上位机经过PCI9056桥接芯片的地址映射能够直接读取该双口RAM的数据来进行剖析处理。发送进程与接纳进程相似并相反。

3.PCI9056桥接芯片

在SpaceWire总线节点终端体系与航电计算机体系之间完结PCI通讯有两个方法,其一便是选用CPLD或许FPGA专门作为一个独立的模块完结PCI协议,别的一种方法便是选用专用PCI协议芯片。本终端体系规划中从功用稳定性和结构简易性方面动身,挑选用PLX公司出产的PCI9056芯片,该芯片能够设置成多种传输方式,完结SpaceWire总线节点与航电设备之间的通讯桥接功用。

在PCI9056与本地FPGA之间的通讯分为直接主方式、直接从方式和DMA方式。因为PCI通讯要求到达SpaceWire总线网络的2Mbit/s至400Mbit/s通讯速率(本板卡完结了200Mbit/s),这儿选用的芯片时钟频率为66MHz,传输方式为直接从方式,PCI9056为主芯片,FPGA为从芯片。

为了与PCI9056进行高效的数据通讯,FPGA内部划出了一部分内存以装备成双口RAM的方式完结PCI9056对SpaceWire数据的收发以及相应操控寄存器的操控传输。

参考文献:

[1] EMBC1000-PCISPW型SpaceWire节点通讯板卡运用说明书,欧比特操控工程股份有限公司,2013。

[2] 康咏岐, 面向航天运用的SpaceWire节点单元的IP 核规划与完结[J],微电子学与计算机,2005,22(9),120-123。

[3] 陈健飞,曹松,SpaceWire总线接口终端的规划与完结[J],微计算机信息,2010,26(82),123-124。

[4] 陈大羽等,空间高速总线SpaceWire节点的规划与完结[J],航天回来与遥感,2010,31(4),58-64