首要阐明下,之前没有搞时钟就开端看I/O口还有外部中止是不对的。幸亏发现的不晚,现在把这有必要的一课给补上。假如连时钟都搞不明白,下面的外设是必定无法弄的。别的抛弃了本来做一个整体程序包的主意,主要是太浪费时刻了,完结一个器材的驱动还要想把他无缝的添加到本来的程序结构里去,现在不是做这个作业的时分,需求快速的把测验完结,然后上体系去调试。

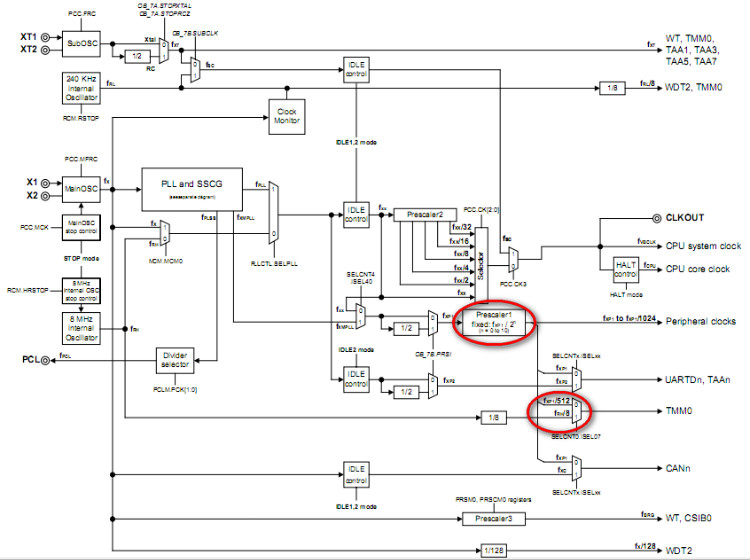

下面开端正题,V850的时钟仍是比较饶人的,需求细心的去读datasheet,别的我到现在还有无法了解的当地在datasheet上面。下图是体系时钟的框图:(赤色的圈里便是不了解的当地,不知道在哪个当地设置)

代码出处 system.c

void SystemClkInit( void )

{

unsigned char psval = 0;

VSWC = CG_VSWC_VALUE; // 设置 内部外围功用操控寄存器 值为17

/* Set main system clock */

OSTS = CG_OSCSTAB_SEL16; // 设置 晶振安稳时刻挑选寄存器 值为0x06(2^16/fx),为下面检测OSTC做准备

psval = CG_CPUCLK_MAINFEEDBACK | CG_CPUCLK_SUBNOTFEED | CG_CPUCLK_MAINENABLE;

PRCMD = psval;

PCC = psval; // 设置 MCU时钟操控寄存器 值为0x80,制止子时钟振动器,使能主时钟振动器

while (!(OSTC || 0x00)) // 检测 晶振安稳时刻状况寄存器 的最低为是不是为1(晶振震动以安稳)

{

;

}

PLLS = CG_PLLLOCKUP_SEL1; // 设置 锁相环确定时刻标准寄存器 值为0x03(2^13/fX (default value)),为下面检测LOCKR做准备

PLLON = 1; // 设置 PLLCTL锁相环操控寄存器 最低位为1,使能锁相环发动

while (LOCKR && 0x01) // 检测 锁相环确定状况寄存器 的最低为是不是为0(锁相环以确定)

{

;

}

psval = CG_MAINSYS_MAINOSC;

PRCMD = psval;

MCM = psval; // 设置 体系主时钟方法寄存器 值为0x01(设定主时钟源非内部高速振动源)

SELPLL = 1; // 设置 PLLCTL锁相环操控寄存器 的次低位为1,与MCM寄存器合作设置主时钟通过锁相环倍频

/* Set fCPU */

psval = PCC | CG_CPUCLK_MAIN0; // 设置 体系主时钟的分频系数,对内部设备时钟没有任何影响,依然为32MHz

PRCMD = psval;

PCC = psval; // 设置 MCU时钟操控寄存器 的低4位,设置分频系数

RCM = CG_RCM_INITIALVALUE | CG_LOWCLK_STOP | CG_H%&&&&&%LK_STOP;//设置 内部振动器形式寄存器 值为0x83,封闭内部高速,低速振动源

/* Set fXP1 */

SELCNT4 = CG_SELCNT4_FXX; // 设置 挑选操控寄存器4 值为0x00,挑选时钟源为fxx

/* Set fBRG */

PRSM0 = CG_PRESCALER3_DISABLE; // 设置 预分频3方法寄存器 值为0x00,制止分频

/* WDT2 setting */

WDTM2 = 0x1F; // 设置 看门狗定时器2方法寄存器 值为0x1F,看门狗中止

}

代码出处 main.c

void main( void )

{

SystemClkInit(); // 初始化体系时钟为32MHz

/* CLKOUT pin set */

PMCCM |= 0x02; // 设置体系时钟输出引脚使能,输出值为体系时钟(32MHz)

/* PCL pin set */

PFC9H &= 0xDF;

PFCE9H |= 0x20;

PMC9H |= 0x20; // 设置P9_13脚为第二功用,时钟输出功用

PCLM = CG_PCL_ENABLE | CG_PCL_SEL0;

// 设置时钟输出功用使能,而且设置其分频系数(这里是进行4分频,输出为8MHz)

while (1);

}

代码出处 system.h

/* CPU system clock selection (CK3~0) */

#define CG_CPUCLK 0x07

#define CG_CPUCLK_MAIN0 0x00 /* fCPU = fXX */

#define CG_CPUCLK_MAIN1 0x01 /* fCPU = fXX/2 */

#define CG_CPUCLK_MAIN2 0x02 /* fCPU = fXX/2^2 */

#define CG_CPUCLK_MAIN3 0x03 /* fCPU = fXX/2^3 */

#define CG_CPUCLK_MAIN4 0x04 /* fCPU = fXX/2^4 */

#define CG_CPUCLK_MAIN5 0x05 /* fCPU = fXX/2^5 */

#define CG_CPUCLK_SUB 0x08 /* fSC (fXT or fRL) */

/* PCL clock frequency selection (PCK1~0) */

#define CG_PCL_SEL0 0x00 /* fPCL= fPLLO/4 */

#define CG_PCL_SEL1 0x01 /* fPCL= fPLLO/8 */

#define CG_PCL_SEL2 0x02 /* fPCL= fPLLO/16 */

#define CG_PCL_SEL3 0x03 /* fPCL= fPLLO/32 */

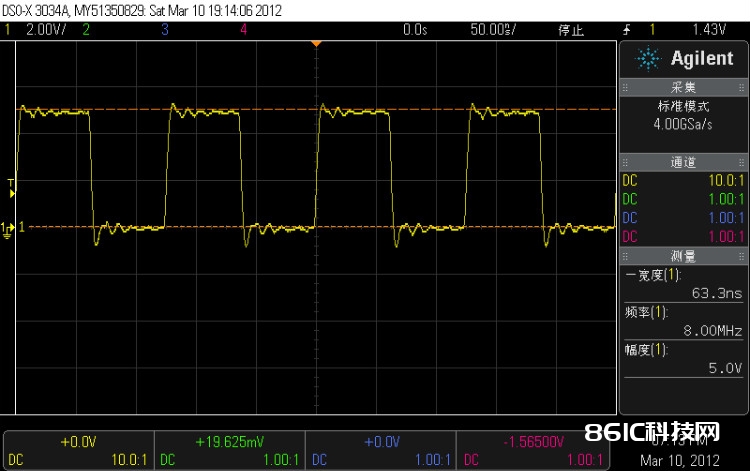

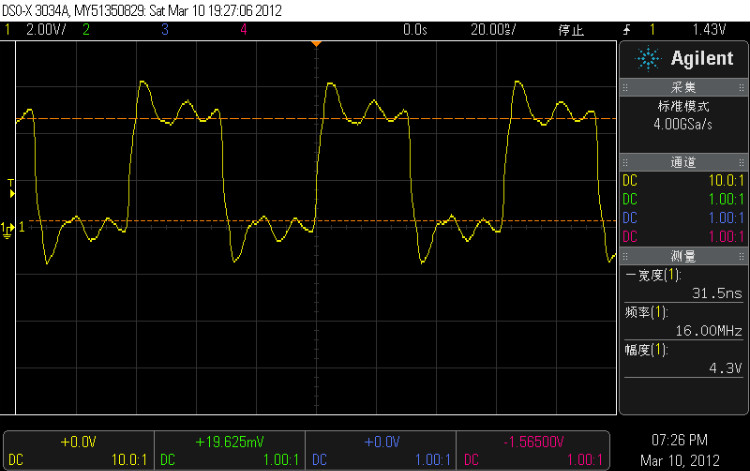

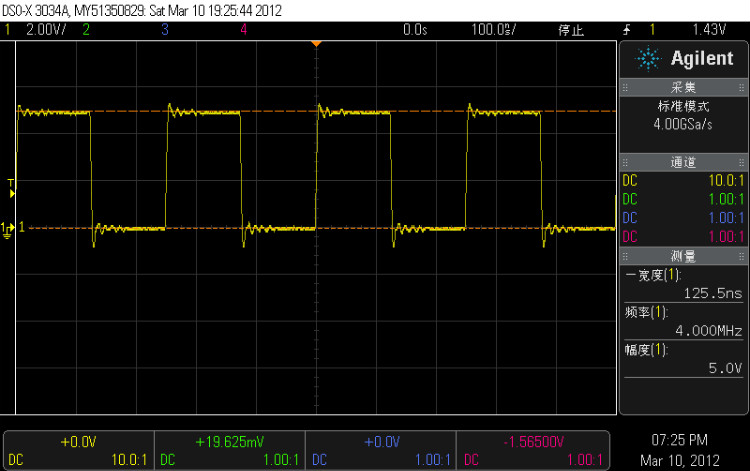

上面的代码设置体系主时钟输出32MHz能够在榜首幅图的CLKOUT端口丈量,在70f3630里是引脚"PCM1",可编程输出时钟输出为8MHz在70f3630里是引脚"P9_13"引脚。下面两幅图是用示波器丈量的成果作为佐证:

最终弥补一点: