今日的便携式设备经过继续的活动监测和情境感知来了解周围环境。为了完结这个功用,设备集成了越来越多的传感器和外设,由此发生许多数据。这反过来使得集成更强壮的CPU变得很有必要,以便履行越来越多的核算。一起,有必要缩小规划尺度,下降本钱和功耗,但又不献身终究产品不断提高的功用要求。

传感器中枢(Sensor hub)的概念被越来越多地选用到当今的SoC规划中,以满意“一直运转”的传感器/外设拜访和操控(乃至以高速率)的要求,而且不会增加功耗和规划本钱。传感器中枢可所以小型CPU内核,与传感器/外设衔接,并经过履行后台操作并仅在需求时“唤醒”主处理器,充任功耗较大的主处理器的卸载引擎的人物。

用于传感器搜集的依据处理器的典型架构

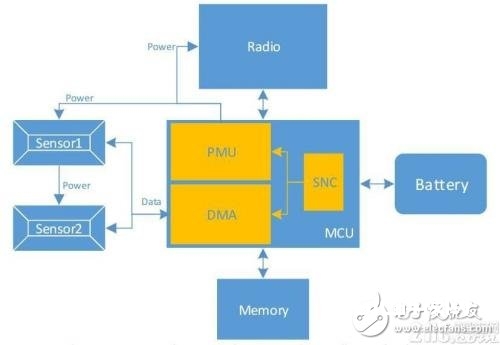

运用在集成多个传感器的体系中的典型依据微操控器的架构包含以下组件[1]:

a) 一个微操控器单元(MCU) – 也称为处理子体系,MCU操控体系内一切构成部分的运转并处理数据。它包含一个处理器、一个内部或外部存储器、以及本地数据处理所需的一切外设和子体系。在典型的依据MCU的架构中,操控器履行一切传感器数据搜集、处理和存储。

b) 传感器元件(或传感子体系) – 一组传感器,可所以无源或有源,数字或模仿的恣意组合。这些传感器将来自外部环境的输入信息转换成电信号。在大多数运用中,传感器用于监测运动、光、气压、振荡、流速、温度、通风、电等。一般来说,传感器元件在其输出端生成电压或电流信号。在数据被处理、存储和传输之前,这些信号一般会被扩大,并经过模数转换器转换成数字信号。

c) 无线电 – 一种短距离收发器,供给与主机的无线通讯。

d) 电源子体系 – 一般衔接到电池或能量搜集器。该子体系充任可控单元,可独自翻开和封闭体系构建块的电源。它一般是MCU软件中的一个软件块。电源子体系担任为每个独自的硬件组件供给适宜的电源电压。

在具有多个传感器的更杂乱的依据微操控器的架构中,在硬件中集成了智能,用来操控各种子体系。 例如,从传感器到存储器传输数据耗时又耗电,这一部分作业其实能够从处理器转移到直接内存存取(DMA)单元。电源办理单元(PMU)还能够被编程为对特定事情做出反响并封闭各种子体系,例如外设、传感器和无线电。

图1. 依据微操控器的典型架构

这种先进架构的意图是尽或许削减主MCU活泼的时刻。本来需求MCU干涉的使命,现在能够由智能子体系履行。但是,还存在一个问题,便是每次有来自传感器、无线电或各种子体系的事情时,MCU都需求被唤醒,由于它是仅有能够布置逻辑来处理这些事情的元件。

优化功率的技能 – 增加传感器节点操控器

为了延伸具有多个传感器的体系的续航时刻,现已提出了许多种下降功耗的技能[2],[3]。有些技能在媒体拜访操控层面进行节能[4]

[5],有些技能从数据聚合或交融着手[6],[7],有的则选用芯片规划优化技能,如片上功率门控[ 8]或动态电压调理[9]。

本文介绍了一种不同的技能,来优化多传感器体系中的电源运用,一起将主处理器用于数据搜集的唤醒时刻操控到最短。该技能依据集成杂乱的硬件状况机,能够接收主处理器上的重复性使命,如传感器轮询和读取,然后完结集成的低功耗传感器中枢概念。专用硬件状况机能够更快地唤醒,并运用更少的模块来将数据从传感器/外设传输到内存,以及反向传输,而主处理器坚持休眠状况。此外,传感器中枢能够对数据履行简略操作,因而主处理器只需求在要求杂乱数据操作时唤醒。

这种办法的一个很好的比如,是集成在Dialog半导体公司的DA1469x蓝牙低功耗SoC处理计划中的传感器节点操控器(SNC)硬件模块[10]。SNC是一种微型硬件状况机,能运转由有限的指令集组成的微码(μcode),有助于开发人员操控通讯操控器(即SPI、I2C等)、传感器和外设。它能够经过运用其最小指令集主动运转,无需唤醒体系的其余部分。这答应它履行许多操作 – 例如:轮询传感器状况位、比较寄存器与内存地址内容(值)、将数据从通讯接口传输到体系RAM以及比较分支 – 一起耗费最低电流。

图2. 具有传感器节点操控器外设的运用处理器架构

SNC的首要特性如下(图3):

传感器节点指令集(SeNIS),包含10条微码生成指令,适用于

o 轻松创立指向内存缓冲区的指针

o 轮询串行接口状况位

o 比较阈值

体系RAM用于微码存储和数据

DMA功用,用于将数据直接从通讯接口传输到体系RAM

直接拜访一切外设和寄存器

经过PMU在中止触发和域上电(例如定时器、GPIO)后当即履行

SNC到主处理器告诉,以及反向告诉

SNC与一切通讯接口(SPI、I2C和UART)坐落相同的电源域,SNC还能够操控其他电源域。它履行驻留在体系RAM中的微码,其间SNC具有直接内存衔接;以体系时钟速度运转;而且能够生成中止以告诉PMU一切操作都已完结,然后能够封闭整个体系的电源。

图3. 传感器节点操控器框图

运用此类专用硬件履行传感器和外设数据操作的架构的首要长处是:

主CPU睡觉时刻更长,然后能够节约功耗

节约MIPS,由于CPU不用拜访慢速外设或履行简略的数据操作

不过它有一些缺陷。SNC编程模型的十分简略的指令集仅答应根本操作。别的,编程SNC需求运用汇编言语。最终,由于SNC是一个十分简略的模块,调试会变得杂乱。

节约功耗和MIPS

咱们现已进行了一系列丈量,证明了运用SNC能够完结的功耗和MIPS节约。这些丈量是在Dialog的依据ARM Cortex-M33的DA1469x SoC上进行的,并比较了只运用主CPU和在SNC支撑下履行的相同使命。 第一组丈量会集在拜访一般用于传感器读数的慢速外设(如I2C和SPI)时节约的功耗/MIPS。第二组丈量着眼于运用DA1469x中包含的蓝牙低功耗(BLE)通讯模块的实践运用事例。

与CPU(CM33)比较,SNC履行业务所需的时刻要短许多,如表2所示。由于CPU或许需求履行忙等候,因而节约了时刻相当于节约了MIPS。

时长 (μs)

CS-写 写 写-读 读 读-CS 总计 时刻差异

SNC 13.98 26.1 16.68 209.64 5.5 271.9

(8-bit 形式SPI)

CM33 46.96 18.06 139.18 145.04 87.3 436.5 60.50%

(DMA, 有适配器)

对现实生活中的运用事例,咱们比较了每隔1500毫秒(表3)和500毫秒(表4)进行播送时所耗费的功率,一起运用SPI每100毫秒读取加快计传感器一次。

表3:每1500毫秒进行播送时的能耗,运用SPI每100毫秒进行一次传感器读取

播送 (每1500 ms) & 传感器读取每 100 ms – 进行15 秒 电流耗费 (μC) 节约

SNC 223.6

CM33 374.8 40.30%

表4:每500毫秒进行播送时的能耗,运用SPI每100毫秒进行一次传感器读取

播送 (每500 ms) & 传感器读取每 100 ms – 进行15 秒 电流耗费 (μC) 节约

SNC 255.6

CM33 406.8 37.20%

在杂乱的运用中,假如需求拜访多个传感器,考虑到缓存未命中和使命切换等问题,对MCU的占用会更大。

下降编程杂乱度

上面提到过,运用集成的传感器节点操控器时面对的最大应战之一,是保证根底体系功用的编程、调试和充分运用与选用通用MCU的计划相同简略。应战的首要方面有:

供给对开发人员友爱的笼统编程,以有用操控驱动与衔接的传感器/外设的通讯接口,以及与主CPU通讯相对应的根本功用。

运用10指令汇编式编程,并供给更高等级的编程结构,以简化和加快软件开发。

支撑完好的体系全体调试 – 而不是独自调试每个CPU内核,由于或许无法检测到当内核并行运转时的体系行为过错。

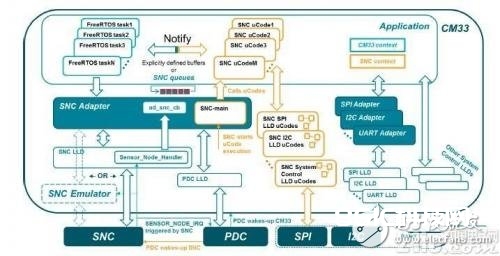

为了处理这些应战,咱们需求一个完好、易于运用的编程结构。它有必要包含笼统和程序,将并发操作体系使命的典范扩展到在SNC上履行的相应(并行)处理。咱们现已为Dialog DA1469x处理计划开发了这样的编程结构(图4)。它具有以下特色:

简化的SNC微码开发

o 经过界说依据SeNIS的类C编程言语,能够一起支撑汇编和类C编程。

用于编程的“混合”编码模型

o 在相同的源和头文件中一起包含针对SNC和主处理器情境(context)的代码开发 – 运用了一个C预处理器来界说依据SeNIS的言语结构,便利开发人员。

与驱动主处理器通讯接口、交流SNC告诉、和操作体系资源相关的根底机制和功用的笼统,作为一组完好且易于运用的API程序/类C函数。

图4. SNC编程结构

SNC编程模型的特征可归纳如下:

DA1469x运用包含由OS使命和SNC 微码并行履行的进程。

SNC适配器向DA1469x体系注册或刊出SNC微码,然后创立一列SNC微码,每个微码由特定PMU事情触发。

SNC适配器选用特别的SNC微码,依据相应的微码列表完结注册的SNC微码履行的调度,并经过其初级驱动器操控SNC硬件模块。

界说了一组依据SeNIS的结构预处理器宏,然后生成一组汇编和类C言语结构用于SNC微码开发。

供给一组初级驱动器SNC微码,可用于驱动SPI、I2C等通讯外设。

为操作体系使命和SNC微码供给了一种机制,进行交流:

o 告诉

o 数据(即:SNC 行列)

除了上述完结轻松编程SNC函数的结构之外,还供给以下内容以支撑调试:

运用SNC断点和逐渐调试区域来调试SNC微码的机制。

SNC仿真器,而不是SNC硬件模块,用于改善和简化SNC微码调试进程。

总结

本文介绍了一种新的架构,可最大极限地下降集成了多个传感器和外设的便携式体系的功耗。该架构运用杂乱的硬件状况机来卸载主处理器上的一些重复性使命,例如传感器/外设轮询和读取。与其他架构比较,这种新架构在功耗和MIPS优化方面具有很大的优势,不过会使编程模型变的更杂乱。因而,咱们还介绍了一种对开发人员友爱的编程结构来战胜该问题。

来历;互联网