在许多高速数据收集体系中,数据正确锁存是规划者必需求面临的问题。特别是在内部时钟与外部时钟选用同一个时钟源的依据FPGA的高速数据收集体系中,因为走线延时、器材延时、FPGA输入管脚延时,导致FPGA输入数据与FPGA内部时钟的相对相位联系不确定;在时钟频率可变的状况下,相对相位联系还会随频率改动。在FPGA内部一般选用D触发器完成对输入数据的采样。为了避免亚稳态 ,D触发器要求输入数据相对时钟沿满意必定的树立、坚持时刻,即输入数据与FPGA内部时钟要满意必定的相位联系。因为输入数据与采样时钟相对相位的不确定性,就有或许不满意FPGA内部D触发器的树立、坚持时刻,呈现亚稳态。针对上述状况,本文给出在FPGA中能够自习惯地挑选时钟上升沿或下降沿采样的自习惯同步器电路规划。该电路能够检测锁存时钟上升沿与输入数据跳变的相位联系,由检测成果挑选上升沿采样或下降沿采样,使数据改动避开时钟沿的亚稳态窗 ,下降呈现亚稳态的概率。

1 某雷达数据收集体系简介

图1所示为某雷达体系数据收集原理图,该雷达体系有两种带宽,要求两种采样频率,采样时钟由FPGA发生。规划选用了ECL输出电平规范的ADC,FPGA输入输出选用LVTTL规范。因而,FPGA输出时钟以及ADC数据送入FPGA均需求选用电平转化芯片。这样,FPGA输出时钟的上升沿到相应FPGA输入管脚上升沿之间(图1中C点到D点)有8~9ns的延时。相同的延时,不同的采样频率,输入数据与采样时钟的相对相位不同;并且因为FPGA内部布线延时的不确定性,采样时钟与输入数据的相对相位会跟着每次从头布局布线而改动,这两种状况都或许导致不满意D触发器的树立、坚持时刻,导致采样失效。

如图2所示,在FPGA内部若选用上升沿锁存数据,关于115MHz采样频率能够确保正确采样,关于85MHz的采样频率,有或许呈现采样失效;反之,若选用下降沿锁存数据,115MHz的采样频率或许呈现采样失效。

处理上述问题的难点在于猜测输入数据与采样时钟的相位联系,然后挑选适宜的采样时钟沿。选用图1所示的采样计划,经常呈现某一种采样频率采样失效的状况,如115MHz采样频率采样正常,而85MHz采样频率采样失效。自习惯同步器能够猜测采样时钟与输入数据的相位联系,自习惯地挑选上升沿或下降沿采样,下降呈现亚稳态的概率。

2 自习惯同步器原理

自习惯同步器能够猜测采样时钟上升沿与输入数据的相位联系。假如相位联系不能满意D触发器的树立、坚持时刻,则自习惯同步器能自习惯地对数据或许时钟作延时调整,直到满意树立、坚持时刻。

依据同步器延时调整目标不同,同步器能够分为时钟延时同步器和数据延时同步器。下面给出两种同步器的完成原理。

2.1 时钟延时同步器

图3所示为时钟延时同步器,抵触检测电路检测输入数据与时钟沿的相位联系,依据检测成果由状况机自习惯挑选时钟是否延时。图3中时钟延时单元可完成时刻为T的延时,延时单元若为一非门,该电路便是一个简略的时钟上升沿采样或许下降沿采样的自习惯挑选电路。

该电路具有相对简略、简单完成的特色。可是因为时钟延时只要两种挑选,不或许完成相位的准确匹配,很难习惯一些超高速电路的需求。该电路一般选取数据总线中的某一位做相位匹配,因而要求数据总线上各位数据延时尽或许持平。

2.2 数据延时同步器

图4所示电路为数据延时同步器,输入数据通过若干级延时单元的延时,抵触检测电路检测时钟上升沿与各级延时数据的相位联系,由状况机挑选较为抱负的延时数据。

数据延时同步器能够完成对数据的准确延时,完成对超高速数据或DDR数据的锁存。可是,因为许多延时单元的运用,增加了FPGA规划的杂乱度,完成较为困难。

3 自习惯同步器在采样体系中的使用

图5所示电路为自习惯同步器在图1所示的某雷达采样体系中的使用。图5中采样时钟、D触发器组与图1中相同,仅仅图5中D触发器组的时钟改为同步时钟,BUFG为Xilinx FPGA内部的大局时钟缓冲。自习惯同步器检测同步时钟与数据最低位data[0]的相对相位,自习惯地挑选采样时钟,到达同步输入数据的意图。因为数据总线只选取其间一位data[0],因而要求总线上各位数据延时尽或许持平。

4 自习惯同步器的FPGA完成

数据延时同步器完成较为杂乱,特别关于位数较多的数据总线,需求占用许多资源,状况机也较杂乱。但其完成原理与时钟延时同步器根本相同,本文只给出时钟延时同步器的完成。图6所示电路为自习惯同步器,其间del为延时单元,延时时刻计为T_del;me_p为data上升沿与时钟上升沿的抵触检测模块,me_n为data下降沿与时钟上升沿的抵触检测模块;fsm为有限状况机。当data跳变发生在时钟上升沿[-T_del,T_del]时刻之内时,电路输出sel有用。

4.2 突检测单元me_p,me_n的完成

图8为抵触检测单元me_p的原理图。该电路能够完成两路输入信号上升沿的相位检测,假如输入信号r1上升沿较r2的上升沿提早,则g1输出为‘1’,g2为‘0’;不然g1输出为‘0’,g2为‘1’。在FPGA完成时,选用依据四输入查找表(LUT4)的规划,关于布局布线要尽或许坚持对称性,需求参加布局束缚、乃至布线束缚。图9为经Synplify归纳后的原理图。

抵触检测单元me_n能够完成输入信号r1下降沿与输入信号r2上升沿的相位检测,原理同me_p。关于me_n的完成,只要在装备FPGA查找表(LUT)时,将图9中I0单元(LUT4_7FFF)改为“LUT4_DFFF”即可。

4.3 状况机的完成

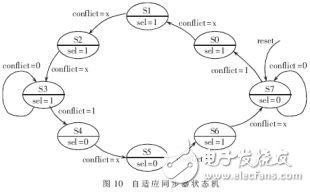

图10为自习惯同步器状况机,输入为conflict,输出为sel。状况机共8个状况,状况为S0、S1、S2、S3时,输出为‘0’,挑选图(5)所示‘sam_clk’;不然输出为‘1’,挑选‘sam_clk’的反向时钟‘~sam_clk’;中心态S0、S1、S2以及S4、S5、S6能够有用避免状况机振动。图10中′x′表明恣意状况。

上述自习惯同步器已通过图1所示的雷达采样体系的验证。采样频率在20MHz到140MHz规模内改动时,未呈现采样失效。

4.1 延时单元的FPGA完成

图7为延时单元电路,选用FPGA内部的LUT4作延时。因为FPGA内部布线延时与LUT4延时比较不行疏忽,因而需求对LUT4作相对布局束缚,必要时还要作布线束缚。