在28nm技能打破的根底上,赛灵思又宣告推出根据20nm节点的两款业界创始产品。赛灵思是首家推出20nm商用芯片产品的公司。此外,该新式器 件也是赛灵思将向商场推出的首款选用UltraScale®技能(可编程工业的首款ASIC级架构)的产品。UltraScale架构充沛发挥 Vivado®规划套件中顶级EDA技能的优势,使客户可以快速展开新一代All Programmable立异。在28nm节点上,赛灵思在业界首要推出Zynq®-7000 All Programmable SoC 和 Virtex®-7 3D IC两款产品。此举将持续坚持赛灵思从28nm工艺节点开端抢先竞赛对手整整一代水平的优势。

赛灵思商场营销和企业战略高档副总裁Steve Glaser指出:“赛灵思是首家推出28nm器材的公司,在20nm工艺节点上,咱们持续坚持业界最活跃的的产品投片计划。咱们的尽力再次获得报答,赛 灵思在高端器材上远远抢先竞赛对手至少一年的时刻,而在中端器材上则至少抢先半年左右。”

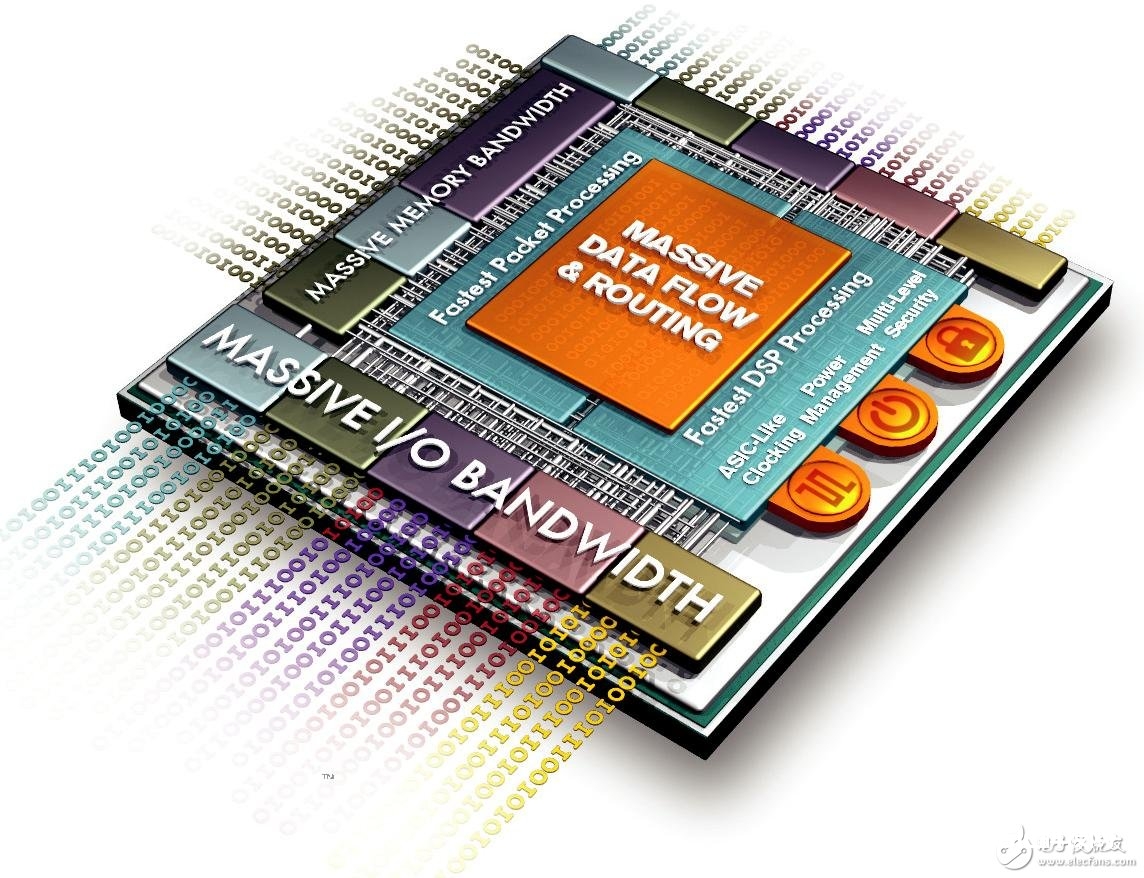

与28nm技能节点相同,赛灵思在推出的新产品组合中也完成了一些业界创始的技能立异。首要,公司推出了新一代UltraScale架构,该架构将 选用20nm、16nm FinFET甚至更先进的工艺。Glaser表明:“这是业界首款可协助用户经过All Programmable器材完成ASIC级规划的可编程架构。UltraScale架构使得赛灵思推出的20nm和16nm FinFET All Programmable可以供给海量I/O和存储器带宽,支撑最快速的包处理和DSP处理、相似ASIC的时钟、电源办理和多级安全性。”

架构优势

UltraScale架构包含数百种结构改善,可是假如没有开宣布Vivado 规划套件,其间的许多改善都是无法完成的。Vivado 规划套件为赛灵思客户供给了高档EDA东西功用,比方说Vivado的高档布局布线功用,能协助用户全面发挥UltraScale的海量数据处理功用,使 得规划团队能将UltraScale的使用率提高到90%以上,并且还能满意严厉的功用和功耗要求。如此高的使用率大大超过了同类竞赛产品所能到达的水 平,竞赛产品现在还要求用户献身功用来进步使用率,这就使得客户不得不选用厂商更大型、更贵重的器材,效果他们却发现需求怠慢时钟速率来满意体系功耗要 求。

在28nm工艺节点上,这一问题已不复存在,这要归功于赛灵思的布线架构。在20nm工艺节点上,这也不会构成问题,由于UltraScale架构 可以针对宽总线完成海量数据流,来协助客户开宣布具稀有Tb吞吐量和最低时延的体系。与Vivado协同优化的UltraScale架构能经过高度优化的 要害途径与内置高速存储器级联来消除DSP和包处理的瓶颈问题。增强型DSP子体系将要害途径优化与新式27个18位乘法器和两个加法器相结合,可明显提 升定点及IEEE-754浮点运算的功用与功率。宽存储器完成计划也适用于UltraScale 3D IC,明显改善了晶片间带宽,然后进步了全体功用。

图1 – UltraScale架构能供给海量I/O和存储器带宽,支撑最快速的包处理和DSP处理、相似于ASIC的时钟、电源办理和多级安全性。

一般仅见于ASIC级产品中的多区域时钟技能使规划人员可以在其体系中构建出高功用低功耗且时钟倾斜极低的时钟网络。

UltraScale器材对I/O和存储带宽做了进一步改善,包含支撑新一代存储器衔接,能大幅下降时延并优化I/O功用。该架构供给了多个硬化ASIC级IP核,包含10/100G以太网、Interlaken和PCIe®。

UltraScale架构还支撑多区域时钟,该特性一般仅见于ASIC级产品中。多区域时钟能使规划人员可以在其体系中构建出高功用低功耗且时钟歪 斜极低的时钟网络。UltraScale架构和Vivado的协同优化也能让规划团队针对赛灵思20nm All Programmable产品的更多不同功用元件选用更丰厚的电源门控技能,然后进一步下降功耗。

最终但相同重要的是,UltraScale还支撑经过AES比特流解密与认证、密钥含糊处理以及安全设备编程等高档方法来完成业界一流的体系安全性。

专门要害商场量身定制

Glaser指出,规划团队使用UltraScale器材可完成更高的体系集成度,一起最大化全体体系功用,下降全体体系功耗以及体系的总资料清单 本钱。他说:“最初FPGA仅被视为很好的逻辑器材替代品,可是赛灵思以其在28nm工艺节点上所获得的效果为根底,持续使用20nm和FinFET 16/14工艺提高All Programmable技能的价值,使其远远逾越了最初人们关于FPGA产品的价值预期。咱们共同的体系价值在多种不同使用中都得到了杰出表现。”

Glaser指出,选用赛灵思20nm和16nmFinFET UltraScale架构的器材能充沛满意不断涌现的多种不同细分商场需求,例如光传输网络(OTN)、网络高功用核算、数字视频和无线通信等(参见图 2)。所有这些范畴都必须满意越来越多对产品功用、本钱、低功耗和大规模集成的要求。

图2 – UltraScale架构将加快下一代不同类型体系的开发,尤其是有线和无线通信范畴的体系开发