文章转自ADI官网,版权归属原作者一切

简介

传统收发器规划中,50 Ω单端接口广泛用于射频和中频电路。当电路进行互连时,应悉数具有匹配的50 Ω输出和输入阻抗。然而在现代收发器规划中,差分接口常用在中频电路中以取得更好的功能,但实践规划进程中,工程师需求处理几个常见问题,包含阻抗匹配、共模电压匹配以及杂乱的增益核算。了解发射机和接纳机中的差分电路对优化增益匹配和体系功能很有协助。

差分接口优势

差分接口有三大首要优势。首要,差分接口可按捺外部搅扰和接地噪声。其次,它能够按捺偶次阶输出失真。这关于零中频(ZIF)接纳机非常重要,由于出现在低频信号中的偶次阶成分无法滤除。第三,输出电压可到达单端输出的两倍,然后将给定电源上的输出线性度进步6 dB。

本文论说三种情况下的接口解决计划:ZIF接纳机、超外差式接纳机和发射机。这三种架构广泛用于射频拉远单元(RRU)、数字直放站和其他无线测验仪器中。

ZIF接纳机接口规划和增益核算

在零中频(ZIF)接纳机规划中,IF信号是复信号,直流和低频率信号来供给有用信息。典型解调器在驱动200 Ω至450 Ω负载时可供给最佳功能,一起ADC驱动器的输入阻抗一般并非50 Ω,因而规划体系时选用直流耦合很重要也很困难。

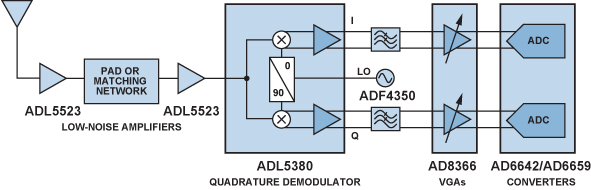

图1显现了一个ZIF接纳机装备,它运用两个低噪声放大器(LNA) ADL5523一个400MHz至6000MHz正交I/Q解调器ADL5380 一个作为本振(LO)的宽带频率合成器ADF4350以及一个双通道数字可编程可变增益放大器(VGA)AD8366 表1显现了相关ADL5380接口和增益参数。

表1.ADL5380接口和增益参数

| 测验条件 | VS = 5 V, TA = 25°C, fLO = 900 MHz, fIF = 4.5 MHz, PLO = 0 dBm, ZIN = 50 Ω |

|

| 参数 | 值 | 补白 |

| 电压转化增益 | 6.9 dB | I和Q输出上具有 450 Ω差分负载 |

| 5.9 dB | I和Q输出上具有 200 Ω差分负载 | |

| 共模输出电压 | 2.5 V | ADJ衔接至 VS |

| 差分输出阻抗 | 50 Ω | |

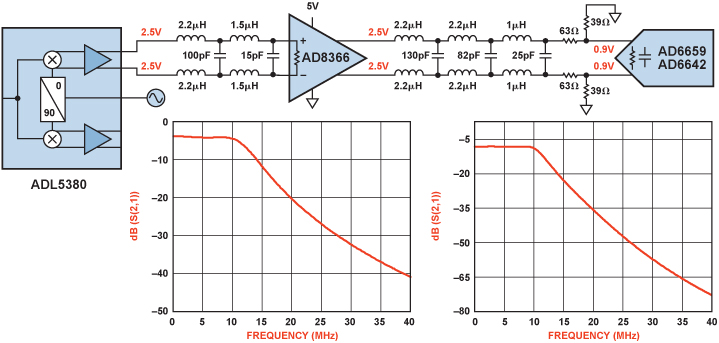

与具有217 Ω差分输入阻抗的AD8366接口时,ADL5380具有5.9 dB电压增益和–0.5 dB功率增益[5.9 dB – 10log (217/50)]。为取得最佳功能,将ADL5380 ADJ引脚衔接至VS,使ADL5380与AD8366间的共模电压设置为2.5 V。在ADL5380与AD8366间放置具有0.5 dB刺进损耗的差分四阶巴特沃兹低通滤波器,以便按捺噪声和高频搅扰成分。尽管滤波器会输入和输出阻抗并不匹配,但在基带频率下这些不匹配是能够疏忽的。

表2.AD8366接口和增益参数

| 测验条件 | VS = 5 V, TA = 25°C, ZS = 200 Ω, ZL = 200 Ω, f = 10 MHz |

|

| 参数 | 值 | 值 |

| 电压转化增益 | 4.5 dB | 最小数字增益设置 |

| 20.25 dB | 最大数字增益设置 | |

| 共模输出电压 | 1.5 V | 最小值 |

| 2.5 V | 最大值或输入自偏置 | |

| 差分输入阻抗 | 217 Ω | |

| 共模输出电压 | 1.6 V | 最小值 |

| 3 V | 最大值 | |

| 2.5 V | VCMA和VCMB 坚持浮空 | |

| 差分输出阻抗 | 28 Ω | |

| 线性输出摆幅 | 6 V p-p | 1 dB增益紧缩 |

AD8366的共模输出电压可设置为2.5 V;当VCM坚持浮空时其线性度最佳。惋惜的是,AD6642在0.9 V共模输入电压(0.5 × AVDD)下具有最佳功能。由于AD8366的共模输出电压有必要介于1.6 V与3 V之间,因而AD6642 VCM和AD8366 VCM引脚无法直接衔接,有必要运用电阻将AD8366共模输出电压分压至0.9 V。

为取得最佳功能,AD8366应驱动200Ω载。要完成所需的共模电平缓阻抗匹配,可在AD8366后增加63 Ω串联电阻和39 Ω并联电阻。这一电阻网络将使信号功率衰减4 dB。

AD8366的输出摆幅可达6 V p-p,但电阻网络供给的4 dB衰减使AD6642得到的电压限于2.3 V p-p,避免了较大搅扰尖峰或增益的失控对ADC带来危害。

在AD8366与AD6642间放置具有1.5 dB刺进损耗的差分六阶巴特沃兹低通滤波器,能够滤除高频搅扰成分。I或许Q通道的完好差分接口如图2所示。

为保存满足的余量来敷衍整个温度规模内的增益改动,AD8366在正常形式下的增益设置为16 dB。

选用这种装备,整个信号链的增益如下:

5.9 dB – 10log (217/50) – 0.5 dB + 16 dB – 10log (200/217) – 1.5 dB – 4 dB

= 9.9 dB.

在ADL5380之前以级联方法刺进的两个LNA完成了32 dB的射频增益。由于模数转化器被装备为2 V p-p满幅摆幅和78 Ω等效输入阻抗,它能够接纳最大–34 dBm的单音RF输入信号。假如输入信号是具有10 dB峰均比(PAR)的调制信号,在不改动VGA设置情况下,接纳机能够接纳的最大输入信号为-41dBm。

换言之,电压增益可用于核算信号链链路预算。当输入端口阻抗等于输出端口阻抗时,电压增益等于功率增益。整个信号链的电压增益为:

32 dB + 5.9 dB – 0.5 dB + 16 dB – 1.5 dB – 8 dB = 43.9 dB.

关于单音信号输入,要取得2 V p-p摆幅规模,正确的输入功率为:

8 dBm – 43.9 dB + 10log (78/50) = –34 dBm.

用电压增益核算的成果与功率增益核算出成果是相同的。

某些运用中,ADL5380或许需求直接衔接至AD6642,这种情况下,可为AD6642差分输入增加500 Ω电阻以改进匹配。ADL5380电压增益为6.9 dB,且具有与AD8366相同的共模问题。所以应运用160 Ω串联电阻和100 Ω并联电阻来完成500 Ω负载和所需的共模电压。相同,电阻网络可将电压增益衰减8 dB(功率则衰减4 dB)。

在ADL5380与AD6642间放置具有1.5 dB刺进损耗的低通滤波器,然后滤除搅扰频率成分。整个链路的输入阻抗为50 Ω,输出阻抗为500 Ω。选用这种装备,整个信号链的增益如下:

6.9 dB – 10log (500/50) – 1.5 dB – 4 dB = –8.6 dB.

超外差式接纳机接口规划和增益核算

超外差式接纳机规划中,体系运用沟通耦合,因而规划超外差接纳机电路时不用考虑直流共模电压匹配。

许多混频器,例如ADL535x和ADL580x,具有200 Ω的差分输出阻抗,因而不同输出阻抗出现不同功率增益和电压增益。

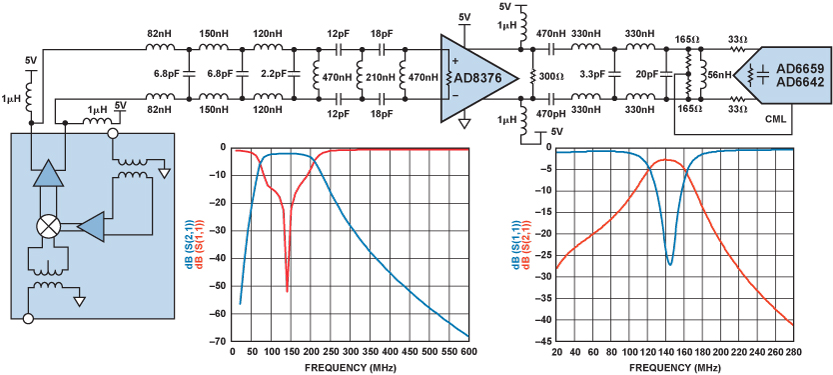

图3显现了超外差式接纳机的一个通道,该器材选用以下元件:低噪声放大器ADL5523 具有LO缓冲器、IF放大器和RF巴伦的双通道平衡混频器ADL5356 带通或许低通滤波器;双通道、超低失真IF VGAAD8376 另一个低通或许带通抗混叠滤波器;双通道IF接纳机AD6642

该规划运用140MHz 中频和20MHz带宽,因而器材衔接时可选用沟通耦合。

AD5356在200 Ω负载下具有最佳功能,而AD8376的输入阻抗为150 Ω。因而,为了按捺混频器输出杂散并供给杰出的阻抗匹配,差分LC滤波器有必要具有200 Ω的输入阻抗和150 Ω的输出阻抗。在某些运用中,需求经过过渡带极窄滤波器按捺频带外信号,可运用差分SAW滤波器来完成,但这会给接纳机信号链引进过大的损耗和群推迟。四阶差分带通巴特沃兹滤波器可合适许多无线接纳机,由于前端RF滤波器能够为带外搅扰供给满足的衰减。

表3. ADL5356和AD8376接口和增益参数

| ADL5356 测验条件 | VS = 5 V, TA = 25°C, fRF = 1900 MHz, fLO = 1760 MHz, LO功率 = 0 dBm |

|

| 参数 | 值 | 补白 |

| 电压转化增益 | 14.5 dB | ZSOURCE = 50 Ω, 差分 ZLOAD = 200 Ω 差分 |

| 共模输出电压 | 2.5 V | ADJ 衔接至 VS |

| 功率转化增益 | 8.2 dB | 包含4:1 IF端口变压器和PCB损耗 |

| AD8376 测验条件 | VS = 5 V, TA = 25°C, RS = RL = 150 Ω(140 MHz时) | |

| 参数 | 值 | 补白 |

| 差分输入电阻 | 150 Ω | |

| 电压转化增益 | –4 dB | 最小数字设置 |

| 20 dB | 最大数字设置 | |

| 输出阻抗 | 16 kΩ || 0.8 pF | |

AD8376的电流输出型电路具有高输出阻抗,因而其差分输出需求接150 Ω电阻完成电压输出。另一个差分滤波器放置在AD8376和ADC之间,用于衰减二阶和三阶谐波失真成分,因而该150 Ω负载能够被分红两部分。首要将300 Ω电阻装置于AD8376的输出端。另一个300 Ω电阻由两个165 Ω电阻和ADC的3 kΩ输入阻抗构成。两个165 Ω电阻一起为ADC输入供给直流共模电压。LC滤波器的输入和输出阻抗均为300 Ω。关于高中频运用,信号源和负载的阻抗的完美匹配是非常重要的。完好接口如图4所示。

此接纳机中,混频器之前放置一个20 dB LNA。混频器之后的滤波器具有2 dB刺进损耗;AD8376与ADC之间的滤波器具有1.2 dB刺进损耗。AD8376增益设置为14 dB,以便供给满足的余量来应对温度改动。接纳机的整体增益为:

20 dB + 8.2 dB – 2 dB + 14 dB – 1.2 dB = 39 dB.

为将ADC输入电压约束在2 V p-p以下,传输到150 Ω电阻(300 Ω || (165 Ω × 2) || 3 k Ω)的功率应小于5.2 dBm。因而关于单音信号,接纳机最大输入功率为–33.8 dBm。假如输入信号是10 dB PAR调制信号,运用此增益设置的最大输入信号为–40.8 dBm。

发射机接口规划和增益核算

关于发射通道规划,ZIF和超外差式架构具有类似的接口特性,均需求在TxDAC® 与调制器间履行直流耦合。大多数调制器的中频输入电路需求外部供给直流偏置;TxDAC输出可为直流耦合形式下的调制器供给直流偏置。大多数高速DAC是电流输出架构,因而需求外输出电阻才能为调制器发生输入电压。

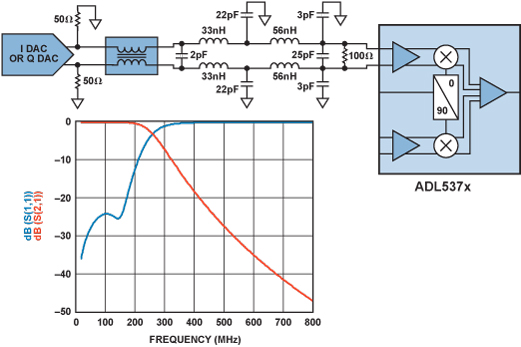

图5显现了超外差式或ZIF发射机,该器材选用以下元件:TxDACAD9122 ,低通滤波器、正交调制器ADL537x另一个RF滤波器、频率合成器ADF4350数字操控VGAADL5243, 功率放大器、用于操控功率放大器(PA)栅极电压的DACAD562x.

关于AD9122,满量程输出电流可设置在8.66 mA与31.66 mA之间。关于大于20 mA的满量程电流,无杂散动态规模(SFDR)会变差,但DAC的输出功率和ACPR也跟着满量程电流下降而减小。恰当折衷的计划是将20 mA沟通电流叠加于10 mA直流电平上,得到0 mA至20 mA的电流输出。

表4.AD9122和ADL5372接口和增益参数

| AD9122 测验条件 | AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V |

|

| 参数 | 值 | 补白 |

| 满量程输出电流 | 8.66 mA | 最小数字满量程设置 |

| 31.66 mA | 最大数字满量程设置 | |

| 输出电阻 | 10 MΩ | |

| ADL5372 测验条件 | VS = 5 V, TA = 25°C, fLO = 1900 MHz, fIF = 140 MHz |

|

| 参数 | 值 | 补白 |

| 输出功率 | 7.1 dBm | VIQ = 1.4 V p-p 差分 |

| I和Q输入偏置电平 | 0.5 V | 引荐 |

| 差分输入阻抗 | 2900 kΩ | |

ADL5372的输入电路需求0.5 V共模电压,由流经50 Ω电阻的10 mA直流电流供给。0 mA至20 mA沟通电流由两个50 Ω电阻和一个100 Ω电阻同享。因而调制器输入的沟通电压为20 mA × ((50 × 2) || 100) = 1 V p-p。TxDAC与调制器之间的滤波器用于去除高频杂散和谐波成分。滤波器的输入和输出阻抗为100 Ω。完好接口如图6所示。

选用50 Ω输出时,ADL5372的电压转化增益为0.2 dBm。运用13 dB PAR调制器信号时,均匀功率有必要至少减小15 dB,以便习惯Tx数字预失真进程。ADL5372具有1 V p-p单音输入时,均匀调制器输出功率为7.1 dBm – 2.9 dB = 4.2 dBm。假如考虑低通滤波器的2.2 dB刺进损耗,均匀输出功率为4.2 dBm – 2.2 dB = 2 dBm。这种状态下,调制器输出端均匀输出功率为-10dBm。

为了确保发射链路供给11 dBm均匀发射功率,Tx信号链内后端需求具有26 dBm 的P-1dB的PA驱动器。假如需求2 dB刺进损耗的RF滤波器以按捺LO馈通和调制器边带输出,那么增益模块和PA驱动器有必要供给23 dB的总增益。针对此运用,主张运用具有集成式增益模块、数字操控衰减器和PA驱动器的VGA ADL5243。

结束语

本文介绍了ZIF和超外差式接纳机解调器、IF VGA、混频器和ADC模仿端口差分规划,以及TxDAC与FMOD之间的发射机差分接口,其间均运用ADI器材作为信号链有源部分。别的还供给了规划用于这些电路的运用滤波器的增益核算和仿真成果。本振差分接口规划以及其他相关规划概况请参阅以下参阅文献。

参阅电路

Circuit Note CN-0018, Interfacing the ADL5372 I/Q Modulator to the AD9779A Dual-Channel, 1 GSPS High-Speed DAC.

Circuit Note CN-0134, Broadband Low Error Vector Magnitude (EVM) Direct Conversion Transmitter.

Calvo, Carlos. “The differential-signal advantage for communications system design.” EE Times.