1 导言

卫星数据模仿源是一种能够模仿遥感卫星发生相关卫星数据信号的信号源。首要用于遥感卫星记载体系的体系毛病检测以及新体系开发验证。

当记载体系呈现毛病需求检修时,用模仿的卫星信号替代实在的卫星信号进行体系保护,能够免受卫星过境时刻的影响,使得体系的保护作业更便利。别的,在卫星发射之前,相关记载体系的研发中,模仿源能够作为记载体系的测验信号。

一起跟着遥感技术的广泛运用,遥感卫星数量的不断添加,不同卫星之间的数据存档格局往往不同,其间常常需求进行转化;由于介质寿数有限,关于需求长时间保存得的数据资料,一般需求定时进行介质转化。以上作业也可通过模仿源进行数据回放再存档,存档时挑选不同的存档格局或存档介质,到达格局转化或介质转化的意图。

所以模仿源在地上记载体系中起着十分重要的效果。

2 整体结构

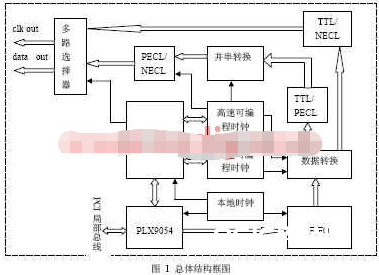

本文规划的遥感卫星数据模仿源的整体结构如图1所示,其首要原理为:从存储设备读取已存档遥感卫星数据或编程生成的特定图画数据,通过PCI总线发送到PLX9054,PLX9054接收到的数据通过数据缓存、并串转化和电平转化等处理构成与实践卫星码速率相同的串行数据流和随同时钟。为了模仿各种不同类型的卫星,模仿源的数据发送频率有必要是可变的,输出规模:1MHz~400MHz,步进为1MHz。

3 要害电路完结

3.1 高速DMA数据发送

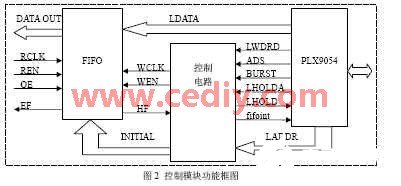

为满意高速的要求,本规划运用插卡方法,且选用PCI总线。PCI接口芯片许多,本文选用PLX公司的PLX9054。PLX9054支撑主/从形式,内置6个128bytes或64bytes的FIFO,两个独立的DMA通道,契合PCI v2.2规范,理论传输速率为132MB/s,满意高速数据传输的要求。为了确保接连的数据发送,Local端运用大容量的FIFO进行数据缓存,这儿运用IDT公司的大容量FIFO——IDT72V36110,巨细为131072 x 36。该FIFO具有独立的读写时钟,五个输出标志位,规划中只用到半满(HF)和空(EF)两个标志位,其间半满标志位用于PLX9054往FIFO写数据,空标志位用于数据转化模块从FIFO读数据。FIFO在运用前有必要先进行初始化,如设置FIFO作业形式,读写数据宽度等,这部分作业由操控电路在体系上电后主动完结,使FIFO一向处于作业状况。

在进行数据发送时, PCI部分总线端发动DMA写数据,每次写数据的巨细为FIFO容量的一半,完毕后即完结一次DMA写数据,假如FIFO中的数据没有被一起往外读,此刻FIFO的半满标志位有用为低电平,空标志位无效为高电平。当然实践运用时,转化模块依据空标志无效,判别FIFO有数据,在PLX9054向FIFO写数据的一起对FIFO进行读数据。当FIFO中数据少于容量的一半时,半满标志位无效为高电平,操控模块立刻通过PLX9054向体系发送中断请求,体系呼应后发动下一次DMA传输。操控模块运用ALTERA公司的MAX3000A系列CPLD——MAX3256A,通过Verilog HDL言语编程完结,其功用框图如上图2所示。

3.2 卫星模仿数据输出

卫星下行数据为串行的差分NECL电平信号,而FIFO中的数据为32位并行TTL电平数据,所以要对FIFO中的数据进行并串转化和电平转化。进行并串转化需求串行时钟信号,为了能够模仿各种不同类型的卫星,串行信号的随一起钟频率有必要是可变的;一起为了习惯遥感卫星的下行数据不断向高速开展的趋势,本规划的最高输出随一起钟为400MHz,总的输出规模:1MHz~400MHz。这个频率规模比较大,用单一的可编程锁相环时钟芯片很难到达。规划中对时钟规模进行了分段,低频部分:1MHz~160MHz,高频部分:160MHz~400MHz,通过两片可编程时钟芯片的组合来完结。

3.2.1 低速可编程时钟

低速可编程时钟选用Cypress公司的可编程锁相环时钟芯片——CY22150,它的输出规模:80Khz~200MHz,且输出频率恣意可编程。它具有低颤动、低畸变、高精度的特色,支撑在体系编程,编程数据通过I2C总线送入时钟芯片。I2C总线有两根传输线,一根时钟线SCLK,一根数据线SDAT,其间数据线SDAT是双向的。I2C体系有它自己的传输协议。一般在体系中都是用单片机体系完结I2C传输协议。由于单片机体系中软件的每条指令的执行时刻都是能够预知的,可严厉的操控好两条传输线的时序联系,能够比较便利的完结I2C协议。可是,在本体系中假如只是由于时钟电路的现场编程而引进单片机体系,会使电路的规划变得很杂乱,并且,加上购买单片机仿真器和编程的费用,整个体系的费用将添加许多。因此在设计时抛弃了这种惯例规划办法。考虑到I2C总线规范对最低码速率没有严厉的要求,测验依托PLX9054的I/O读写,并通过CPLD中的逻辑操控完结模仿I2C总线,用软件的办法依照I2C时序完结时钟芯片的现场编程功用。试验证明,此办法可行。

3.2.2 高速可编程时钟

要完结400MHz的高频,只能挑选ECL器材,规划中选用ON Semiconductor公司的可编程时钟芯片NBC12429,输出规模:25MHz~400MHz,步进为1MHz,实践运用中只用到160MHz~400MHz部分。它也支撑现场可编程,编程方法有两种:并行编程方法和串行编程方法,串行编程方法只需求三根数据线,比并行编程方法需求12根要简略,故选用串行方法。它的编程比CY22150简略,只需求接连地把编程数据写到它的内部寄存器就能够。

3.2.3 数据转化

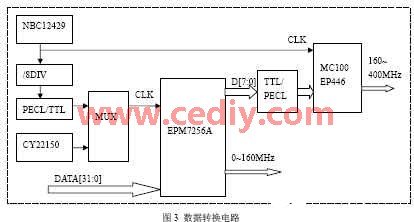

数据转化部分首要完结对FIFO的数据读取以及并串转化,考虑到高速和灵活性,选用Verilog HDL言语编程完结,编程器件运用ALTERA公司的MAX7000A系列CPLD——EMP7256A-5,理论上支撑200MHz的时钟频率,实践运用时通过优化后能到达160MHz。当输出频率为1MHz~160MHz时,串并转化比较简略,直接在CPLD里就能够完结;当输出频率为160MHz~400MHz时,串并转化相对费事些,整个转化分两步完结:先在CPLD里完结32位到8位的转化,然后选用ON Semiconductor公司的高速ECL并串转化芯片——MC100EP446完结8位并行到串行的转化,并且中心要进行一次TTL电平到PECL电平的转化,详细规划方案如图3所示。

3.2.4 电平转化及输出

模仿源的终究输出信号应该是差分NECL电平信号,数据进行并串转化后,有必要进行相应的电平转化,其间低速输出进行TTL电平到NECL电平转化,高速输出进行PECL电平到NECL电平转化,最终通过二选一挑选器输出。

4试验与定论

模仿源选用Windows驱动程序模型(WDM)开发驱动程序,在驱动程序的基础上用VC6.0开发相应的应用软件,包含时钟编程,存档数据发送和棋盘格数据生成并发送等。最终在运用Windows 2000渠道的高性能服务器进步行了卫星存档数据和程序生成的棋盘格数据的发送测验,其间高性能服务器运用双Xeon CPU,1G内存和高速Raid。在发送过程中,和模仿源相连的记载体系进行实时记载,并用示波器对发送频率进行实践丈量。通过不同频率的屡次测验标明,示波器的丈量结果与预订发送频率共同,对记载文件和被发送文件进行的误码率计算结果,也保持在记载体系答应的规模内。以上测验结果标明,此模仿源作业安稳,到达规划要求的性能指标,有用地处理了地上记载体系开发和保护过程中所需的数据源问题。

责任编辑:gt