EnDat接口是HEIDENHAIN专为编码器规划的数字式、全双工同步串行的数据传输协议,具有传输速度快、功用强壮、连线简略、抗干扰能力强等长处,是编码器、光栅尺数据传输的通用接口。本文论述了EnDat接口的特色、功用、时序和数据传输、OEM数据存储,一起介绍了编码器数据收集后续电路规划方案、依据FPGA模块规划的原理和准则。

一概述

肯定式编码器运用天然二进制、循环二进制(格雷码)或PRC码对码盘上的物理刻线进行光电转化,将衔接轴的转动角衡量转化成相应的电脉冲序列并以数字量输出。它具有体积小、精度高、接口数字化及肯定定位等长处,被广泛使用于雷达、转台、机器人、数控机床和高精度伺服体系等许多范畴。肯定式编码器的数据输出以同步串行输出为主,EnDat接口是海德汉专为编码器规划的数字式、全双工同步串行接口。它不只能为增量式和肯定式编码器传输方位值,一起也够传输或更新存储在编码器中的信息,或保存新的信息。因为运用了串行传输方法,所以只需四条信号线,在后续电子设备的时钟鼓励下,数据信息被同步传输。数据类型(方位值、参数、确诊信息等)由后续电子设备发送给编码器的形式指令挑选决议。

二EnDat接口介绍

1.EnDat接口的特色

★高功用低成本:通用的接口适用于一切的增量和肯定式编码器,更经济的电能耗费,小的尺度和紧凑的衔接方法,快速体系装备,零点可依据偏置值起浮。

★更好的信号质量:编码器内部特别的优化进步了体系精度,为数控体系供给更好的概括精度。

★更好的实用性:主动体系装备功用;数字信号进步了体系的牢靠性;监控与确诊信息有利于体系的安全;冗余码校验有利于牢靠的信号传输。

★进步了体系的安全性:两个独立的方位信息及过错信息位,数据的校验和及应对。

★适用于先进的技能开展:(高的分辨率、短的操控周期,最快16M时钟,安全规划理念)适用于直接驱动技能。

图1EnDat接口编码器数据收集原理图

2.EnDat2.2编码器功用的进步

★传输方位值与附加信息可一起传输:附加信息的类型可经过存储地址挑选码挑选。

★编码器数据存储区域包含编码器制造商参数、OEM厂商参数、运转参数、运转状况,便于体系完结参数装备。

★EnDat2.2编码器完结了全数字传输,增量信号的处理在编码器内部完结(内置14Bit细分),进步了信号传输的质量和牢靠性,可完结更高的分辨率。

★监控和确诊功用,报警条件包含:光源失效、信号幅值缺乏、方位核算过错、运转电压太低或太高、电流耗费太大等;当编码器的一些极限值被挨近或超过期供给正告信号。

★更宽的电压规模(3.6~14V)和传输速率(16M)。

3.时序和OEM数据存储

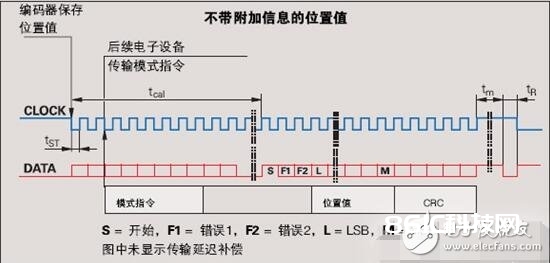

在每一帧同步数据传输时一个数据包被发送,传输循环从时钟的第一个下降沿开端测量值被保存,核算方位值。在两个时钟脉冲(2T)后,后续电子设备发送形式指令“编码器传输方位值”(带或不带附加信息)。

在核算出了肯定方位值后(tcal——-见图2),从开端位开端编码器向后续电子设备传输数据,后续的过错位F1和F2(只存在于EnDat2.2指令中)是为一切的监控功用和毛病监控服务的群组信号,他们的生成彼此独立,用来表明或许导致不正确方位信息的编码器毛病。导致毛病的切当原因保存在“运转状况”存储区,能够被后续电子设备查询。

从最低位开端,肯定方位值被传输,数据的长度由运用的编码器类型决议。传输方位值所需的时钟脉冲数保存在编码器制造商的参数中。方位值数据的传输以循环冗余检测码完毕。

图2无附加信息的方位值传输

方位值假如带附加信息,紧接在方位值后的是附加信息1和2,他们也各以一个CRC完毕。附加信息的内容由存储区的挑选地址决议,然后在后面的采样周期里被传输。在后续的传输中一直传输该信息,直到新的存储区被挑选。在数据字的结束,时钟信号有必要置高电平。10us到30us或1.25us到3.75us(EnDat2.2可编程的恢复时刻tm)后,数据线回到低电平,然后,新的数据传输可在新的时钟信号下开端。

图3带附件信息的方位传输

一起,编码器为参数供给了不同的存储区,它们能够被后续电子设备读取,这些区域能够被编码器制造商、OEM厂商乃至最终用户写入。一些特定的区域是能够被写保护的。不同系列的编码器支撑不同的OEM存储区和不同的地址规模。因而,每一个编码器有必要读取OEM存储区的分配信息。依据此原因,后续电子电路应依据相对地址编程,而不能运用肯定地址。

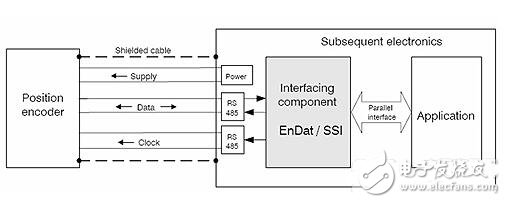

三EnDat接口后续电子设备的电路规划方案

运用者能够依据EnDat接口协议和电路电气特性自行规划接口电路进行数据收集与处理,一起海德汉也供给了特定的数据处理芯片供用户挑选。假如用户自行规划电路,需遵从EnDat接口的电气特性,并需求把握EnDat接口的协议,确保严厉遵从协议的时序要求和数据帧格局。而假如选用海德汉供给的数据处理芯片,则能够简化规划,用户只需装备FPGA的寄存器,依照芯片可接受的指令格局发送指令,就可取得需求的数据。

经过遵从RS一485(差分信号)规范的收发元件,在后续电子设备宣布的同步时钟鼓励下,数据(方位值和参数)能够在编码器和后续电子设备之间双向传输。

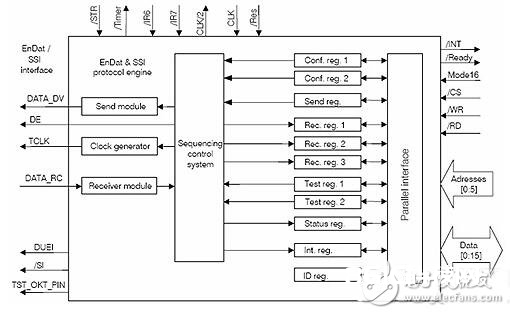

四FPGA+软件宏

海德汉的合作伙伴MAZet公司针对Xilinx公司的Virtex和Spartan系列及Altera公司的Acex和Cyclone系列供给了EnDat协议的软件宏,依据客户需求,MAZet公司还能够供给定制软核。该软核完结了EnDat接口的一切功用,用户可经过6位地址线和16位数据线与微操控器进行8位或16位的数据传输。下面是FPGA的模块图和电路规划。

图4FPGA模块图

图5编码器和后续电路衔接模块图

海德汉公司的EnDat接口在许多职业已得到广泛的使用,现在它又被提升到簇新高度。双向EnDat2.2接口的时钟频率现已进步到16MHz,能满意直接驱动这类高动态功用要求的使用,特别是电子工业的使用,时钟频率从8MHz进步到16MHz不只将大大缩短读取方位信息所需时刻,还能够大幅缩短操控环的周期。一起简略、经济的体系规划为客户供给了便利,强壮的功用和通用性及具有前瞻的安全规划理念引导编码操控技能不断向前开展.