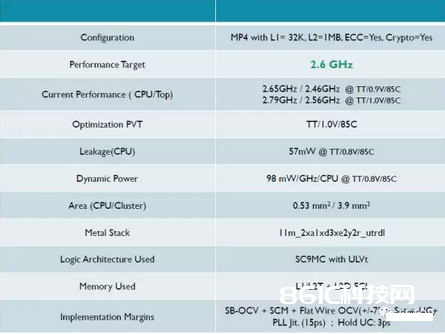

首要,我要着重,我不是做后端的,可是工作中常常遇到和做商场和芯片搭档评论PPA。这时,后端会拿出这样一个表格:

下图是一个A53的后端完成成果,节点是TSMC16FFLL+,咱们就此来解读下。

首要,咱们需求知道,作为一个有抱负的手机芯片公司,能够挑选的工厂并不多,台积电(TSMC),联电(UMC),三星,Global

Foundries(GF),中芯(SMIC)也牵强算一个。还有,本年开端Intel工厂(ICF)也会开放给ARM处理器。事实上有人现已开端做了,只不过用的不是第三方的物理库。一般新工艺会选TSMC,然后要降本钱的时分会去UMC。GF一向比较特殊,稳妥起见不敢选,而三星不太理他人所以也没人理他。至于SMIC,嘿嘿,那需求有很高的抱负才干选。

16nm的意义我就不具体说了,网上许多解说。而TSMC的16nm又分为许多小节点,FFLL+,FFC等。他们之间的最高频率,漏电,本钱等会有一些差异,合适不同的芯片,比方手机芯片喜爱漏电低,本钱低的,服务器喜爱频率高的,不胜枚举。

接下来看表格第一排,Configuration。这个最简略了解,运用了四核A53,一级数据缓存32KB,二级1MB,打开了ECC和加解密引擎。这几个选项会对面积发生较大影响,对频率和功耗也有较小影响。

接下来是Performance

target,方针频率。后端工程师把频率称作Performance,在做后端完成时,有必要在频率,功耗,面积(PPA)里选定一个主参数来作为首要优化方针。这个表格是专门为高功能A53做的,频率越高,面积和漏电就会越大,这是无法防止的。稍后我再贴个低功耗小面积的陈述做比照。

下面是Current

Performance,也便是现在完成了的频率。里边的TT/0.9V/85C是什么意思?咱们知道,在一个晶圆(Wafer)上,不行能每点的电子漂移速度都是相同的,而电压,温度不同,它们的特性也会不同,咱们把它们分类,就有了PVT(Process,Voltage,

Temperature),别离对应于TT/0.9V/85C。而Process又有许多Conner,相似正态散布,TT仅仅其间之一,依照电子漂移速度还能够有SS,S,TT,F,FF等等。一般后端成果需求一个Signoff条件(咱们这一般是SSG),依照这个条件出去流片,作为挑选门槛,之下的芯片就会不合格,跑不到所需的频率。所以条件设的越低,良率(Yield)就会越高。可是条件也不能设的太低,否则后端很难做,或许爽性方程无解,跑不出成果。X86上有个词叫体质,便是这个PVT。

这一栏有四个频率,上下两组简略差异,便是不同的电压。在频率确守时,动态功耗是电压的2次方,这个咱们都知道。而左右两组数字的差异便是Corner了,别离为TT和SSG。

下一行是Optimization

PVT。咱们都知道后端EDA东西其实便是解方程,需求给他一个优化方针,它会主动找出最优部分解。而1.0V和0.9V中有必要选一个值,作为最常用的频率,功耗和面积的甜点(Sweet

Spot)。这儿是选了1.0V,它的SSG和方针要求更挨近,那些达不到的Corner能够作为降频贱卖。

再下一行是漏电Leakage,便是静态功耗。CPU停在那啥都不跑也会有这个功耗,它包括了四个CPU中的逻辑和一级缓存的漏电。可是A53自身是不包括二级缓存的,其他的一些小逻辑,比方SCU(Snooping

Control Unit)也在CPU核之外,这些被称作Non-CPU,包括在MP4中。咱们待机的时分便是看的它,能够经过power

gating关掉二三级缓存,可是一般来说,不会全关,或许无法关。

下面是Dynamic

Power,动态功耗。根本上我见过的CPU在丈量动态功耗的时分,都是跑的Dhrystone。Dhrystone是个十分陈旧的跑分程序,根本上便是在做字符串复制,十分简略被软件,编译器和硬件优化,作为功能方针根本上只要MCU在看了。可是它有个优点,便是程序很小,数据量也少,能够只运转在一级缓存(假如有的话),这样二级缓存和它之后的电路全都只要漏电。尽管拜访二级三级缓存乃至DDR会比拜访一级缓存耗费更多的能量,可是它们的推迟也大,此刻CPU流水线很或许堕入中止。这样的成果便是Dhrystone能最大程度的耗费CPU中心逻辑的功耗,比拜访二级以上缓存的程序都要高。所以一般都拿Dhrystone来作为CPU最大功耗方针。实际上,是能够写出比Dhrystone更耗电的程序的,称作Max

Power Vector,做SoC功耗预算的时分会用上。

动态功耗和电压强相关。公式里边自身便是2次方,然后频率改变也和电压相关,在跨电压的时分便是三次方的联系了。所以别看1.0V只比0.72V高了39%,终究动态功耗或许是3倍。而频率高的时分,动态功耗占了绝大部分,所以电压不行小觑。

此外,动态功耗和温度相关,SoC运转的时分不行能温度维持在0度,所以功耗一般会拿85度或许更高来核算,这个就不多说了。

下一行是Area,面积。面积是芯片公司的安身之本,和毛利率直接相关。所以在功能契合的情况下,越小越好,乃至能够献身功耗,不吝推高电压,所以有了OD(Over

Drive)。有个数据,当时28nm上,每个平方毫米差不多是10美分的本钱,一个超低端的手机芯片怎样也得30mm(200块钱那种手机用的,或许你都没见过,仍是智能机),芯片面积本钱便是3刀,这还不算封测,贮存和运送。低端的也得是40mm(300块的手机)。咱们常见的600-700块钱的手机,其间六分之一本钱是手机芯片。当然,反过来,也有人不缺钱的,比方苹果,听说A10在16nm上做到了125mm,换算成这儿的A53MP4,单看面积不考虑功耗,足足能够放120个A53,极端奢华,这可是跑在2.8G的A53,假如是1.5G的,150个都或许做到。

那苹果这么大的面积到底是做什么了?首要,像GPU,Video,Display,基带,ISP这些模块,都是能够简单的拿面积换功能的,由于能够并行处理。并且,功耗也能够拿面积换,一个最简略的方法便是降频,添加处理单元数。这样漏电尽管添加,可是电压下降,动态功耗能够削减许多。一个破例便是CPU的单核功能,为什么苹果能够做到Kirin960的1.8倍,散热还能承受?和物理库,后端,前端,软件都有联系。

首要,A10是6发射,一起代的A73只用了2发射。当然,由于受到了数据和指令相关性约束,功能不是三倍提高,而6发射的成果是面积和功耗非线性添加。作为一个比较,我看过ARM的6发射CPU模型,同工艺下,单核每赫兹功能是A73的1.8倍,动态功耗预算超越2倍,面积也挨近2倍。当然,它的微结构和A73是有挺大差异的。这个单核芯片跑在16nm,2.5Ghz,单核功耗差不多是1W。而手机芯片的功耗能够维持在2.5W不降频,所以苹果的2.3Ghz的A10算下来仍是可行的。

为了操控功耗,在做RTL的时分就需求刺进额定晶体管,做Clock

Gating,并且这仍是分级的,RTL级,模块级,体系级,信号时钟上也有(我看到的SoC时钟一般占了整个逻辑电路功耗的三分之一)。这样一套搞下来,面积最少大1/3.然后便是Power

Gating,也是分级的。最简略的是每块缓存给一个开关,模块也有一个开关。杂乱的依据不同指令,能够核算出哪些Cache

bank短时刻内不必,直接给它关了。Power Gating需求的延时会比Clock Gating大,有的时分假如操作很频频,Power

Gating反而因小失大,这需求细心的考量。并且,规划的越杂乱,验证也就越难写,这儿边需求做一个均衡。除了时钟域,电源域,还有电压域,能够依据不同频率调电压。当然了,域越多,布线越难,面积越大。

再往上,能够界说出不同的power state,让上层软件也参加经来,构成电源办理和调度。我在这个答复里边写的更具体一些:怎么点评 ARM 的

big.LITTLE 巨细核切换技能?

再回到苹果A10,它还运用了6MB的缓存。这个在手机里边也算大的惊世骇俗。一般高端的A73加2MB,A53加1MB,现已很巨大上了,低端的加起来也不超越1MB。我拿SPECINT2K在A53做过一些试验,二级缓存从128KB添加到1MB只会添加15%不到的功能,到6MB那功能/面积收益更不是线性的,这是光秃秃的面积换功能。并且苹果宣传的不是SPECINT,而是GeekBench4.0,我置疑是不是这个跑分对缓存巨细更灵敏,有空能够做做试验。顺带提一句,安兔兔5.0和缓存巨细没半毛钱联系,这让广阔高端手机芯片公司情何以堪。到了6.0好像改了,我还没细心研讨过。至于运用了大面积缓存引起的漏电,却是有方法处理,那便是部分封闭缓存,用多少开多少,是个精细活,需求软硬件一起合作。

影响面积的要素还没完,上面仅仅前端,后端还有一堆考量呢。

首要便是表格下一排,Metal

Stack。芯片制作的时分是一层层蚀刻的,而蚀刻的时分需求一层层打码,以免要害部分见光,简称Mask。这儿的11m就表明有11层。晶体管自身是在最底层的,而走线就得从上面走,层数越多越简略,做板子布线的同学必定一看就了解了。照理说这就该多放几层,可是工厂跟你算钱也是依照层数来的,越多越贵。层数少了不但走线难,整体面积的利用率也低,像A53,11层做到80%的利用率就挺好了。所以芯片上不是把每个小模块面积求和便是整体面积,还得考虑布局布线(PR,Placing&Routing),考虑面积利用率。

再看表格下两排,Logic

Architecture和Memory。这个也简略了解,便是逻辑和内存,数字电路的两大模块分类。这个内存是片上静态内存,不是外面的DDR。uLVT是什么意思呢,Ultra

Low Voltage Threshold,指的是规范逻辑单元(Standard

Cell)用了超低电压门限。电压低关于动态功耗当然是个功德,可是这个规范单元的漏电也很高,和频率是对数联系,也便是说,漏电每添加10倍,最高频率才添加log10%。后端能够给EDA东西设一个约束条件,比方只要不超越1%的需求冲频率的要害途径逻辑电路运用uLVT,其他都运用LVT,SVT或许HVT(电压顺次升高,漏电减小),来减小整体漏电。

关于动态功耗,后端还能够定制晶体管的源极和漏极的长度,越窄的电流越大,漏电越高,相应的,最高频率就能够冲的更高。所以咱们有时分还能看到uLVT

C16,LVT C24之类的参数,这儿的C便是指Channel Length。

接下去便是Memory,又作Memory Instance,也有人把它称作FCI(Fast Cache

Instance)。拜访Memory有三个重要参数,read,write和setup。这三个参数能够是相同的时刻,也能够不相同。关于一级缓存来说根本用的是相同的时刻,并且是一个时钟周期,并且这傍边无法流水化。从A73开端,我看到后端的要害途径都是卡在拜访一级缓存上。也便是说,这段途径能做多快,CPU就能跑到多快的频率,而一级缓存的巨细也决议了索引的巨细,越大就越慢,频率越低,所以ARM的高端CPU一级缓存都没超越64KB,这和后端严密相关。当然,一级缓存增大带来的收益自身也会非线性减小。之后的二三级缓存,能够运用多周期拜访,也能够运用多bank替换拜访,巨细也因而能够放到几百KB/几MB。

逻辑和内存统称为Physical

Library,物理库,它是依据工厂给的每个工艺节点的物理开发包(PDK)规划的,而Library是一个Fabless芯片公司能做到的最底层。能够定制自己的老练物理库,是这家公司后端抢先的标志之一。

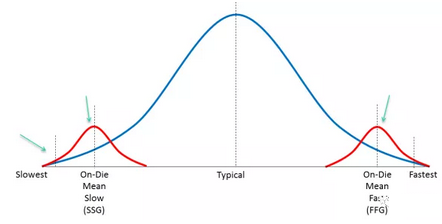

最终一行,Margin。这是指的工厂在出产过程中,必定会发生误差,而这行方针界说了误差的规模。如下图:

蓝色表明咱们方才说的一些Corner的散布,赤色表明出产误差Variation。有必要做一些测验芯片来纠正这些误差。SB-OCV表明stage-based

on-chip variation,和其他的几个误差加在一起,一共+-7%,也便是说会有7%的芯片不在后端规划结束时确认的成果之内。

后边还有一些setup UC之类的,表明信号树立时刻,坚持时刻的不确认性(Uncertainty),以及PLL的颤动规模。

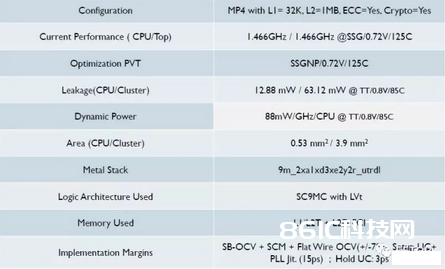

至此,一张陈述解读结束,咱们再看看对应的低功耗版完成版别:

这儿频率降到1.5G左右,每Ghz动态功耗少了10%,可是静态降到了12.88mW,只要25%。咱们能够看到,这儿运用了LVT,没有uLVT,这便是静态能够做低的原因之一。由于面积不是优化方针,它根本没变,这个也是能够了解的,由于Channel宽度没变,逻辑的面积无法变小。