时钟设备规划运用 I2C 可编程小数锁相环 (PLL),可满意高性能时序需求,这样能够发生零 PPM(百万分之一)组成过失的频率。高性能时钟 IC 具有多个时钟输出,用于驱动打印机、扫描仪和路由器等运用体系的子体系,例如处理器、FPGA、数据转化器等。此类杂乱体系需求动态更新参阅时钟的频率,以完结 PCIe 和以太网等其它许多协议。

时钟 IC 归于 I2C 从器材,需求主操控器来装备内部 PLL 逻辑,其操控逻辑能够写入微操控器内。作为 I2C 主机,微操控器将装备写入时钟 IC 的内部易失性存储器并操控 PLL。因而,能够经过板上 MCU – IC 组合进行体系时钟频率的动态更新。可编程微操控器为高性能时钟 IC 供给操控逻辑才能,经过削减板载 IC和板上走线使全体规划愈加紧凑,并下降终究物料本钱。

操作理论

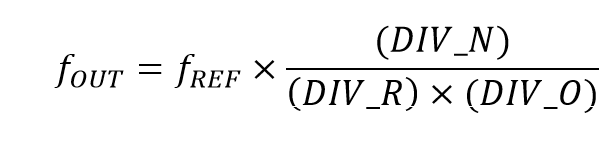

图 1 为高性能时钟设备的根本 PLL 架构。该规划运用份额因子为 PLL 输出端口供给时钟组成。终究输出频率的根本公式为:

fREF 为输入参阅晶体频率(在大都运用中一般为 8 MHz 至 48 MHz)。

DIV_R(DIV_R1 和 DIV_R2)是输入频率参阅的分频因子。此类分频器名为预分频器。

DIV_N 为小数 N 分频因子。

DIV_O(DIV-O1、DIV-O2、DIV-O3 和 DIV-O4)为输出前的后分频因子。

图 1简化高性能时钟的 PLL 架构框图

图1中的橙色框图为参数,运用这些参数的方程式为可编程方程式。这些参数能够在出厂时写入时钟设备的非易失性存储器。时钟设备具有内部易失性和非易失性存储器,两个存储器相互仿制其内容。非易失性存储器在出厂时已被写入所需装备,在终究运用中,当设备发动电源时,非易失性存储器的内容会被仿制到易失性存储器。一起,PLL 发生所需的默许时钟输出。

时钟 IC 的重要特性之一便是经过 I2C 接口完结运转时可编程。经过可编程功用,用户能够更改设备的易失性存储器内容以进行即时更改。只需运用恰当的 I2C 指令,就能够经过主操控器完结用户装备文件的即时编程功用。

设备的非易失性存储器还能够存储预界说的多用户装备。用户能够运用频率挑选 (Frequency Select, FS) 功用以挑选其间一个装备。该 FS – 位为设备中可用的 CMOS 输入引脚。FS 引脚运用 N – 位外部 CMOS 信号,然后内部挑选存储在非易失性存储器中的一个装备文件,这个装备文件相同也被仿制到了易失性存储器,PLL 则输出不同的信号。

一起,微操控器经过 I2C 供给数据来操控高频时钟。运用微操控器的长处是,它具有不同的通讯外设和通讯协议,如 I2C、SPI、UART、蓝牙、ZigBee 等,使得体系能够以主从装备将数据传输到其他微操控器,也能够运用一个自界说的运用传输至安卓和 iOS 设备。此外,微操控器还配有各种 IDE 东西用于简化规划。这能够更好地证明运用 I2C 指令来装备 PLL 参数、编写并验证定制运用程序是适宜的。

高性能时钟的运用需求

高性能时钟 IC 专为顾客、工业和网络运用而规划。此类时钟 IC 具有多个从不同 PLL 导出的差分输出和单端输出,而且能够经过 I2C 接口完结可编程功用。此外,高性能时钟 IC不只能够支撑 PCI Express (PCIe) 1.0 / 2.0 / 3.0、USB 2.0 / 3.0 和万兆以太网 (GbE)等要害接口标准的参阅时钟。还能支撑压控晶体振荡器 (VCXO) 和频率挑选 (FS)等其他增值功用。

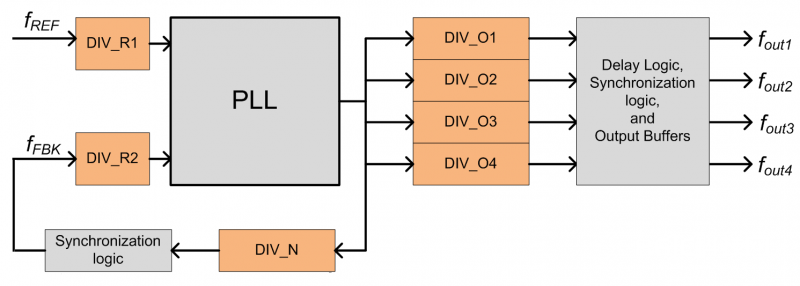

高性能时钟 IC 选用规划完结 I2C 从机形式。因而,需求一个板载 I2C 主机来操控以下可编程功用:

· 经过 I2C 接口进行体系内编程

· 经过频率挑选 (FS) 引脚更新装备

· 外部复位操作

· 压控晶体振荡器 (VCXO) 操作

图 2:微操控器 – 高性能时钟接口电路

微操控器在时钟 IC PLL 操控中的效果

如图 2 所示,将时钟 IC 连接到微操控器电路。时钟 IC 具有内部 PLL 模块,其功用是供给作为固定直流电压的调谐电压 (Vtune) ,而调谐电压将随频段而改动。PLL 模块在输入端接纳本地振荡器频率,由内部前置扩大器扩大信号。别的,预分频器对输入频率进行下变频,并将其作为输入传送至相位比较器。

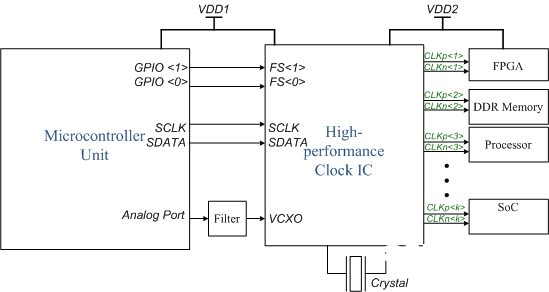

图 3:PLL 模块的微操控器操控。

微操控器经过 I2C 发送数据到可编程分频器。该分频器也接纳来自参阅振荡器(例如 4 MHz 晶体振荡器)的输入。相位比较器(即相位检测器)经过预分频器接纳本地振荡器频率(例如 87.15 MHz),还经过参阅分频器和参阅振荡器接纳微操控器的输入(例如,87.15 MHz)。假如两个输入都匹配,相位比较器将供给 Vtune 调谐电压。一旦本地振荡器频率与微操控器频率数据之间稍有不匹配,都将无法供给调谐电压 (Vtune) 和输出。图 3 所示为完好的框图。

在微操控器的协助下,PLL 经过调谐本地振荡器频率发生闭环,并在输出端发生调谐电压。调谐电压将从较低频率信道增加到较高频率信道。经过改动预分频器和可编程分频器的值,微操控器能够调整步长。

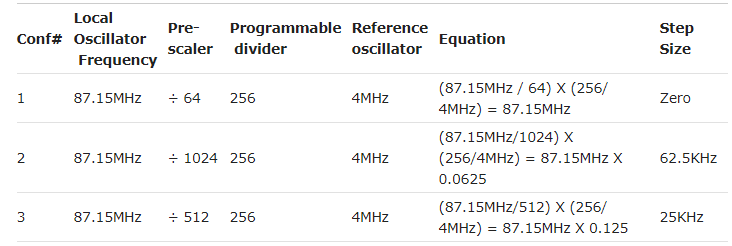

步长 =(本地振荡器频率/预分频器)X(可编程分频器/参阅振荡器)

表 1 所示为部分装备

经过 I2C 接口进行体系内编程

体系内编程可为体系规划完结快速有用的迭代。编程数据序列可经过 SCL 和 SDA 引脚传送到时钟器材,把操作次序编程至板载微操控器(主设备)中,经过指令和数据在运转时与从机时钟进行交互。

此处为体系示例,其间时钟信号有必要以采样率的倍数为准。该时钟频率在 155.52 MHz 和 156.25 MHz 两组频率之间改变。这意味着驱动串行操控器的时钟有必要能够在这两个值之间灵敏切换。微操控器主设备能够拜访并修正写入易失性存储器的 PLL 装备,然后满意这两个频率需求。

经过频率挑选 (FS) 引脚更新装备

高性能时钟设备支撑包含个性化装备的多个用户装备文件。在 FS 引脚转化方面,高性能时钟器材具有两个时序标准 – 快速切换和慢速切换。

快速切换适用于输出 ON/OFF 、输出分频值改动,以及输出 MUX 设置更改。慢速切换则适用于更改 PLL 参数(包含 PLL ON/OFF)。望文生义,快速切换中的输出改动更快,而慢速切换的速度较慢。两种切换类型都能够翻开或封闭输出,而且不出一点点过失。图 4 所示为 FS 与输出时钟之间的时序联系。

图 4:频率挑选操作

外部复位操作:

当外部复位收效时,时钟 IC 进入低功耗形式。输出和 I2C 总线信号处于高阻抗 (HI-Z) 状况,直到撤销外部复位并完结初始化。外部复位重启易失性存储器内容,存储在非易失性存储器中的装备则被仿制到易失性存储器。当需求从头初始化恣意一个体系中运转的运用程序时,该功用将被运用。

压控晶体振荡器 (VCXO) 操作:

对某些运用而言,输出时钟频率应经过运用模仿反应盯梢输入数据流。如图 5 所示,时钟 IC 作为大锁相环的一部分。ASIC 或 SoC 担任盯梢输入流、计算过失并发生 PWM 信号(一般来说),随后将过失信息反应至本地时钟发生器以进行频率调谐。

图 5VCXO 示例电路

VCXO 功用能够修正 PLL 频率,因而频率牵引不依赖于晶体特性、温度、电压或设备工艺。VCXO 调制是线性、精准调制。也能够运用时钟参阅。经过微操控器的内置模仿模块,VCXO 的操控逻辑精准到小数点后 6 位。

作为 I2C 主设备,微操控器将装备写入时钟 IC 的内部易失性存储器并操控 PLL。因而,经过板载 MCU-IC 组合能够完结体系时钟频率的动态更新。开发人员能够运用可编程微操控器,为高性能时钟 IC 供给操控逻辑。这能够削减对板载 IC 和走线数量的需求,使得整个体系规划愈加紧凑。

微操控器装备强壮 IDE 东西,能够加快运用开发。集成可编程片上体系(PSoC)器材可进一步简化规划并有助于下降全体产品本钱。有关高性能时钟 %&&&&&% 规划的更多详细信息,请参阅4-PLL扩频时钟发生器入门以及扩频时钟发生器的规划最佳实践。