一、试验意图

1.把握数字示波丈量的基本原理。

2.了解数字存储示波器的硬件结构。

3.把握虚拟数字存储示波器的CVI软件规划。

规划虚拟数字存储示波器

(1)规划一个包含耦合方法挑选、伏/格调整、触发源挑选、时基挑选等基本功用的虚拟数字存储示波器界面,要求显现屏水平刻度为10div,笔直刻度为10div。

(2)在完结内容(1)的基础上完结幅值、时基可调的虚拟双踪数字存储示波器。

要求:①笔直灵敏度至少包含50mV/div、0.1V/div、0.5V/div、1V/div四档;②扫描速度至少包含0.1u/div、1u/div、10u/div、100u/div、500u/div、1m/div、10m/div、0.1s/div八档;③添加双踪示波功用,能一起显现两路被测信号波形。

(3)数据处理规划

要求:①显现被测信号幅值包含:有效值、峰峰值、平均值;②显现被测信号的频率值。

(4)在电子丈量试验箱中示波器硬件供给32K存储深度的基础上规划波形存储、回放功用。

三、试验器材

1.SJ-8002B电子丈量试验箱 1台

2.核算机 1台

3.信号源(也能够运用渠道的DDS信号源) 2台

4.Q9线 1 条

5.示波器 1台

4.1 数字示波器原理

数字存储示波器是用 A/D 变换器把模仿信号转化成数字信号,然后把数据存储在半导体存储器 RAM 中。当有需求时,将 RAM 中存储的内容调出,通过 LCD 用点阵或连线的方法再现波形,其原理框图能够参阅图1。在这种示波器中信号处理和信号显现功用是分隔的,它的功用首要取决于进行信号处理的AD、RAM 和微处理器的功用。因为选用 RAM 存储器,能够快写数慢读数,使得即便在调查缓慢信号时也不会有闪耀现象。

4.2 虚拟数字存储示波器组成

图1 虚拟数字存储示波器

虚拟示波器将核算机和丈量体系融合于一体,用核算机软件替代传统仪器的某些硬件的功用,用核算机的显现器替代传统仪器物理面板。通过相关的软件能够规划出的操作便利、形象传神的仪器面板,不只能够完结传统示波器的功用,并且具有存储、再现、剖析、处理波形等特色,还能够进行各种信号的处理、加工和剖析,完结各种规划的丈量使命。并且仪器的体积小、耗电少,便利带着,能够在不同的核算机上运用。

因而,在SJ-8002B中,也引用了虚拟数字存储示波器的原理来完结数据的收集。其间的信号调度、AD转化、存储数据的SRAM以及操控逻辑都在是试验渠道中,核算机首要起到了数据的处理和显现的效果。

4.3 SJ-8002B电子丈量试验箱示波器硬件结构

4.3.1测验规模及收集参数调整规模

测验电压起伏规模:-20V~+20V(峰峰值)

丈量频率规模:1Hz~1MHz

采样时钟:

| timebase序号 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

采样时钟频率 |

20M |

20M |

20M |

20M |

20M |

20M |

20M |

20M |

20M |

20M |

|

timebase序号 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

|

采样时钟频率 |

10M |

5M |

2.5M |

1M |

500K |

250K |

100K |

50K |

25K |

12.5K |

可程控增益:

| Div序号 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

通道总增益A |

20 |

10 |

5 |

2 |

1 |

0.5 |

0.2 |

0.1 |

0.05 |

0.02 |

数据缓存深度:64KB

对收集的数据进行剖析,显现波形的峰值、平均值、有效值和频率、周期等参数。

4.3.2 硬件原理图

图2 SJ8002B示波器硬件原理图

图2为示波器模块的原理框图。由图可见,高速收集的双通道是彻底独立的,因而能够完结多种不同的测验使命,完结虚拟双踪数字存储示波器的各种功用。

4.3.3 操控逻辑

示波器的硬件操控首要分为数据写入(收集)和数据读出(显现)两个部分。其间操控逻辑悉数都在存储在CPLD内部,如图3所示:

图3 示波器的硬件操控逻辑

Ain1和Ain2通道接入相同的采样时钟,一起进行转化。转化后的数据通过缓冲器,送至SRAM锁存。当一次收集完结后,由主机读回数据,进行进一步的处理,如滤波、显现等。

数据写入:AD9288在采样时钟CLK的操控下,将两路输入模仿信号数字离散为8bit数字信号通过数据缓冲器送至SRAM。地址由同一个地址计数器供给,该地址计数器为加/减计数器(收集数据时递加,读取时递减)。这样,每次收集所得数据都会顺畅的存入SRAM中。

4.3.4收集部分

收集部分的要害器材是ADI公司的AD9288,它是8bit双通道含有采样坚持电路的单片集成的模/数转化器,具有低功耗、体积小、动态特性好、易于有用的特色。双8bits、40MSPS,低功耗(每个通道90mw),SNR=47DB(在41MHz时),每个通道的模仿输入规模1.024Vp-p,中心电平Vin0=1/3 Vdd,3.0V模仿供电(2.7V-3.6V),两种数据输出形式(补码或原码),电平兼容TTL/CMOS。

4.3.5 调度电路

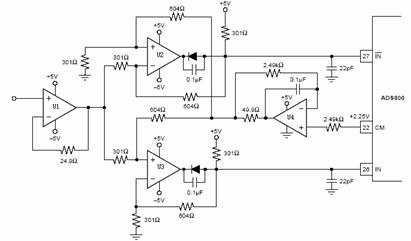

因为AD9288选用了差分输入,所以需求将试验板的模仿输入的直流耦合单边信号,无失真的转化为差分信号,并将信号的起伏进行平移,以满意AD9288 0.5~1.5V的输入要求。选用了如下的通道电路完结信号的转化。

图4 差分信号转化电路

电路中,U1是一个跟从器,效果是阻抗匹配;差分信号的发生选用了2个运算放大器,其间U2是作为输入的同相放大器,U3是作为输入补给的反相放大器。两个二极管和U4组成了信号平移部分。

4.3.6 衰减和增益操控电路

因为示波器的测验规模(-20V~+20V)比AD9288的测验规模(0.5V~1.5V)宽,因而,在收集电路的前端参加信号衰减和信号增益两级起伏调整电路,确保丈量的正确性以及进步丈量的精确度。