本刊前两期给出了数字示波器DIY制作计划,第一篇会集介绍了LCD绘图显现,第二篇介绍了模仿信号调度,完结这些内容学习之后,读者可能会发现一个丧命的问题,那便是高速数据收集,前面给出的计划是根据MCU操控的ADC,这种计划丧命的缺点是数据收集的速度慢,对频率稍高的信号无法有用采样,本篇将介绍一种MCU加CPLD操控的DMA高速数据采样计划。

一、传统低速数据收集

传统MCU操控的ADC数据收集原理框图如图1所示,MCU运转驱动程序操控ADC循环转化,每次转化一般由发动、查询等候、读取数据、写入RAM几个进程,每一个进程都需求CPU履行若干指令来完成,这样的数据收集不只受ADC速度,尤其是遭到MCU运转速度影响,一般只能做低速数据收集。

二、DMA数据收集

DMA也便是DirectMemoryAccess简称,是直接内存存取的意思,DMA的首要优势是可在无CPU干与的情况下进行数据的交流,能够将ADC的速度发挥到极致。根据MCU加CPLD操控的DMA原理框图如图2所示。MCU通过对CPLD的操控,完成让出数据总线,由CPLD时序逻辑电路操控AD循环转化并将成果直接存储到RAM中,这个循环进程是纯硬件电路完成的,因而速度快,不受MCU速度影响。MCU查询到一帧数据收集完结后,再夺回数据总线,从RAM中读取数据,处理数据并显现波形。

下面咱们结合详细的器材来介绍这种DMA计划,ADC器材挑选TLC5510,RAM挑选UT62256,32KSRAM。

TLC5510是美国德州仪器公司出产的8位半闪速结构模数转化器,它选用CMOS工艺制作,可提供最小20Msps的采样率。

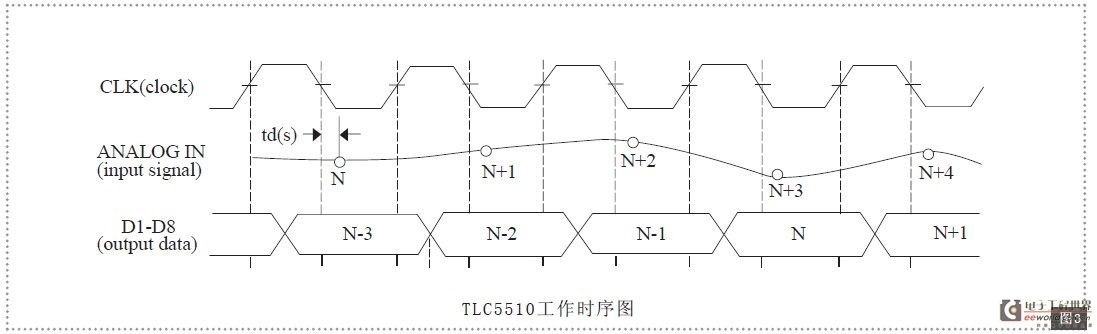

TLC5510的作业时序图如图3所示,时钟信号CLK在每一个下降沿收集模仿输入信号。第N次收集的数据通过2.5个时钟周期的推迟之后,在时钟上升沿将转化得到的成果送到内部数据总线上,在时钟其他时间段数据坚持不变。能够看到,该器材能够在20MHz时钟信号驱动下以20MHz的采样率收集数据,均匀取得一个数据只需0.05μs。

RAM数据写入时序图如图4所示。RAM的写入条件是具有确认的地址ADDR,CE=0,WE=0,OE=1;数据线上的数据将被写入RAM内部相应的单元。

归纳TLC5510的作业时序和RAM的写入时序,提出如图5所示的驱动进程。根据同一个时钟信号驱动,在时钟下降沿①、低电平②、上升沿③、高电平④4个节拍中,同步完成AD转化和数据写入RAM。