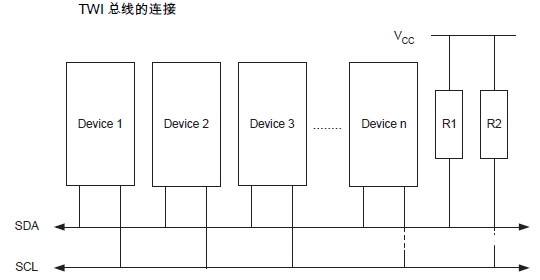

在AVR系列单片机中内嵌有一个TWI(Two-wire Serial Interface)接口,它实际上便是IIC总线接口。IIC是一种多向操控总线,它是由PHILIPS公司在二十世纪八十年代初规划出来的,使用该总线可完成多主机体系所需的判决和高低速设备同步等功用,是一种高性能的串行总线。IIC总线的衔接方法如下图所示。它只用两根双向传输线就能够将128个不同的设备互连到一同。这两根线一根是时钟线SCL,一根是数据SDA。外部硬件只需求两个上拉电阻,每根线上一个。一切衔接到总线上的设备都有自己的地址。

总线的速度有两个不同的标准,一种的速度低于100kHz,而别的一种的速度高达400kHz,总线间的%&&&&&%不能大于400pF。一切TWI兼容的器材的总线驱动都应该是漏极开路或集电极开路的结构,这样就能够完成线与的功用。TWI器材在输出为0时,TWI总线会发生低电平。当一切的TWI器材输出为三态时,总线会输出高电平,假如接有上拉电阻电压将会被拉高。

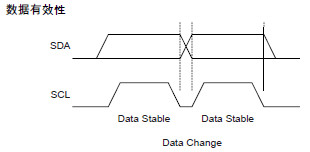

TWI总线上传输的数据是经过在时钟线(SCL)高电平期间对应的数据线(SDA)上的电平来判别的。可经过下图来描绘。

在上图中,当SCL拉高期间对应的SDA的电平,假如是高则这位数据便是1,反之则是0。只要在SCL为低电平期间,SDA才能够更新下一位的数据。TWI总线上数据的传送便是经过SCL为高时对应到的SDA的值来构成的。明显,SCL的频率决议了数据传送的速度。

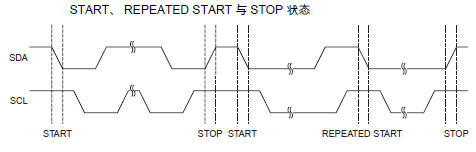

除了传送的数据以外,在每一帧数据传送之前,还会有一个发动信号,以告诉从机预备接纳数据。在数据传送完毕之后,也会有一个中止信号,以告诉从机数据传输完毕。发动信号是这样来界说的,在SCL为高电平期间,若对应的SDA线上有一个由高变低的电平下跳沿,则标明这是一个发动信号。相同,中止信号是这样界说的,在SCL为高电平期间,若对应的SDA线上有一个由低变高的电平上跳沿,则标明这是一个中止信号。为了构成发动或中止信号,有必要在判别该信号的SCL拉高之前做好电平预备,比如要构成一个中止信号,有必要在SCL为低电平期间把SDA上的电平拉低,以便在紧跟着后边的SCL高电平期间把SDA的电平拉低,构成一个中止信号。当已经有一个发动信号之后,在没有中止信号呈现之前若再次呈现发动信号,则标明该信号是一个重新发动信号,它首要用于在主机不抛弃总线操控的情况下发动新的传送。上述整个进程可用下图来描绘。

经过上述评论,说明晰TWI总线的数据位传送与时钟脉冲是同步的。除了发动与中止情况之外,当时钟线为高电平时,数据线上的电压(不论是高仍是低)有必要保持稳定,不然有或许被识别成中止信号或重新开始的信号。

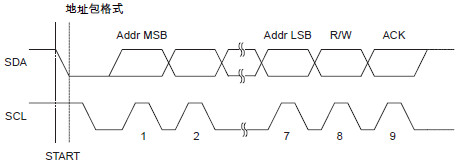

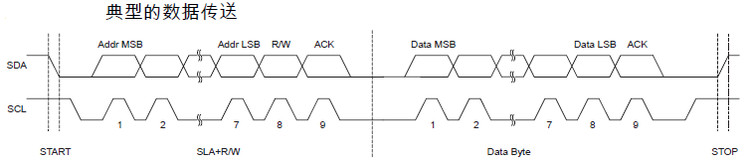

下面来看TWI总线是怎么寻址的。在发动信号之后紧接着的便是地址帧,一切的地址包均为9位,包括7位地址位、1位READ/WRITE操控位(即方向位,标明是主机写从机仍是从机写主机)与1位应对位。假如READ/WRITE为1,则履行读(从机写主机)操作;不然履行写(主机写从机)操作。从机被寻址后,有必要在第九个SCL(ACK)周期经过拉低SDA作出应对。发送地址时先发送高位后发送低位,地址字节的MSB(数据的最高位)先被发送,从机地址由用户自行分配,但要避开保存的播送地址(即地址0000000)。地址的传输格局可用下图来描绘。

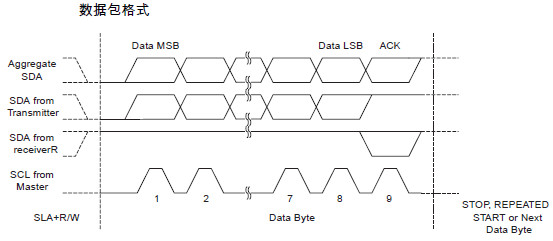

地址发送后,就要发送数据包。一切在TWI总线上传送的数据包为9位长,包括8位数据位及1位应对位。在数据传送中,主机发生时钟及START与STOP情况,而接纳器呼应接纳。应对是由从机在第9个SCL周期拉低SDA完成的。假如接纳器在第9个SCL周期使SDA为高,则是宣布NACK信号。NACK信号是在接纳器在完成了最终数据的接纳,或许因为某些原因无法接纳更多的数据时,才在收到最终的字节后宣布去奉告发送器的。数据的传输格局可用下图来描绘。

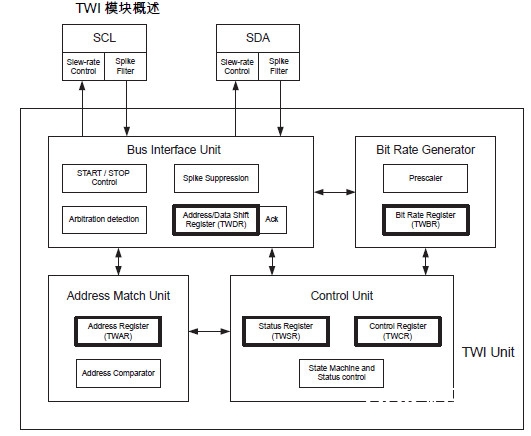

在上图中,坐落粗线之中的寄存器能够经进程序进行拜访。SCL与SDA为MCU的TWI接口引脚。引脚的输出驱动器包括一个波形斜率限制器以满意TWI的信号标准。引脚的输入部分包括尖峰按捺单元以去除小于50ns的毛刺搅扰。当相应的端口被设置为SCL与SDA引脚时,能够使能I/O口内部的上拉电阻,这样可省掉外部的上拉电阻。

当TWI作业于主机形式时,比特率发生器(上图中的Bit Rate Generator部分)操控时钟信号SCL的周期。详细的值由TWI情况寄存器TWSR(上图中的Control Unit部本分)的预分频系数以及比特率寄存器TWBR(上图中的Bit Rate Generator部本分)设定。可经过下面的公式来核算。

式中,TWBR是TWI比特率寄存器的数值,TWPS是TWI情况寄存器预分频的数值。TWI作业在主机形式时,TWBR值应该不小于10。不然主机会在SDA与SCL发生过错输出作为提示信号。

当TWI作业在从机形式时,不需求对比特率或预分频进行设定,但从机的CPU时钟频率有必要大于TWI时钟线SCL频率的16倍。

在上图中,还有一个总线接口(上图中的Bus Interface Unit部分)。它包括有数据与地址移位寄存器TWDR,START/STOP操控器和总线裁定断定硬件电路。TWDR寄存器用于寄存发送或接纳的数据或地址。除了8位的TWDR外,总线接口单元还有一个寄存器,包括了用于发送或接纳应对的(N)ACK。这个(N)ACK寄存器不能由程序直接拜访。当接纳数据时,它能够经过TWI操控寄存器TWCR来置位或清零;在发送数据时,(N)ACK值由TWCR的设置来决议。START/STOP操控器担任发生和检测TWI总线上的START、REPEATEDSTART与STOP情况。即便在MCU处于休眠情况时,START/STOP操控器依然能够检测TWI总线上的START/STOP条件,当检测到自己被TWI总线上的主机寻址时,将MCU从休眠情况唤醒,这一功用在节电时十分必要。

接下来是地址匹配单元(上图中的Address Match Unit部分)。地址匹配单元将检测从总线上接纳到的地址是否与TWAR寄存器中的7位地址相匹配。假如TWAR寄存器的TWI播送应对识别使能位TWGCE为1,从总线接纳到的地址也会与播送地址进行比较。一旦地址匹配成功,操控单元将得到告诉以进行正确地呼应。TWI能够呼应,也能够不呼应主机的寻址,这取决于TWCR寄存器的设置。即便MCU处于休眠情况时,地址匹配单元仍可持续作业。一旦主机寻址到这个器材,就能够将MCU从休眠情况唤醒。

最终一个部分是操控单元,它监听TWI总线,并依据TWI操控寄存器TWCR的设置作出相应的呼应。当TWI总线上发生需求应用程序干涉处理的事情时,TWI中止标志位TWINT置位。一旦TWINT标志方位1,时钟线SCL的电平即被拉低,暂停TWI总线上的数据传输,让用户程序处理事情。在下列情况呈现时,TWINT标志位会被置位。

1、在TWI传送完START/REPEATED START信号之后

2、在TWI传送完SLA+R/W数据之后

3、在TWI传送完地址字节之后

4、在TWI总线裁定失利之后

5、在TWI被主机寻址之后( 播送方法或从机地址匹配)

6、在TWI接纳到一个数据字节之后

7、作为从机作业时,TWI接纳到STOP或REPEATED START信号之后

8、因为不合法的START或STOP信号形成总线过错时