单片机被广泛应用于工业操控,家电,消费电子,医疗电子,外表丈量等范畴,为应广阔初级电子工程师/单片机爱好者之需,本站盛大策划整合推出《单片机关键技能根底详解》系列技能文章,以后会连续推出其他章节,敬请广阔工程师朋友继续重视和留心。

一、关于C51单片机的中止号以及中止向量

1、中止号

2、interrupt 和 using 在C51中止中的运用

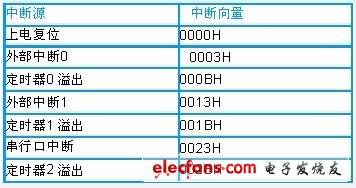

8051 系列 MCU 的根本结构包含:32 个 I/O 口(4 组8 bit 端口);两个16 位守时计数器;全双工串行通讯;6 个中止源(2 个外部中止、2 个守时/计数器中止、1 个串口输入/输出中止),两级中止优先级;128 字节内置RAM;独立的 64K 字节可寻址数据和代码区。中止发生后,MCU 转到 5 个中止进口处之一,然后履行相应的中止服务处理程序。中止程序的进口地址被编译器放在中止向量中,中止向量坐落程序代码段的最低地址处,留意这儿的串口输入/输出中止共用一个中止向量。8051的中止向量表如下:

二、CPU与单片机的复位电路的效果及根本复位方法

在上电或复位进程中,操控CPU的复位状况:这段时刻内让CPU坚持复位状况,而不是一上电或刚复位结束就作业,避免CPU宣布过错的指令、履行过错操作,也能够进步电磁兼容功用。

不管用户运用哪种类型的单片机,总要涉及到单片机复位电路的规划。而单片机复位电路规划的好坏,直接影响到整个体系作业的可靠性。许多用户在规划完单片机体系,并在实验室调试成功后,在现场却呈现了“死机”、“程序走飞”等现象,这首要是单片机的复位电路规划不可靠引起的。

根本的复位方法

单片机在启动时都需求复位,以使CPU及体系各部件处于确认的初始状况,并从初态开端作业。89系列单片机的复位信号是从RST引脚输入到芯片内的施密特触发器中的。当体系处于正常作业状况时,且振动器安稳后,假如RST引脚上有一个高电平并坚持2个机器周期(24个振动周期)以上,则CPU就能够呼应并将体系复位。单片机体系的复位方法有:手动按钮复位和上电复位。

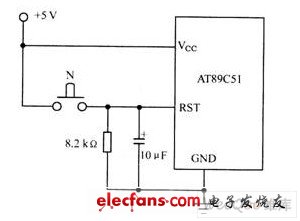

1、手动按钮复位

手动按钮复位需求人为在复位输入端RST上参加高电平(图1)。一般选用的方法是在RST端和正电源Vcc之直接一个按钮。当人为按下按钮时,则Vcc的+5V电平就会直接加到RST端。手动按钮复位的电路如所示。因为人的动作再快也会使按钮坚持接灵通数十毫秒,所以,彻底能够满意复位的时刻要求。

图1

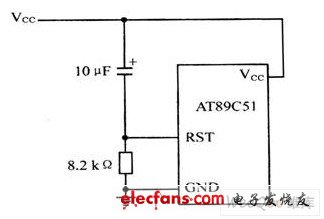

2、上电复位

AT89C51的上电复位电路如图2所示,只要在RST复位输入引脚上接一电容至Vcc端,下接一个电阻到地即可。关于CMOS型单片机,因为在RST端内部有一个下拉电阻,故可将外部电阻去掉,而将外接电容减至1?F。上电复位的作业进程是在加电时,复位电路经过电容加给RST端一个时刻短的高电平信号,此高电平信号跟着Vcc对电容的充电进程而逐步回落,即RST端的高电平继续时刻取决于电容的充电时刻。为了确保体系能够可靠地复位,RST端的高电平信号有必要坚持满足长的时刻。上电时,Vcc的上升时刻约为10ms,而振动器的起振时刻取决于振动频率,如晶振频率为10MHz,起振时刻为1ms;晶振频率为1MHz,起振时刻则为10ms。在图2的复位电路中,当Vcc掉电时,必定会使RST端电压敏捷下降到0V以下,可是,因为内部电路的约束效果,这个负电压将不会对器材发生危害。别的,在复位期间,端口引脚处于随机状况,复位后,体系将端口置为全“l”态。假如体系在上电时得不到有用的复位,则程序计数器PC将得不到一个适宜的初值,因而,CPU可能会从一个未被界说的方位开端履行程序。

图2

3、积分型上电复位

常用的上电或开关复位电路如图3所示。上电后,因为电容C3的充电和反相门的效果,使RST继续一段时刻的高电平。当单片机已在运转傍边时,按下复位键K后松开,也能使RST为一段时刻的高电平,然后完成上电或开关复位的操作。

依据实际操作的经历,下面给出这种复位电路的电容、电阻参考值。

图3中:C:=1uF,Rl=lk,R2=10k

图3 积分型上电复位电路

三、单片机双机并行通讯中所遇问题

1 导言

本体系选用的CPLD为 ATMEL公司出产的ATF1540AS器材,该器材是一种高功用、高密度复合可编程逻辑器材,简称CPLD,它运用ATMEL 的电可擦除存储器技能,有 64个逻辑宏单元和68个I/O端口,很简略和多个TTL、SSI、MSI、LSI和经典的PLDS组合运用。每个宏单元包含积项和积项多路挑选器、 OR/XOR/CASCADE逻辑、触发器、输出挑选和使能、输入逻辑阵列五个部分。ATF1504AS的增强选路开关增加了可用的门计数,进步了管脚锁存规划修正的成功率。

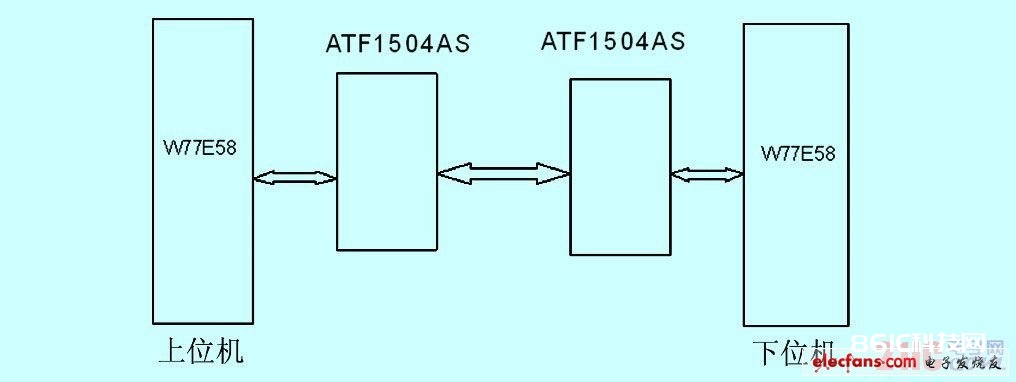

图1 双机通讯框图

2 体系结构

体系的CPU选用W77E58,由ATF1504AS构成通讯接口,体系框图如图1所示。

2.1 问题提出

电脑刺绣机为到达杰出的人机界面交互功用,选用上下位机方法,下位机首要进行绣花动作的操控,上位机首要进行把戏的盯梢。为了完成绣花的一起在液晶屏上进行绣花盯梢,单CPU方法存在体系资源透支, CPU处理数据将好不简单,所以提出了选用双CPU的作业方法,但一起带来一个问题—双CPU的通讯问题。

2.2 解决方案

(1) 选用串行通讯方法

长处:在由单片机组成的多机方法中,串行接口方法是最常用的。串行通讯方法接口电路简略,能够便利完成长间隔传输。抗搅扰才能比较好。

缺陷:传输数据慢,不合适实时数据传输。在数据传输要求高的情况下,简略形成瓶颈阻塞现象。

(2) 选用并行通讯方法

长处:并行通讯传输数据快,合适进行实时操控。

缺陷:抗搅扰才能差,不合适长间隔传输,最大间隔不超越5m。

因为本体系对数据传输的实时性要求比较高,而且上下位机之间的间隔不超越3m,进行恰当的抗搅扰办法,彻底能够到达体系的要求,所以确认选用并行通讯方法。

2.3 具体办法

(1) 选用ATF1504AS(可编程逻辑器材)进行并行通讯,削减分立器材所发生的杂散%&&&&&%而带来的噪声搅扰。

(2) 在输入数据端加斯密特电路(74LS14),将外部传输线上耦合噪声滤除去。然后进步总线接纳的抗搅扰功用。

(3)选用三态门驱动方法能够进步总线的抗搅扰才能,因为三态门有三种状况输出,既所谓的低阻高电平、低阻低电平、高阻态(禁态)。因为三态门的输入具有的三态性,所以使三态门的信号源的担负减轻。有利于进步速度和抗搅扰才能。

3 双CPU通讯原理规划

3.1 双CPU通讯原理图

从图2双CPU通讯原理图中能够看出,在输入接口上都接上74LS14斯密特电路和74LS244三态门驱动器,以进步抗搅扰才能。在SRZB、SCYX(上位机)及SRZB、SCYX(下位机)的握手信号线上接入74LS14斯密特电路,以进步抗搅扰才能。

图2 双机通讯原理图

3.2 ATF1504AS内部原理图

因为篇幅有限,仅列出上位机的ATF1504AS的内部原理图如图3,下位机的ATF1504AS的内部原理图与此相相似。