本文作者:Ryan CurranADI公司精细转化器部分产品使用工程师

以低吞吐量运转SAR ADC能够完成多种优势。经过添加转化操作之间的时刻,能够放宽体系滤波器要求,添加获取输入信号及从ADC抽取数据的时刻。由于ADC的收集周期是转化周期中读取数据最常用的区域,因而,延伸收集周期将放宽数字主机的要求。能够选用主机输出-从机输入(MOSI)时钟速率较慢的低端处理器。例如,AD7980 16位SAR ADC的额定采样速率最高为1 MSPS。

ADC的繁忙周期的最大额定值为710 ns,读取数据的时刻只剩下290 ns。要输出16位数据要求时钟周期不超越18 ns(或许不低于55 MHz左右)。但是,假如器材运转时的吞吐量为100 ksps,成果会使收集时刻(数据读取周期)从290 ns增至9290 ns。下降ADC采样速率后,能够放宽串行时钟要求,并把最小串行时钟频率改为2 MHz左右。在放宽数字主机要求以外,延伸收集时刻后,由于添加了树立时刻,因而,还能够挑选运用低功耗和低带宽ADC驱动器。

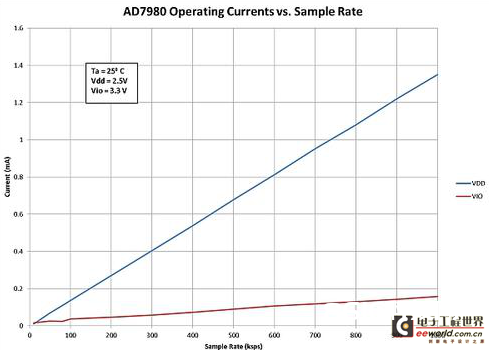

只需ADC支撑需求的体系接连时刻信号带宽,就能够考虑运用额定最大吞吐量较低的ADC(如AD7988-1),以下降体系本钱。AD7988-1是与AD7980同系列的一款100 ksps SAR ADC器材,它以较低的价格供给了相同的功能。如图1所示,器材的功耗与采样速率呈线性关系,由于大都功耗发生在活泼转化周期中。削减转化进程的次数,耗费的电量也会削减。速率为100 ksps时,AD7980(或AD7988-1)的功耗约为AD7980以1 MSPS的速率采样时的十分之一。

图1:AD7980作业电流与采样速率

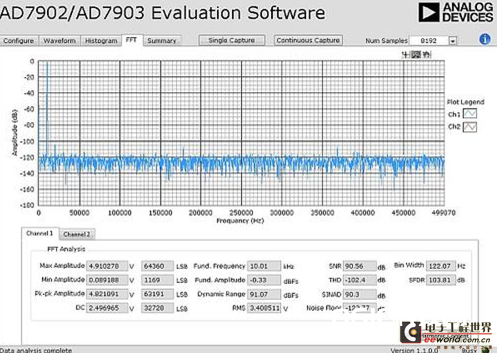

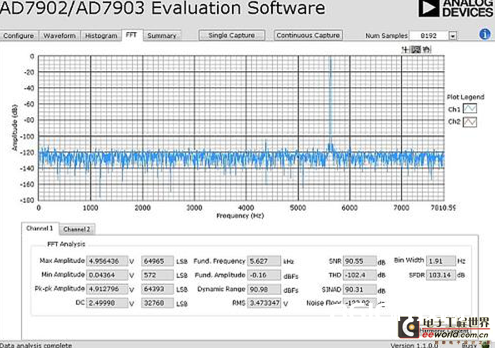

在单通道16位伪差分AD7980以外,ADI系列一起供给AD7902。这是一款双通道16位伪差分同步采样ADC,其额定采样速率为1 MSPS。在传达时刻等使用中,能够使用同步采样体系来抽取信号相位信息。咱们收集了AD7902以1 MSPS和15.625 ksps(1 MSPS的1/64)的速率对10 kHz信号音采样时的实验室成果。运用等式4,欠采样10 kHz信号音的基频应该出现在DFT频段中,该频段跨度为5.625 kHz。能够看出,在契合奈奎斯特规范的采样与欠采样装备之间,无起伏信息丢掉。但重构信号将为原始接连时刻输入的榜首奈奎斯特区混叠表明。

图2:AD7902的通道1(以1 MSPS对10 kHz信号音采样)

图3:AD7902的通道1(以15.625 KSPS对10 kHz信号音欠采样)

欠采样或许具有优势的另一个比如是多通道次序采样数据收集体系。这些体系一般由一个SAR ADC构成,带有一个多路复用模仿前端,以固定距离按已知次序转化。在这种状况中,各个通道的有用采样速率以体系中使能通道数的函数下降。例如,在一个八通道体系中,假如SAR ADC运转于1 MSPS下,则每隔八个样本代表一个相应的通道。因而,给定通道的采样速率仅为1 MSPS的1/8(125 ksps)。能够看到,在一个多路复用次序采样体系中,单个通道的奈奎斯特频率是怎么快速下降的。

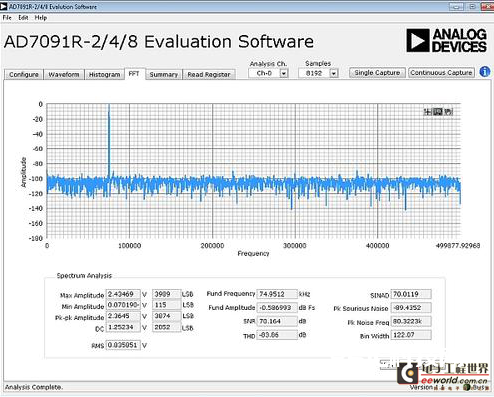

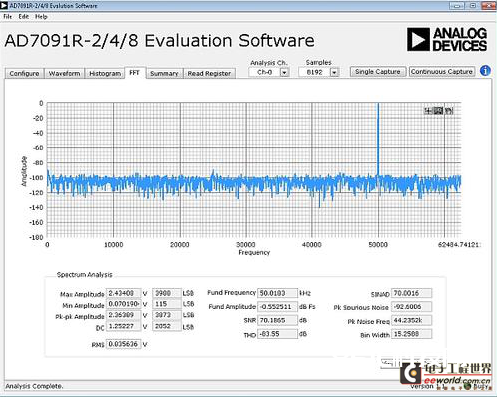

ADI公司供给AD7091R-8,这是一款超低功耗的12位、八通道1 MSPS SAR ADC,内置一个基准电压源和一个用户可编程的通道序列器。该器材选用4 mm x 4 mm LFCSP微型封装,作业于3 V电源和1 MSPS采样速率时,其功耗不高于1.7 mW。在AD7091R-8上,假如使能悉数八个通道,器材就会按从通道0到通道7的次序,主动重复次序采样。当ADC的采样速率为1 MSPS时,每个通道将以125 ksps的速率采样。因而,相对于1 MSPS单通道体系,给定通道的奈奎斯特频率从500 kHz下降到62.5 kHz。在多路复用器的一个通道上监控75 kHz信号音,成果会发生接连时刻信号的混叠表明,其基频为50 kHz。如后续各图所示,当经过使能AD7091R-8上的额定通道批改奈奎斯特规范时,动态功能并未下降。

图4:AD7091R-8监控75 kHz信号音(仅使能一个通道)。

图5:AD7091R-8监控75 kHz信号音(使能八个通道,通道采样速率为125 ksps)。

本文论述了这样一种主意:在通讯体系以外,有些使用能够用到欠采样理论。这些使用或许包含RMS-DC转化、沟通应变计、传达时刻、超声电平丈量和多路复用采样。用SAR ADC完成欠采样体系或许带来巨大的功能和功耗优势。不光能够放宽体系的整体约束,一起还能完成电路的整体目标。