IIR数字滤波器在许多范畴中有着宽广的使用。与FIR数字滤波器比较,它能够用较低的阶数取得高选择性,所用存储单元少,经济而效率高,在相同门级规划和相同时钟速度下能够供给更好的带外衰减特性。下面介绍一种在FPGA上完成IIR数字滤波器的办法。

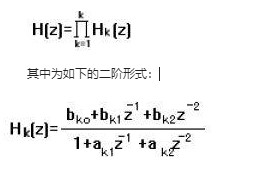

IIR数字滤波器的结构 恣意阶的IIR滤波器可通过数学分化,表明为:

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/zhishi/moni/338190.html