想必咱们经过之前的SDSoC系列文章,现已了解到怎么构建一个SDSoC开发渠道,并了解了SDSoC快捷的开发流程,可以说舞台现已搭好,现在就该你去完结自己的规划开发大“秀”了!

咱们仍是经过一个使用典范,来看看SDSoC在实践的规划开发作业中是怎么支撑你的“扮演”的。

因为SDSoC规划施行上的灵活性,它被作为视频处理的抱负渠道,经过它可以创立一个优化的视频处理体系,在处理功用、本钱、功耗和开发时刻等要素之间完结平衡。

详细地讲,你可以在规划中将那些像素级的、功用要求较高的处理作业可以放在PL(可编程逻辑)中完结,一起由PS(处理器体系)去背负那些非要害的、体系级的处理作业,比方文件处理和帧级的视频处理。

一起,SDSoC丰厚的规划资源这时也会帮到你。OpenCV现已与SDSoC严密地集成在一起,它可以供给丰厚、强壮的视频处理函数。

赛灵思供给了50+高度优化的OpenCV函数(被称为xfopencv库),协助用户加快其视频处理使用开发进程。其他经过SDSoC由HLS高档归纳引擎生成的函数,也可以放在FPGA可编程逻辑中进行加快。

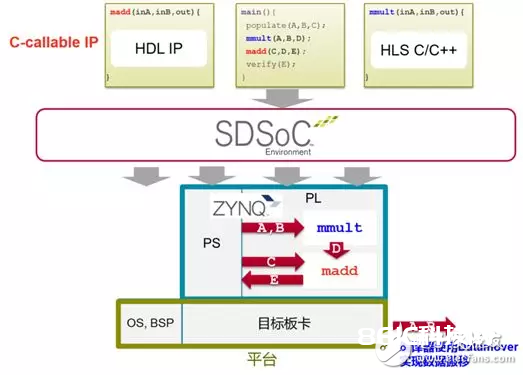

图1,SDSoC使用开发暗示(图片来历:赛灵思)

咱们再来将SDSoC使用开发的整个进程做个整理。

首要,开发者可以将需求在PL中加快的功用由C/C++写成算法,或是经过Vivado HLS生成IP,也可以是由HDL硬件描绘言语写成的C言语可调用的IP,并将这些规划源代码导入SDSoC。

然后,咱们对需求完结的功用进行软、硬件分区,这个进程用户只需在SDSoC中挑选并指定那些需求硬件加快的功用函数即可,非常便利。

接下来,SDSoC会依据用户的软硬件分区来生成PS和PL之间的DataMover、装备硬件接口和软件驱动,输出成Vivado IPI工程,一起供给全体系功用剖析和预算,悉数作业都由体系主动完结。然后,用户可以依据需求对体系完结方法进行干涉和改动,以到达满足的作用。

最终,SDSoC可以输出整个规划的FPGA比特流文件和可以用来发动操作体系的软件引导映像。

最终总结一下:SDSoC并非要替代曾经那些咱们现已熟知的Zynq SoC独立开发工具,而是将它们集成在了一个一致的开发环境中,并供给一个真实端到端的优化规划流程,让曾经需求不同开发团队花费很多时刻协作完结的杂乱作业,得以简化,也让更多没有FPGA规划经历的体系架构和软件工程师,可以轻松驾御Zynq SoC这个全可编程规划渠道,在这个立异的渠道架构上,开端他们的扮演!