导言

捷联惯导中的航姿计算机完结数字渠道导航,需求在杂乱运算的一起还能够高速、精确地完结多种传感器丈量数据的收集以及航姿成果和体系状况的传送。一般的做法都是用一片或多片 DSP芯片来完结,可是当数据接口较多并且数据传输频率较高时,这类体系的实时性就难以得到确保;而 FGPA具有丰厚的硬件资源,能够真实完结多模块并行作业,并且能够到达较高的作业频率。别的,用 FPGA规划航姿计算机,还具有以下杰出的长处:低成本、低功耗、小体积、可从头编程、晋级便利、VHDL 规划电路可复用等。本文详细介绍了在接口较多的航姿计算机中,怎样规划 FPGA使得多种通讯接口功用都能实时牢靠地完结,具有实践工程含义。

1、体系全体规划

图 1为该捷联航姿体系的硬件结构框图。该体系需求高速、实时地收集多种传感器(包含大气传感器、IMU、磁罗盘)的丈量数据,以及一些有关的模仿量,用于 DSP中高精度的航姿解算,一起也需求将航姿信息和体系信息发往多个设备(包含飞参记录仪、显现外表和DS)发送。收集数据需求一起用到的接口包含ARINC429、RS422、SPI、与 DSP并行接口等多种接口;如此多数量、多品种的接口的完结还有必要确保精确性和实时性。这整个体系的时序、逻辑操控都是由 FPGA完结的,DSP(选用 TI公司的TMS320C6713)作为从处理器专门用于航姿解算。本体系中选用的 FPGA芯片为 ACTEL公司 PA系列中的 APA300芯片,用 VHDL言语在 LibroIDE环境下对该芯片进行开发。

2、多种工业接口的 FPGA完结

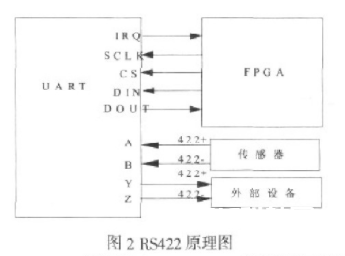

(1)RS422通讯接口。RS422规范是运用差分传输办法提高通信间隔和牢靠性的一种通讯规范。该航姿计算机需求用 RS422接口与IMU、大气传感器、磁罗盘、无线电航表等六个外部设备通讯。因为 RS422能够支撑双作业业办法,为了充分运用资源,因而规划了四个彻底相同的并行的接口模块,其间每一个接口模块都是通过 FPAG操控 MAX3140芯片得以完结(如图2);一起出于规划功率的考虑,只规划了一个通用的实体,而让每一个操控模块都作为该实体的一个实例。这样,尽管这四个模块的结构彻底相同,可是在顶层实体中施加不同的操控,就完结了两个单工和两个双工的作业办法。该通用的实体依照 MAX3140的作业时序图,通过操控和监测 UART的五个管脚(SCLK数据接纳时钟、CS片选信号、DIN操控数据输入、IRQ中止、DOUT数据输出),完结对芯片的上电自检和对信号的接纳发送;顶层实体并行地操控四个实体的作业,然后互不影响地完结了上述多路信号的接纳和发送。

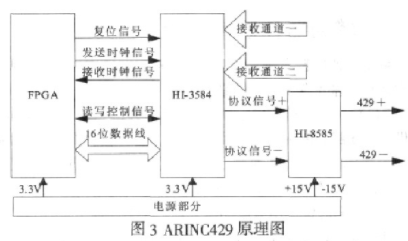

(2)ARINC429通讯接口。ARINC429协议规则了航空运输工业、航空电子体系等体系间的数字数据传输规范,是航空体系电子通讯中一种重要的接口。本体系需求通过 ARINC429接口接纳主惯导的丈量数据,一起通过 ARINC429接口将飞翔参数发送给记录仪。出于对通讯牢靠性的要求,本规划中相同选用操控接口制芯片的办法完结;通过对市面上为数不多的 429芯片进行长时刻的实验验证,终究选用美国 HARRIS公司的 HI-3584和 HI-8585芯片组合的办法。该芯片也支撑双工办法。在 FPGA中依照 HI-3584的作业时序图,规划了一系列并行进程,用于操控和监测 HI-3584的复位信号、发送接纳时钟信号、读写操控信号和 16位的数据信号(如图3)。然后完结对 HI-3582的上电自检、一个通道 429信号的接纳和一个通道429信号的发送。

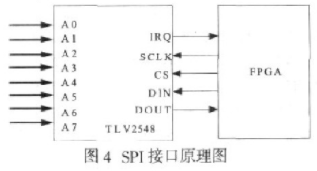

(3)SPI接口。SPI接口是一种高速、串行、全双工、同步传输办法。一般由一个主设备和一个或多个从设备通过中止、时钟、输入数据、输出数据和片选信号等 5个管脚完结。本规划需求用 AD采样芯片收集模仿量,所选的 AD芯片就是以 SPI办法与 FPGA通讯的。该 AD采样芯片为TI公司的TLV2548芯片,8通道、12位、采样频率200ksps。在FPGA中依照TLV2548的作业时序图,规划了一系列并行进程,用于操控和监测 TLV2548的中止信号、接纳时钟信号、片选信号、数据输入信号和数据输出信号(如图4)。然后完结对 8路模仿量的收集。本规划开端选用外部参阅,发现用于分压的精细可调电阻会随时刻改动阻值,较严重影响精度,因而终究运用内部参阅,真实确保了模仿量的牢靠性。别的,所用的内部晶振供给高频采样,使得数据更新率高于1M,然后确保了数据的实时性。

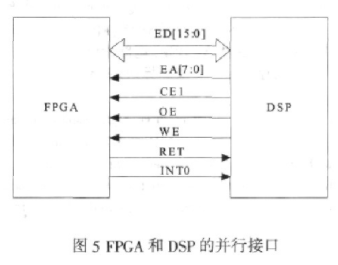

(4)与 DSP的并行接口。并行接口是最常用的一种通讯办法之一。FPGA和DSP之间的数据通讯通过 16位并行接口完结(原理图如图5)。首要,依据 DSP的时序,体系上电后需求对DSP进行不小于 200ms的复位。在体系正常作业时期,当 WE=0写有用、CE1=0片选有用、 a21=1数据有用时,FPGA从总线上读取 DSP的数据,当 OE=0读有用, CE1=0片选有用, a21=1数据有用时,FPGA将数据放在总线上等候 DSP读取。FPGA读、写数据都依据 DSP的 EA信号来标识所操作的数据地址。尽管体系中的数据量比较大,可是为了进步实时性和牢靠性,在FPGA中没有运用 FIFO或许 RAM来存储数据,而仅仅用 FPGA中的变量来暂时存储,本规划中也终究证明了该规划的可用性,这样也让 FPGA的硬件资源更合理利地得以运用。

3、全体时序的完结

本体系的实时性和杂乱性关于正确完结全体时序和作业逻辑提出了比较大的应战。现从以下几个方面阐明本规划的完结办法:

1 高速实时性:全体的并行规划,各个通讯模块简直彻底独登时作业,互不占用资源,然后使得高效性和实时性的要求得到了极大地满意。

2 全体时序有序:该航姿计算机的全体时序和全体逻辑都是让 FPGA中的顶层实体来操控完结的。体系大致时序和逻辑如下:上电后,FPGA操控体系完结各部件的上电自检后,各接口开端并行作业,依照自己的作业时序接纳、发送数据。其间,IMU数据大约每 10ms发送一次,FPGA每次接纳完 IMU数据后,与 DSP通过并行接口进行一次通讯。FPGA将最新的传感器丈量值发送给DSP,而 DSP将最新的航姿信息回传给 FPGA,终究FPGA通过 ARINC429接口传给外部。这样的规划确保了体系时序安稳、逻辑牢靠。

3 数据精确性:数据的精确也要求考虑到详细硬件上的问题。因为 FPGA中的逻辑门是有时刻推迟的,在这样实时的体系中就有必要严厉考虑门电路的延时,不然,很简单呈现如下相似的一些问题,例如,把刚接纳到一组丈量数据赋给变量是需求几纳秒到十几纳秒的时刻来安稳的,假如此刻正好遇上操作改动量的时钟触发,偶然就会引起野值数据,这些不确定的野值随时或许形成整个航姿结算的过错,因而需求依据详细时序修正,以确保根绝这类问题。

该体系的 FPGA规划现已通过模仿数据仿真实验、跑车实验得以验证,在数据精确性、实时性方面都得到了较好的满意。

责任编辑:gt