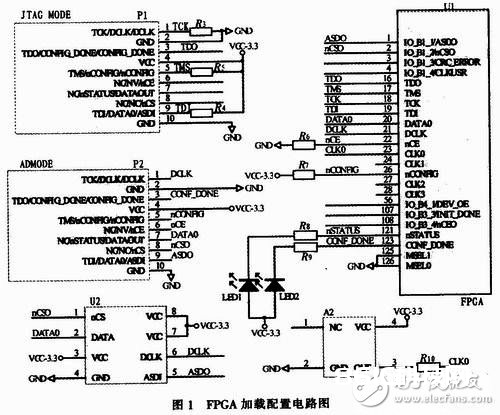

基于FPGA实现数字控制技术的程控直流变换器设计-传统变换器采用模拟硬件实现闭环反馈控制,获得稳定的电压和电流输出。模拟控制实时反应系统状态,响应速度较快,然而在测试技术领域和仪器产品中,模拟系统稳定性不能满足实际需要。为了获得高稳定性能,需要添加大量元器件进行环路补偿。而且,负载、环境变化以及反馈环路中元器件的寄生参数、漂移、老化、不一致性等因素在一定程度上影响着系统的稳定性[1,2]。因此,在需要更快实时反应速度的高性能变换器系统中,模拟控制对输入电压和负载的复杂变化,很难实现良好的瞬态响应,无法获得多状态下的稳定控制。

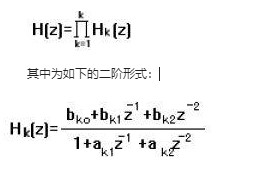

基于级联结构和VHDL语言的IIR数字滤波器在FPGA上实现设计-IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同时钟速度下可以提供更好的带外衰减特性。下面介绍一种在FPGA上实现IIR数字滤波器的方法。

基于可编程逻辑器件实现航姿计算机的设计-捷联惯导中的航姿计算机实现数字平台导航,需要在复杂运算的同时还能够高速、准确地完成多种传感器测量数据的采集以及航姿结果和系统状态的传送。通常的做法都是用一片或多片 DSP芯片来完成,但是当数据接口较多而且数据传输频率较高时,这类系统的实时性就难以得到保证;而 FGPA具有丰富的硬件资源,能够真正实现多模块并行工作,而且可以达到较高的工作频率。

通过利用CPLD/FPGA器件实现数字同步复接系统的设计-在数字通信中,为了扩大传输容量和提高传输效率,通常需要将若干个低速数字码流按一定格式合并成一个高速数据码流流,以便在高速宽带信道中传输。数字复接就是依据时分复用基本原理完成数码合并的一种技术,并且是数字通信中的一项基础技术。

FPGA应用于CMI编码逻辑的开发-出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案。在系统程序设计中,首先产生m序列,然后程序再对m序列进行CMI码型变换。在CMI码型变换过程中,采用专用寄存器对1码的状态进行了存储,同时利用m序列的二倍频为CMI编码进程提供时钟激励,最后输出CMI码型。

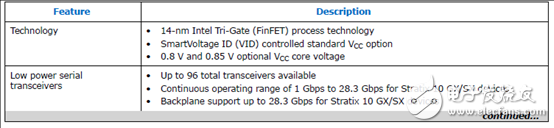

Stratix 10 SoC FPGA器件案例(应用、特性、电路图)-Intel公司的Stratix 10 SoC FPGA系列采用14nm三栅极(FinFET)和异构三维封装系统工艺技术,比以前高性能SoC FPGA提供2x核性能和节省多达70%的功耗, 单片核架构多达550万个逻辑单源(LE),多达96个全双工收发器通路,收发器数据速率高达28.3Gbps,嵌入eSRAM (45 Mbit)和M20K (20 kbit)SRAM存储器区块,基于PLL的分数合成和超低抖动LC振荡器,硬PCI Express Gen3 x16 IP区块,每个收发器通路中有硬10GBASE-KR/40GBASE-KR4 FEC,每个引脚的硬存储器控制器和PHY支持DDR4速率高达2666Mbps,以及硬定点和IEEE 754兼容

FPGA、PLD、CPLD之间的杂乱关系-fpga你可以理解成把一堆逻辑器件比如与门,或门,选择器等放在一个盒子里,盒子周围就是片子的引脚。通过逻辑编写,把许多的门和许多选择器等器件串联或并联引脚上。就等于把数电实验在fpga里面做。

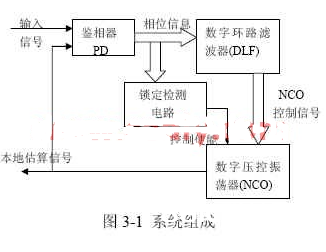

基于EPM7128SCL84-7芯片和quartus 2软件实现低频信号的锁相技术-在现代数字通信中, 数据传输,时钟校时等问题中很重要的一个方面是信号的同步。而同步系统中的核心技术就是锁相环。通常商用的全数字锁相环(DPLL)的关键部件是电荷泵和数字延迟线。电荷泵将数字鉴相器得到的相位差信息以电荷的方式累积起来,并根据积累的电荷量控制数字延迟线的反馈环,从而获得相应的本地估算时钟。即使是微小的相位差,也会导致电荷泵的电荷的累积。因此,这种技术实现的锁相环可以达到很高的同步精度。