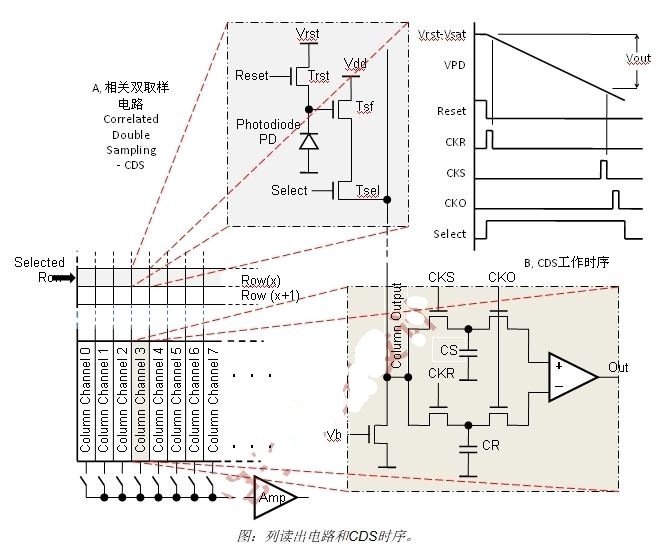

APS像素阵列中同一列的每一个像素上,都有一个同享的列像素信号输出端(Column Output),如图所示。每一列像素的这个同享输出端,都通过一个列模仿信号通道,处理和扩大这一列像素的图画信号。在这个通道中,首要有一个由模仿电压Vb偏置的恒流源,它是本列中每一个像素上源极跟从器Tsf通过挑选开关Tsel衔接的公共负载。在每一个列通道中还有一个重要的结构,便是相关双取样电路CDS(Correlated Double Sampling)。这是一个模仿信号处理电路,它对每个像素光电二极管PD上的电压信号,进行两次取样:第一次取样在PD刚刚被预置到电压Vrst – Vsat之后,当曝光刚刚开始的时间;第2次取样在曝光完结的时间。把与这两次相关信号取样的电压差值对应的电压,作为像素的光电信息输出,因此被称为相关双取样电路。

为什么要选用相关双取样电路处理图画信息?首要有必要了解CMOS成像器图画的固定图样噪声FPN(Fixed Pattern Noise)问题,在CMOS成像器的芯片上,每个像素和每个像素阵列的几许标准都有必要满意光学体系的要求。在当时,一般像素的标准在1.7微米到20微米之间,阵列标准在约2mm2到1000mm2数量级之间。在以微米、亚微米标准构建晶体管的CMOS芯片上,阵列面积的标准是适当“巨大”的。因为工艺不均匀的原因,每个APS像素上的有源器材,在如此大的阵列面积上,会有参数的随几许方位不同而有差异。例如,重置晶体管Trst的饱满电压Vsat,在阵列不同方位上像素中的差异,会引起光电二极管的重置电压Vrst – Vsat在阵列上的差异。这个差异会发生一个虚伪的图形,叠加在实在对应光学图画的信号上。这个虚伪的图形仅与阵列制作进程的不均匀有关,在制作进程完结后是不会改动的,与实在光学图画无关,因此被称为固定图样噪声FPN。相关双取样CDS电路的输出,对应于两次取样值的差,即曝光曲线的斜率,而不是一次取样的绝对值,因此消除了重置管Vsat差异而发生的固定图样噪声。

相关双取样CDS功用一般用开关电容扩大器电路完成,一种常见的CDS电路结构如图所示。列输出(Column Output)的模仿信号别离通过由CKR和CKS信号操控的采样模仿开关,存储在两个坚持电容CR和CS上。CKO信号操控别的两个模仿开关,一起把两个电容上的电压,别离衔接到差分扩大器的正负输入端,使扩大器输出与这两个信号的差值相关的电压。相关双取样CDS的作业时序如图中B所示,在像素的曝光进程开始时,当光电二极管PD被Reset操控重置到Vrst-Vsat电压后,开关CKR敞开,曝光初始的VPD信号电压被采样坚持到电容CR上,构成第一次采样。当曝光结束时,CKS敞开,VPD信号电压被采样坚持到电容CS上,完成第2次采样。然后CKO一起操控两个开关敞开,电压差VCS – VCR = Vout输入到差分扩大器输入端。从CDS的作业进程能够看出,输出的模仿信号值是两次采样的差值,而不是光电二极管曝光后的信号绝对值,然后消除了重置开关Trst参数散布的影响。

相关双取样电路CDS改进了固定图样噪声,被认为是CMOS成像器得到开展的要害一步。CMOS成像器的前期开拓者们,曾想象模仿信号处理能够广泛使用到APS像素阵列中去,而相关双取样电路是至今仍被最广泛使用在CMOS成像器规划中的一种模仿信号处理办法。

从列通道输出的图画光电信号,通过列模仿开关顺次转化输出。列通道输出顺次切换的进程,完成图画信息的水平扫描。图画模仿信号通过一个可变增益的宽带扩大器扩大,能够通过功率推进直接输出片外,作为模仿图画信号输出,也能够通过模数改换电路,输出数字图画信号。而数字图画信号还能够用各种先进的数字信号处理算法,在数字信号处理器DSP和微机中进行改进、增强、紧缩,甚至于图画识别和盯梢等等处理。下一期论题将讨论高清晰度和高速CMOS成像器。

责任编辑:gt