13.1规划需求剖析与功用界说

为了更好地剖析信号收集体系的规划需求,取得正确的体系功用界说,首要来剖析信号及信号收集体系的根本构成。

13.1.1信号与信号收集体系

信号一般能够分为模拟信号和数字信号,在信号收集中常常称为模拟量和数字量。依据信号存在方法的差异,又能够将模拟信号分为直流信号、时域信号和频域信号,将数字信号分为开关信号和脉冲序列。

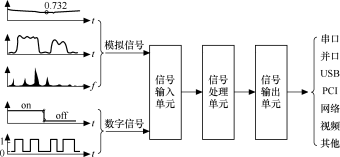

信号收集体系是将方针信号进行收集、处理并存储,构成计算机能够处理的数据格式,并终究进行各种方法输出的体系。典型的信号收集体系首要包括3个部分,即信号输入单元、信号处理单元和信号输出单元。

如图13.1所示为典型的信号收集体系的框图。

1.信号输入单元

信号输入单元是接纳信号源并将信号进行开始处理,构成数字信号的单元。关于模拟信号,一般需求进行信号调度及A/D转化。关于数字信号,一般进行数据宽度、时钟域改换等处理。

2.信号处理单元

信号处理单元是将信号输入单元输出的数字信号进行一系列处理的单元。一般运用CPLD/FPGA、DSP或许ASIC等单元进行信号处理。依据信号方法的不同,信号处理需求完结的作业也大不相同。

图13.1典型信号收集体系框图

3.信号输出单元

信号输出单元是将信号处理单元处理后的信号经过各种接口输出。一般能够经过USB、网络、ISA或许PCI总线等接口输出处理后的信号。

4.其他单元

此外,为了满意体系安稳运转,一个信号收集体系往往还包括数据缓冲区、时钟以及电源等相关的体系。

13.1.2规划需求剖析

更快、更精确地获取及处理尽量多的数据是信号收集体系一向寻求的方针。跟着传感器技能和信号处理技能的开展,高速传输和实时处理成为信号收集体系面临的新课题,也对典型信号收集体系的3个组成部分提出了更高的要求。

1.信号收集体系面临的新课题

高速传输首要影响的是信号输入和输出单元。关于数字信号,便是更高的输入频率和更多的输入通道数,关于模拟信号来说则意味着更高的分辨率,更高的采样频率以及更高的精度。一起高速传输还要求信号收集体系具有继续的以及突发的数据输出才干。

实时处理首要影响的是信号处理单元。它要求信号收集体系能够具有必定的数字信号快速处理才干,以便实时地为不同的输出接口供给适宜的数据格式。因为实时处理是信号收集进程的一个中间环节,因而实时处理的推迟不能形成信号收集的中止,这也对信号处理单元提出了更高的要求。

2.本体系规划需求剖析

在本事例中,信号收集体系需求收集的信号是数字信号。在高速信号传输中数字信号又常常以差分的方法存在,如LVDS。因而,本事例信号收集体系的信号输入单元应能够支撑单端的LVTTL电平信号以及差分的LVDS信号。

跟着PC机功用的不断提高,本来许多需求服务器乃至作业站才干完结的作业现在只需求一台简略的PC机就能够很快完结。因而,根据PC机的信号收集体系是本事例的另一个需求,也便是说信号收集体系的信号输出单元是根据PC机的。

别的,针对不同的使用场合,面临不同的信号方法,更多的用户期望信号收集体系变成愈加通用的体系,而不只是针对某种信号的专用收集体系。因而,具有二次开发即可编程才干的信号处理单元同样是本信号收集体系的一个需求。

13.1.3选型及功用界说

本事例挑选根据FPGA、PCI总线及LVDS接口的规划,能够满意高速收集及实时处理的要求。

1.信号处理单元选型

首要,选用AlteraCyclone系列FPGA归纳考虑了逻辑、存储器、锁相环(PLL)和高档I/O接口,是价格灵敏使用的最佳挑选。

在本事例中选用的CycloneEP1C6Q240是Cyclone系列FPGA的中级产品。具有5980个逻辑单元,内嵌20个M4KRAM块(128*36bit),具有2个PLL,最大支撑185个用户I/O管脚资源。

2.信号输入输出单元选型

其次,PCI总线是满意工业标准的使用最为广泛的扩展标准之一。它是一种具有多路地址线和数据线的高功用的32/64位总线,是PC机中必备的总线结构。

PLXTech公司供给的PCI9054器材是一种支撑32bit/33MHzPCI总线桥芯片。它契合PCI本地总线标准2.2版,突发传输速率到达132MB/s,本地总线支撑复用/非复用的32位地址/数据,支撑主形式、从形式以及DMA传输方法。

一起,为了完结信号收集体系对LVDS信号的支撑,选用DS90LV048/DS90LV047作为LVDS信号接纳/驱动器。它们均具有4路LVDS差分接纳/驱动功用,支撑高达400Mbit/s(200MHz)的转化速率。经过它们能够完结LVDS信号与FPGA支撑的CMOS/LVTTL信号进行转化。

3.其他单元选型

别的,为了满意PCI总线的DMA传输特性,需求在信号收集体系中参加必定量的缓冲区。收集的信号速率越高,需求的缓冲区容量越大,以确保不丢掉数据。在本事例中,选用了Micron公司供给的MT48LC2M32SDRAM作为缓冲区。它是一款64Mb(512K*32*4banks)全同步SDRAM。

至此,一个根据PCI总线,支撑高速LVDS/LVTTL信号收集,具有实时处理才干,可现场编程的信号收集体系完结选型。