跟着依据FPGA进行原型规划的杂乱性不断增加,商场对更好调试技能的需求也日益增加。FPGA原型规划可用于验证、前期软件开发、概念证明等,因此变得十分重要。它的首要职责仍然是履行这些使命,而不是企图找出因原型构建过错而形成的问题。

依据可用的规划或现有使命类型,或许需求不同的调试技能。选用适宜的调试技能还可以缩短FPGA规划的验证周期。

本文描绘了有关FPGA的一些调试技能,选用这些技能可以加速验证进程,文章一起也指出了它们的局限性。这些调试技能可以用于硅前验证进程中所面对的各种应战或问题,后边咱们将会评论。

RTL仿真

在RTL还没有彻底稳守时,原型规划的一个首要需求是拜访和监控内部信号的活动,这有助于找到形成问题的本源,不管问题是由于原型过错仍是RTL本身的一些反常形成的。

测验时,RTL仿真需求在模块周围树立一个完好的原型验证仿真环境,可以给予鼓励,满意内存要求(假如有的话),监控规划过错等。

图1显现了此类RTL仿真规划模型。

图1:RTL仿真模型

图字:要求 验证方案 原型RTL仿真 原型RTL模型 履行板上作业 找到Bug 去除bug履行一切作业

假定/优势

● 此调试办法十分适用,并且在处理规划规划问题时,可以进行调整,现在验证东西可以轻松地处理规划规划问题,但要求仿真时刻不能很长,不然会使这种作业简直没有ROI(出资回报率),而要装备杂乱的测验台。

● 假如是一个现已取得验证的规划,它能从头运用现有的验证测验渠道,这样就不需求从头开始构建,可以节约时刻和精力。

● 作业重点应该侧重于调整现有测验渠道,以便使其不需求任何大的更改,就可以运转验证测验套件。

● 可以缩小问题,挑选只运转失利仿真,削减对仿真的依靠,查看或许引起问题的信号的仿真波形。

局限性

● 假如是大规划规划,简直不或许查看规划中的每个信号、监控其行为。

● 选用这种办法的一个前提条件是,验证工程师或软件工程师应该对规划和内部信号具有杰出的洞悉。

● 此办法比较费时,并且需求软件开发人员支付额定的尽力。

● 在规划被分区的状况下,RTL仿真或许没有协助。假定咱们首要企图“再运用”顶层验证环境,并使其轻松为“受测设备原型”作业,要创立更多的层次和规划分区,则会需求进行额定的作业,以修正装置在独立验证环境中的内部信号探针。

● 调试触及杂乱处理的大规划快速流输出数据规划或许具有应战性,由于这个问题或许在规划层次的各个层级存在。

在杂乱的规划中,有必要考虑一些更好、更快的调试办法,咱们将在后边的章节中评论。

运用逻辑分析仪的硬件调试

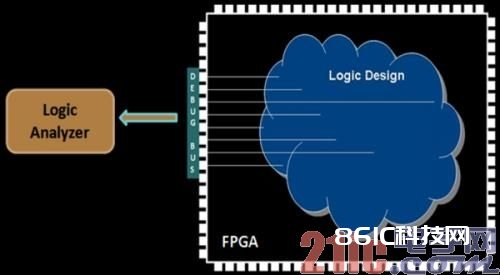

当调试总线坐落FPGA的外部引脚上,并经过逻辑分析仪调查它们时,硬件调试触及内部信号的呈现。这种调试技能对小型逻辑规划真的十分有协助,由于验证工程师也可以运用逻辑分析仪调查到内部规划信号,从而使调试愈加方便快捷。

图2显现了此调试模型。

图2:运用逻辑分析仪的硬件调试

图字:逻辑分析仪 逻辑规划

在这里,可编程的逻辑规划在方针体系中高速运转,可以在实在环境下查看逻辑行为。

假定/优势

● 如无法运用验证测验渠道仿真环境,可以选用这种办法进行调试,由于从头开始树立验证测验渠道的仿真环境或许既繁琐又费时。

● 此办法可以加速调试进程,由于它使验证工程师能查看内部规划信号的活动。

● 此办法供给了一个进入运转设备的窗口,不需求履行任何额定的软件使命。

● 由于一切验证状况都在FPGA板上履行,因此这种办法可以用于规划,不然一般需求适当长的仿真时刻。

局限性

● 规划人员需求手艺调试规划,每次都需求手艺修改进行重复调试。调试需求内部节点,没有在规划顶层就有必要将它们路由到顶层。

● 电路板上的可用引脚数量约束着探针数量。

● 此办法需求在逻辑分析仪查看器中输入信号称号,以便盯梢所显现的规划信号,因此变得很繁琐。

● 规划中的路由探针或许会导致设备运转或守时问题。

因此,用逻辑分析仪进行调试会十分耗时,损失生机,不能用于调试杂乱的规划。

刺进板上调试逻辑

具有杂乱逻辑施行的规划一般需求实时调试功用。这些都是更深化地洞悉规划所必需的,无需树立杂乱的测验渠道架构或施行外部硬件。

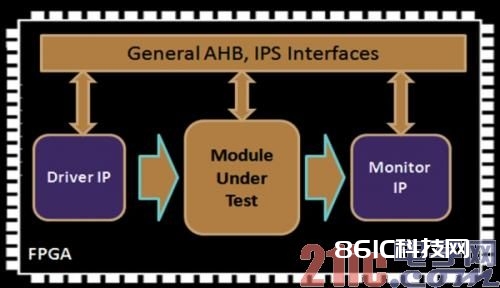

a) 刺进调试逻辑以及依据FPGA的规划只需在初始时支付一些一次性的尽力,因此可以节约调试时刻和本来很大的精力。这将触及编写驱动的归纳逻辑,监控可以与规划本身集成、并可以移植到FPGA的IP。图3显现了运用板上调试逻辑的调试模型。

图3:运用板上逻辑的调试模型

图字:AHB,IPS通用界面 驱动IP 测验中的模块 监控IP

别的,此板上逻辑可以使存储器映射,以便经过调试器提取成果或在运转中驱动输入。

b)可以选用另一种办法读取调试信号–使它们的存储器映射。然后,可以运用调试器读出这些值或经过CPU将这些值与这些信号的猜测值进行比较。假如从规划输出数据呈现的速度比读出的速度更快,则可以施行FIFO。输入数据能以更快的速率存储,以更低的调试器时钟频率读出。考虑到这两个时钟的频率,可以确认FIFO的深度。

假定/优势

● 垫或GPIO消除或许因外部衔接所引起的问题,因此不需求从外部驱动鼓励。

● 频率没有被外部驱动频率约束。

● 驱动鼓励和监控成果是实时的,使调试速度更快。

● 显现器彻底不需求取得外部引脚上的节点,由于可以从内部查看它们,运用那些存储器被映射的寄存器符号过错。

● 不需求位文件生成任何额定的循环来增加调试总线信号。

局限性

● 驱动器和显现器需求是可归纳的,因此或许无法在验证测验渠道从头运用它们。

● 驱动器和显现器所运用的逻辑或许会导致过度运用FPGA资源。

● 选用此办法或许呈现以下状况:假如其间任何一个有内存要求,并且超过了可用的FPGA资源,就不能施行驱动器和监视器。

● 增加额定的逻辑(如驱动器或监视器)或许导致难以满意规划所需的时序要求。

实时调试东西

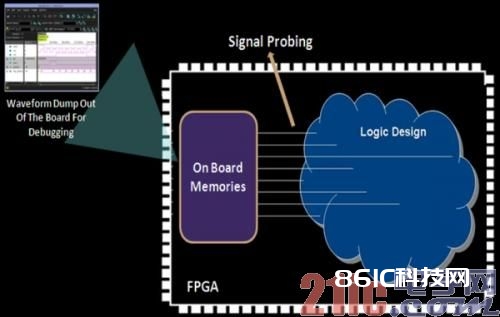

这些调试东西不需求在板的顶层提取内部规划信号,并供给信号勘探功用,以及实时调试。

在此类别中有多种东西,可用于实时调试设备。挑选适宜东西的最佳办法将取决于规划的杂乱性和功用以及所运用的FPGA技能。这些东西在规划中用于刺进探针,以便转储数据,并可操控发动数据存储的特定触发器。规划得到检测后,经过归纳、布局、布线在某个设备上施行,这样,东西供给的GUI界面可以用来查看成果。运用这些东西可调查到规划层次中的任何层级,因此不需求为了在规划顶层取得它们而履行额定使命。

这样的东西很少运用FPGA本身资源,像板上存储器,用于贮存数据,并且它们不需求任何外部硬件。图4显现了此调试办法。

图4:运用板上资源的调试东西

图字:将波形从电路板中倒出,进行调试 信号勘探 板上存储器 逻辑规划

但这类东西所面对的问题是:插装探针后,规划在作业频率和路由拥塞方面会有不行测的操作。

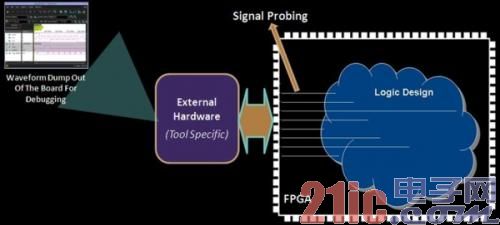

当然还有一些其他东西,也具有实时功用,可灵敏装备运转触发器。这些东西都配有相关硬件,因此供给必要的数据贮存,不运用任何FPGA资源。图5显现了这种调试办法。

图5:运用外部硬件的调试东西

图字:信号勘探 将波形从电路板中倒出,进行调试 外部硬件(特定东西) 逻辑规划

假定/优势

● 关于I/O数量相对较大的规划可以选用此调试办法,由于它不需求在电路板的顶层提取内部信号。

● 此办法可以用于规划仿真杰出、但一旦集成到FPGA中、就不显现预期行为的状况。相同,调试这些问题需求不只供给实时调试,并且还有信号勘探功用的东西。

● 这些东西使调试进程变得相对简单,由于它们一般将波形/数据转储为运用最常用的仿真东西可以翻开的格局。

● 这样的调试东西还能贮存在自己的相关存储器中捕获的波形,它耗费FPGA板的资源,因此一般不必约束规划。

局限性

● 必需装置外部硬件和软件。

● 调试节点有数量约束。

● 规划层次的可见性取决于用于贮存转储数据的存储器。

● 可取得的频率下降。

解决办法之一是:选用来自一个特定分层体或模块的插装信号创立同步build,这样,可以选用调试模块或块的信号在比特流上运转一组测验。在履行阶段遇到问题后,这肯定会节约创立build的时刻。

本文小结

很显然,现在还没有呈现公认的通用调试技能,并且没有合适一切规划验证的调试技能。不同的调试技能有不同的局限性和约束,可是,假如挑选妥当,这些调试东西/技能真的可以有助于削减调试作业,缩短调试周期。

缩短调试时刻或许成为加速硅前验证的一个巨大的里程碑。加速硅前验证是首要要求,这样才干满意上市时刻需求,可以推出第一个全功用硅。