0导言

在当今信息化的年代,在机器获取实际国际信息方面,图画因为具有信息面全、直观、便利直接的特色而遭到广泛的研讨。图画收集与处理体系在工业检测、智能操控、医学成像、安全监控、航空航天等方面得到了广泛的运用。人们在图画获取渠道上不断的进步图画传感器的功用,改进图画获取的硬件组件与体系结构;一起在图画的处理上提出一系列的新式或是改进的处理技能来改进图画的处理质量与处理速度,以便能够满意当时运用对图画质量、实时功用、精准操控等方面的要求。

现有的图画传感器芯片有CCD和CMOS两种类型。CCD图画传感器具有杰出的功用,但其外部电路杂乱,不适合于低成本体系;而跟着CMOS集成电路工艺技能的开展,CMOS图画传感器得到了快速的开展,与CCD比较,它具有制作工艺老练、易集成、低成本、低功耗、体积小以及运用简略等长处。跟着集成电路工艺技能的进步,CMOS图画传感器在分辨率、噪声等方面都有明显的改进,使得它在越来越多的范畴上得到运用,它适用于低功耗的小型图画收集体系。

现在很多的图画收集体系选用CPLD或许单片机作为图画收集的时序操控接口,如文献,或许是用DSP作为图画处理的主处理器,如文献。这二者在各自的方面都有各自的优势,但它们的专用性太强,CPLD与单片机在时序操控方面有优势而图画处理才能弱,DSP则是图画处理才能强而时序操控才能差。FPGA是介于专用集成电路与原有的可编程逻辑器材之间的一种半定制电路器材。它具有丰厚的I/O接口、低功耗、兼容CMOS和TTL电平、可重复擦写,易于在线调试等长处,能够使体系开发具有周期短,危险小,费用低的长处。它的时序操控才能强,在并行处理的算法方面具有较大优势,具有较强的图画处理才能,一起在嵌入式体系方面的运用也具有较好的远景。

USB总线接口技能是一种PC与外围设备进行高速通讯的接口,它具有能够即插即用、衔接便利简略、易于扩展外围设备以及高速传输等长处,适用于有很多数据传输的场合,满意图画传输数据量大的特色,一起作为一种通用串行总线,它的运用使得体系能够被移植到更多的运用场合傍边。

1体系硬件组成

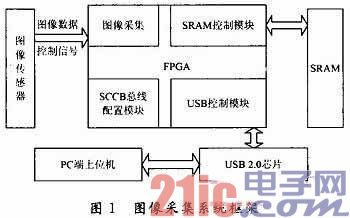

体系硬件的全体结构如图1所示,它包含有搭载有OV7620图画传感器的C3188模组、FPGA、SRAM存储器、USB2.0接口芯片、以及PC端上位机几部分组成。

在体系上电时,由FPGA经过模仿SCCB总线,完结对图画传感器的初始化作业;在完结初始化作业今后,FPGA开端在OV7620发生的时序信号操控下进行图画数据的收集,并将之存储在SRAM傍边;当存满一帧的图画后,在FPGA的操控下,图画数据由SRAM经过CY7C68013A传送到PC端,USB芯片被设置在从形式的作业状况下;上位机程序接纳来自USB芯片的数据并将之实时的显现,完结图画数据的收集与传输。

2OV7620的功用参数及初始化

OV7620是CMOS五颜六色/是非图画传感器。它支撑接连和隔行两种扫描方法,VGA与QVGA两种图画格局;最高像素为664×492,帧速率为30f/s;数据格局包含YUV,YCrCb,RGB三种,能够满意一般图画收集体系的要求。OV7620具有丰厚的编程功用,运用开发者能够经过SCCB操控总线来对芯片相关参数进行设置,以到达操控输出图画巨细、增益、色彩、爆光时刻、输出格局等,以使所取得的图画满意运用的需求。

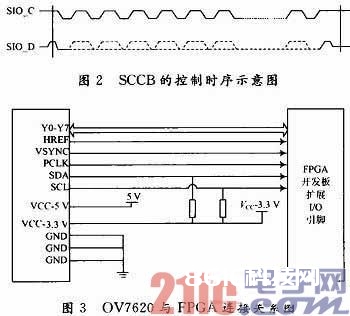

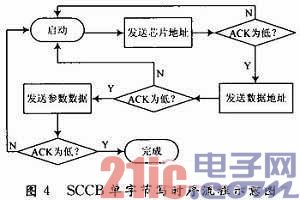

SCCB接口是选用一种简略、双向二线制的同步串行总线。它是简化的I2C协议,其间SIO-1是串行时钟输入线,SIO-O是串行双向数据线,别离相当于I2C协议的SCL和SDA。图中其间的SDA,SCL两根线因为是开漏输出,因而需求有上拉电阻,在本体系中接1kΩ的上拉电阻。SCCB的总线时序与I2C根本相同,它的呼应信号ACK被称为一个传输单元的第9位,分为Don’tcare和NA。Don’tcare位由从机发生;NA位由主机发生,因为SCCB不支撑多字节的读写,NA位有必要为高电平。别的,SCCB没有重复开端的概念,因而在SCCB的读周期中,当主机发送完片内寄存器地址后,有必要发送总线中止条件。不然在发送读指令时,从机将不能发生Don’tcare呼应信号,其二线制的操控时序与I2C相仿,如图2所示。

在FPGA傍边,选用一般IO口模仿SCCB的时序,因为本体系只需求在上电时对图画传感器进行初始化的参数设置,而SCCB的写时序与I2C的写时序彻底兼容,因而,在程序中只需求模仿I2C的单字节写进程。C3188模组与FPGA的衔接联系图如图3所示。程序中运用次序的方法,即将发送的数据逐位发送的方法来进行设置,其状况机如图4所示。

即将初始化的寄存器地址以及所要设置的值直接存放于parameter界说的参数中;在上电时,经过I2C程序将这些写到OV7620傍边,完结图画传感器的初始化作业。

3CY7C68013A芯片SLAVEFIFO形式固件编写

因为体系用于图画的收集,具有数据量大,实时性要求高的特色,因而选用USB2.0接口,以便能满意实时,高速的数据传输。为了到达最快的传输速率,运用SLAVEFIFO形式,在该形式下,USB芯片的数据传输不需求8051的参加,便于很多接连的数据传输,在这种形式下需求有一个外部的操控时序,而FPGA恰能供给相关的时序,一起为了能够与图画数据同步,选用外部输入时钟,同步传输方法,选用8位数据传输。在该运用中,寄存器EP2CFG装备了端点2作为IN端点传输FPGA来的数据至上位机,寄存器EP2FIFOCFG使能主动传输;寄存器EP6CFG装备端点6为OUT端点,寄存器EP6FIFOCFG使能主动传输;并在寄存器FIFOPINPOLAR中设置了端点的满标志为高电平有用,这是因为在刚上电下载完FPGA程序后,FPGA即对图画进行收集并存储至SRAM傍边,而上电时FPGA的引脚默以为高电平,假如没有设置高电平为EP2的满有用,则在下载USB固件之前FPGA会误以为是USB的端点一向处于非满状况而一向传送数据,这样,在下载完USB固件后,主机端所得到的图画就不能确保它是从一帧图画的第一个数据开端传输而是与下一帧的图画有必定的错位。在设置EZ-USBFX2LP为SLAVEFIFO形式的进程大致是:装备IFCONFIG[1:0]=11,先把SLAVEFIFO形式;复位相应端点,即运用FIFOREST寄存器;装备所要用的端点巨细,类型,以及传输方向,运用EPxCFG,式中x代表2,4,6,8;设置各端点的空标志,满标志和可编程标志值,运用PINFLAGAB和PINFLAGCD寄存器;装备是否使能主动传输以及传输的位宽,运用EPxFIFOCFG,式中x代表2,4,6,8;本运用中的USB固件程序的部分代码如下:

4FPGA对图画数据的收集、存储及对USB的传输操控

4.1FPGA对图画的收集操控

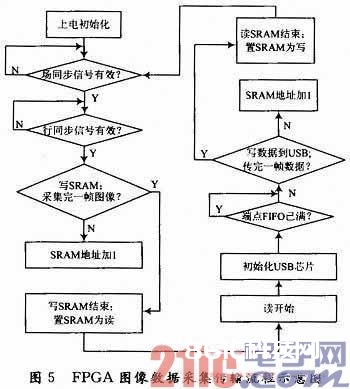

FPGA对图画的收集操控是经过OV7620的VSYNC,HREF,PCLK三个源同步时序信号来对图画进行收集。首先是在1个状况机中检测VSYNC信号,当VSYNC的高电平来暂时,初始化一切的内部寄存器,包含SRAM的地址寄存器,SRAM的写操控信号,数据总线读写方向的挑选信号,USB的写使能信号,内部计数寄存器等;等VSYNC降临之后,表明新的一帧开端了,接下来等候图画的行信号使能降临,当HREF到来之后,就能够将图画的数据写进SRAM傍边了,这个写进程需求两个CLK,在第一个时钟周期中更改SRAM的写地址,第2个CLK周期将衔接在数据总线上的图画数据写进SRAM中,一起对内部的图画计数器进行计数,这个进程中要在HREF为高电平的时分进行存储;当计数到达一帧,也便是153600B的时分完毕收集的进程,并更改相应的操控信号,预备USB的操作信号,进行FPGA对USB芯片的操控,将SRAM傍边的一幅完好的图画能过USB传至USB傍边,整个收集与传送的状况流程如图5所示。

4.2FPGA对USB芯片的操控

在FPGA完结了一幅图画的收集并将图画的数据存储在片外的SRAM傍边今后,接下来要做的作业便是将所存储的图画传给USB芯片,这个进程傍边,FPGA要操控SRAM的写信号,一起使能数据总线的方向为输出方向。FPGA对USB的写首先是花费一个CLK的时刻从SRAM傍边取出一个数据,之后在第2个CLK时刻内判别它的端点满标志,假如USB端点现已满了,则等候,假如非满,则拉低写信号使能信号一起地址计数器加1,回来上一个取数据的状况持续取下一个数据,直到传完一幅图片,之后回来初始的状况从头等新的一帧开端信号的到来。

5上位机读取数据

运用程序是体系与用户的接口,它经过通用驱动程序完结对外设的操控和通讯。本运用中运用VC++6.0进行开发。EZ-USBFx2LP开发套件供给了主机端驱动程序(cyusb.sys),傍边供给了便利便利的设备接口类,根据这些类,能够运用户快速的完结体系相应部分的开发。程序中运用单线程异步数据的传输,每次的传输取一帧图画,并显现在对话框中。

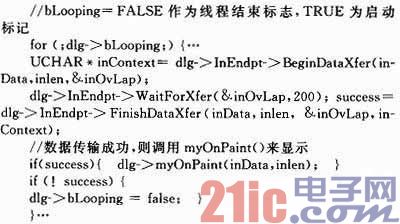

程序的部分代码如下,在该段代码中,首先是调用WaitForXfer函数发动异步传输,假如数据传输成功,则回来相应字节的数据,调用自界说的显现函数就能够将图画显现在对话框傍边,不然断开线程,完毕数据传输。以下为部分代码:

6体系测验成果

体系的硬件架构为:FPGA开发板运用北京威视锐科技有限公司的赤色飓风Ⅱ代RC2-1C6开发板,其板上搭载Altera公司的EP%&&&&&%6Q240C8芯片,配有Cypress公司的USB2.0芯片CY7C68013A、ISSI公司的IS61LV25616AL芯片,并供给了三组扩展接口JE1,JE2,JE3供用户运用,图画传感器芯片运用OmnniVisionCorporation的OV7620芯片。整个体系的衔接联系如图6所示,C3188板所需求的5V与3.3V电源由板上扩展接口JE1上的电源引脚供给,OV7620与FPGA开发板的数据经过JE3,JE2相连,传感器运用的SCCB装备线SCL,SDA经过外接1kΩ的上拉电阻至3.3V。

试验的部分图画如图7,图8所示,其间图7巨细为320×240,图8的巨细为160×240。

7结语

本文以FPGA为操控中心,介绍了CMOS图画传感器的数据收集与存储,并运用USB2.0芯片CY7C68013A进行数据的传输。FPGA为操控中心首要完结了OV7620的初始化作业,数据收集与存储以及CY7C68013A芯片的时序操控;USB2.0芯片作业在SLAVEFIFO形式下,便于图画数据的快速传输。充分利用了FPGA丰厚的接口资源以及USB2.0的高速传输特色。与文献比较,具有更快的传输速度,便于实时的监测。整个体系结构简略,便于保护扩展;而FPGA的参加可作为并行计算的渠道,关于图画数据的实时处理具有必定的优势。本体系可运用于如工业检测等需求高的图画处理速度以及实时的监测才能,而FPGA的运用使得它能够作为小型嵌入式体系,USB2.0接口的运用进步了体系有着较好的可移植性。