Intel公司的MAX 10 FPGA系列选用TSMC 55nm NOR闪存技能,容量从2K到50K 逻辑单元(LE),选用单个或双核电源电压和小尺度3x3mm和高I/O引脚数封装;器材具有全特性FPGA功用,支撑Nios II软核嵌入处理器,数字信号处理(DSP)区块以及软DDR3存储器操控器,内部存储双装备闪存,用户闪存存储器,集成了模数转换器(ADC).首要用在体系管理,I/O扩展,通讯操控,工业使用,轿车电子和消费类电子.本文介绍了Intel® MAX® 10 FPGA系列首要优势,器材平面布局图以及MAX 10 FPGA开发套件首要特性和电路图.

Intel® MAX® 10 FPGAs revoluTIonize non-volaTIle integraTIon by delivering advanced processing capabiliTIes in a low-cost, single chip small form factor programmable logic device. Building upon the single chip heritage of previous MAX device families, densities range from 2K – 50K LEs, using either single or dual-core voltage supplies. The MAX 10 FPGA family encompasses both advanced small wafer scale packaging (3 mm x 3 mm) and high I/O pin count packages offerings.

MAX 10 FPGAs are built on TSMC’s 55 nm embedded NOR flash technology, enabling instant-on functionality. Integrated features include analog-to-digital converters (ADCs) and dual configuration flash allowing you to store and dynamically switch between two images on a single chip. Unlike CPLDs, MAX 10 FPGAs also include full-featured FPGA capabilities, such as Nios® II soft core embedded processor support, digital signal processing (DSP) blocks, and soft DDR3 memory controllers.

Intel® MAX® 10 devices are single-chip, non-volatile low-cost programmable logic devices (PLDs) to integrate the optimal set of system components.

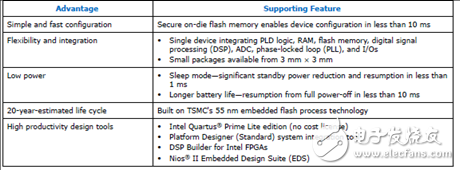

The highlights of the Intel MAX 10 devices include:

• Internally stored dual configuration flash

• User flash memory

• Instant on support

• Integrated analog-to-digital converters (ADCs)

• Single-chip Nios II soft core processor support

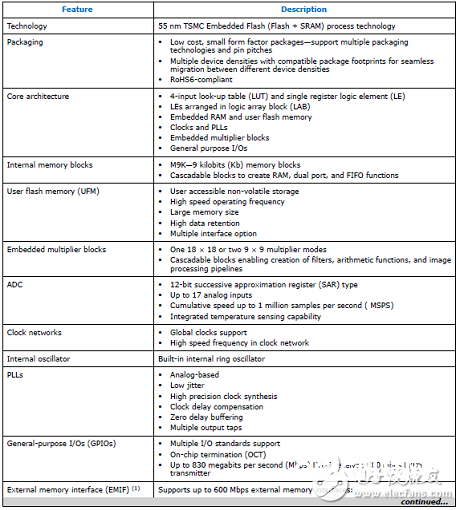

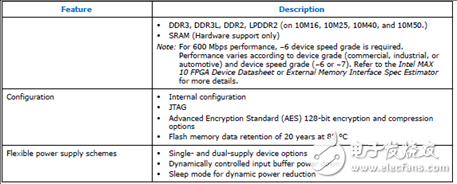

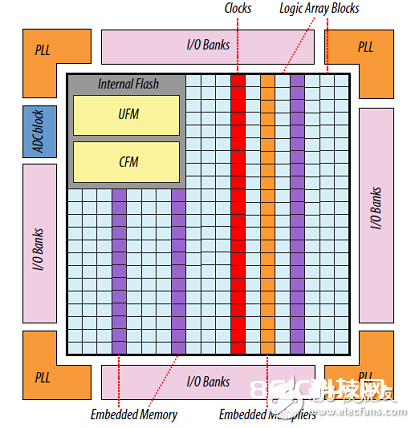

The MAX? 10 devices consist of the following:

• Logic array blocks (LABs)

• Analog-to-digital converter (ADC)

• User flash memory (UFM)

• Embedded multiplier blocks

• Embedded memory blocks (M9K)

• Clocks and phase-locked loops (PLL)

• General purpose I/O

• High-speed LVDS I/O

• External memory interfaces

• Configuration flash memory (CFM)

Intel MAX 10 devices are the ideal solution for system management, I/O expansion,

communication control planes, industrial, automotive, and consumer applications.

Intel® MAX® 10 FPGA系列首要优势:

图1. Intel® MAX® 10 FPGA器材平面布局图

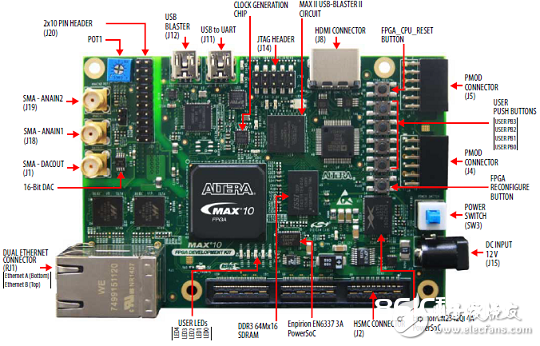

MAX 10 FPGA开发套件

The MAX? 10 FPGA development board provides a hardware platform for evaluating the performanceand features of the Altera? MAX 10 device.

The development kit includes a RoHS- and CE-compliant MAX 10 FPGA Development board with thefollowing components:

• Featured Devices:

• MAX 10 FPGA (10M50D, dual supply, F484 package)

• Enpirion? EN2342QI 4 A PowerSoC Voltage-Mode Synchronous Step-Down Converter withIntegrated Inductor Enpirion

• EN6337QI 3 A High-Efficiency PowerSoC DC-DC Step-Down Converters with Integrated Inductor

• Enpirion EP5358xUI 600 mA PowerSoC DC-DC Step-Down Converters with Integrated Inductor

• MAX II CPLD – EPM1270M256C4N (On-board USB-Blaster™ II)

• Programming and Configuration:

• Embedded USB-Blaster II (JTAG)

• Optional JTAG direct via 10-pin header

• Memory Devices:

• 64-Mx16 1 Gb DDR3 SDRAM with soft memory controller

• 128-Mx8 1 Gb DDR3 SDRAM with soft memory controller

• 512-Mb Quad serial peripheral interface (quad SPI) flash

• Communication Ports:

• Two Gigabit Ethernet (GbE) RJ-45 ports

• Ethernet Port A (Bottom)

• Ethernet Port B (Top)

• One mini-USB2.0 UART

• One high-definition multimedia interface (HDMI) video output

• One universal high-speed mezzanine card (HSMC) connector

• Two 12-pin DigilentPmod™ compatible connectors

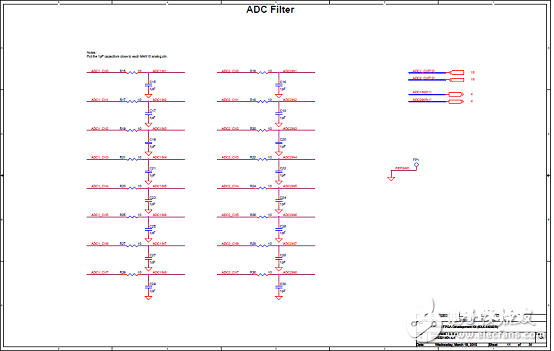

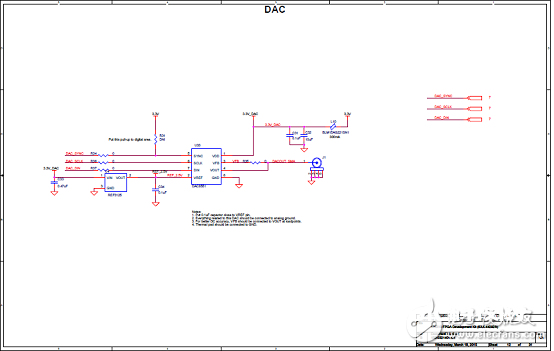

• Analog:

• Two MAX 10 FPGA analog-to-digital converter (ADC) SMA inputs

• 2×10 ADC header

• Potentiometer input to ADC

• One external 16 bit digital-to-analog converter (DAC) device with SMA output

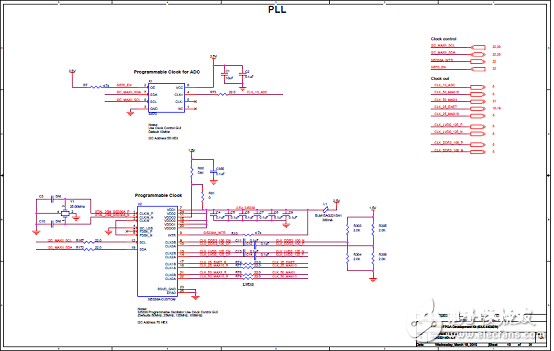

• Clocking

• 25 MHz single-ended, external oscillator clock source

• Silicon labs clock generator with programmable frequency GUI

• Mini-USB cable for on-board USB-Blaster™ II

• 2A Power Supply and cord

• Free Quartus? II Web Edition design software (download software and license from website)

• Complete documentation

• User manual, bill of materials, schematic, and board files

图2. MAX 10 FPGA开发板正面元件图

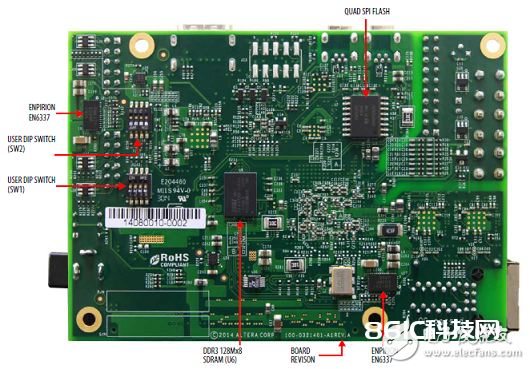

图3. MAX 10 FPGA开发板反面元件图

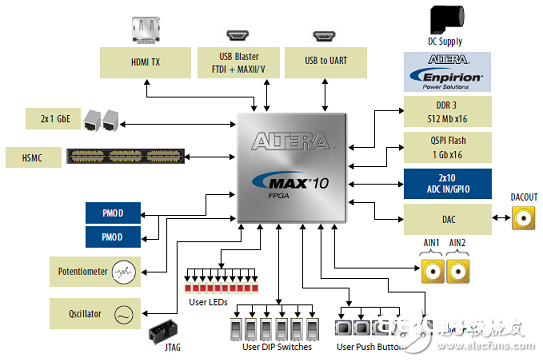

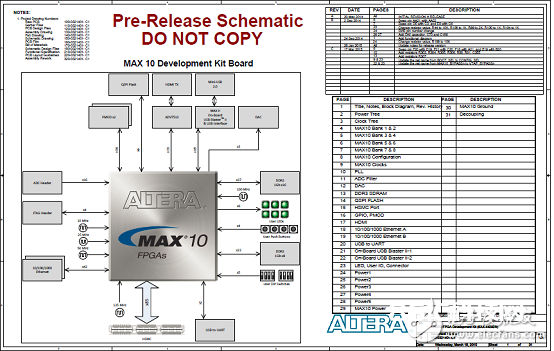

图4. MAX 10 FPGA开发板体系框图

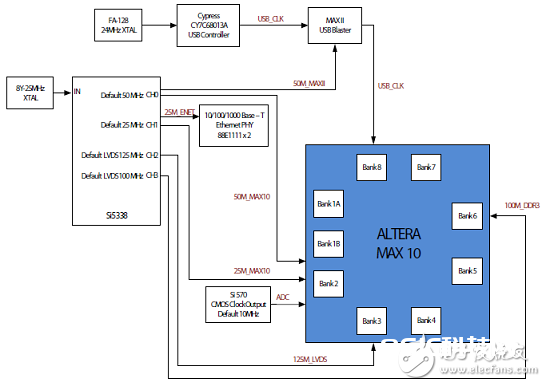

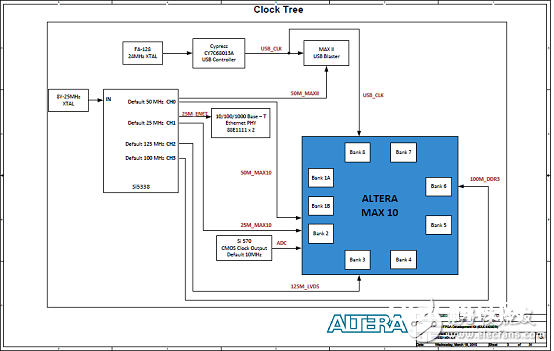

图5. MAX 10 FPGA开发板时钟框图

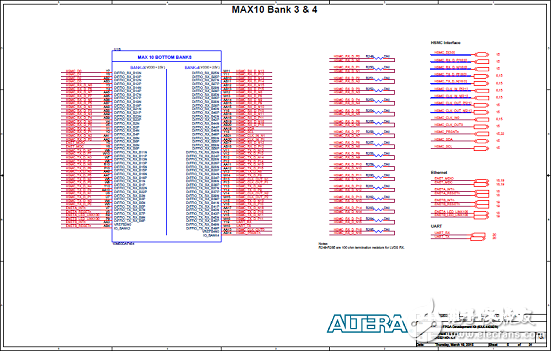

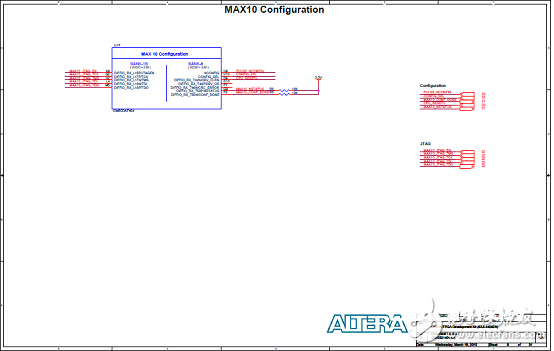

图6. MAX 10 FPGA开发板电路图(1)

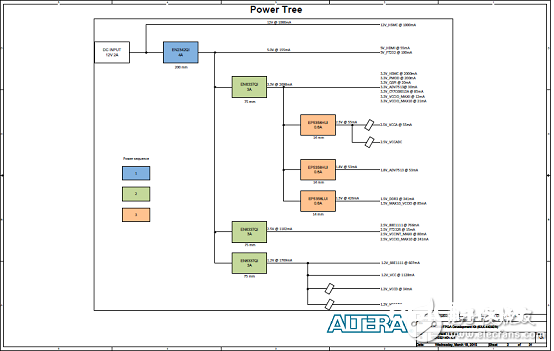

图7. MAX 10 FPGA开发板电路图(2)

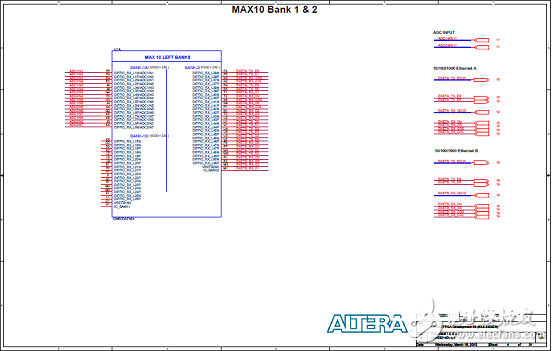

图8. MAX 10 FPGA开发板电路图(3)

图9. MAX 10 FPGA开发板电路图(4)

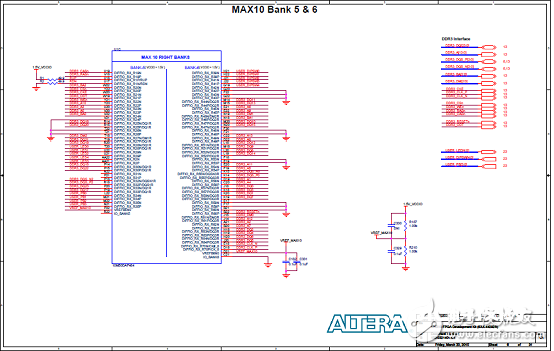

图10. MAX 10 FPGA开发板电路图(5)

图11. MAX 10 FPGA开发板电路图(6)

图12. MAX 10 FPGA开发板电路图(7)

图13. MAX 10 FPGA开发板电路图(8)

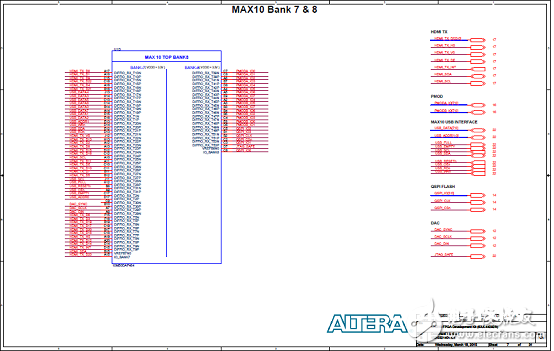

图14. MAX 10 FPGA开发板电路图(9)

图15. MAX 10 FPGA开发板电路图(10)

图16. MAX 10 FPGA开发板电路图(11)

图17. MAX 10 FPGA开发板电路图(12)

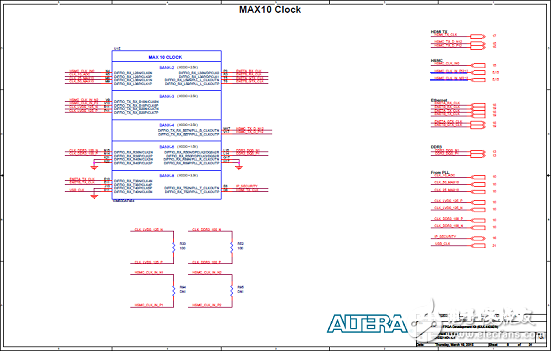

图18. MAX 10 FPGA开发板电路图(13)

图19. MAX 10 FPGA开发板电路图(14)

图20. MAX 10 FPGA开发板电路图(15)

图21. MAX 10 FPGA开发板电路图(16)

图22. MAX 10 FPGA开发板电路图(17)

图23. MAX 10 FPGA开发板电路图(18)

图24. MAX 10 FPGA开发板电路图(19)

图25. MAX 10 FPGA开发板电路图(20)

图26. MAX 10 FPGA开发板电路图(21)

图27. MAX 10 FPGA开发板电路图(22)

图28. MAX 10 FPGA开发板电路图(23)

图29. MAX 10 FPGA开发板电路图(24)

图30. MAX 10 FPGA开发板电路图(25)

图31. MAX 10 FPGA开发板电路图(26)

图32. MAX 10 FPGA开发板电路图(27)

图33. MAX 10 FPGA开发板电路图(28)

图34. MAX 10 FPGA开发板电路图(29)

图35. MAX 10 FPGA开发板电路图(30)

图36. MAX 10 FPGA开发板电路图(31)