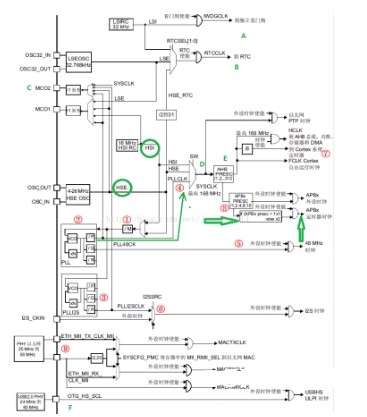

1.首要留意的的是图中画绿色圈圈的两个,HSE和HSI别离表明外部时钟和内部时钟,其间HSE 是是高速外部时钟,可接石英/陶瓷谐振器,或许接外部时钟源,HSE 也能够直接做为体系时钟或许 PLL 输入(从红圈4处能够看出),频率规模为 4MHz~26MHz。STM32默以为25Mhz,像原子的板子便是8Mhz的,所以移植时一定要分外留意。

2.留意红圈2代表的部分,这里是主锁相环倍频输出,用于发生体系需求的高速时钟信号,如图绿色箭头所示(STM32还有一个副锁相环,如红圈3)

主 PLL 时钟的时钟源要先通过一个分频系数为 M 的分频器,然后通过倍频系数为 N 的倍频器出来之后的时分还需求通过一个分频系数为 P(第一个输出 PLLP)或许 Q(第二个输出 PLLQ)的分频器分频之后,终究才生成终究的主 PLL 时钟。例如咱们的外部晶振挑选 8MHz。一起咱们设置相应的分频器 M=8,倍频器倍频系数 N=336,分频器分频系数 P=2,那么主 PLL 生成的第一个输出高速时钟 PLLP 为:PLL=8MHz * N/ (M*P)=8MHz* 336 /(8*2) = 168MHz(来历:正点原子)

3.区别APB1和APB2

如红圈8表明的方位,STM32F4 许多外设的时钟来历,即两个总线桥: APB1 和 APB2,其间 APB1是低速总线(最高 42Mhz),APB2 是高速总线(最高 84Mhz)。别的定时器部分,假如地点总线( APB1/APB2)的分频系数为 1,那么就不倍频,假如不为 1(比方 2/4/8/16),那么就会 2 倍频( Fabpx*2)后,作为定时器时钟输入。

简单点说,举个APB1的比如,体系时钟是168Mhz,APB1分频系数为4(system_stm32f4xx.c装备),则APB1速度为42Mhz,可是挂靠在在该总线上的定时器3,因为分频系数4而不是1,因而定时器输入频率为42Mhz x 2 =84 Mhz,详细详见这篇文章点击翻开链接

4.AHB总线频率

见图