文章转自ADI官网,版权归属原作者一切

摘要

直接数字频率组成(DDS)技能用于发作和调理高质量波形,广泛用于医学、工业、仪器仪表、通讯、国防等很多范畴。本文将扼要介绍该技能,阐明其优势和缺乏,调查一些运用示例,一起介绍一些有助于该技能推广的新产品。

简介

许多职业中一个要害的需求是准确发作、轻松操作并快速更改不同频率、不同类型的波形。不管是宽带收发器要求具有低相位噪声和超卓的无杂散动态功用的捷变频率源,仍是工业丈量和操控体系需求安稳的频率鼓励,快速、轻松、经济地发作可调波形并一起坚持相位接连性的才干都是至关重要的一项规划标准,而这正是直接数字频率组成技能的优势地点。

频率组成的使命

不断增多的频谱拥堵,加上对功耗更低、质量更高的丈量设备的永无止境的需求,这些要素都要求运用新的频率规模,要求更好地运用现有频率规模。成果,人们寻求对频率发作进行更好的操控,大都状况下,均是凭借于频率组成器. 这些器材运用一个给定频率, fC,来发作一个相关的方针频率(和相位), fOUT. 其一般联系能够简略地表明为:

fOUT = εx× fC

其间,份额因子εx, 有时也被称为归一化频率.

该等式一般运用实数逐渐迫临的算法完成。当份额因子为有理数时,两个相对质数(输出频率和基准频率)之比将谐波相关。但在大都状况下,εx 或许归于更广泛的实数集,迫临进程一旦处于可承受的规模之内即会被切断

直接数字频率组成

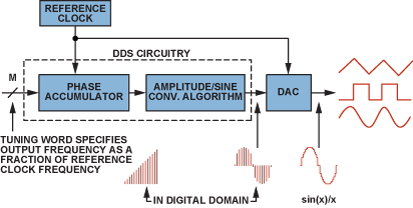

频率组成器的一种有用型完成办法是直接数字频率组成 (DDFS), 一般简称为 直接数字组成 (DDS). 这种技能运用数字数据处理来发作一个频率和相位可调的输出,该输出与一个固定的频率参看或时钟源fC.相关。在DDS架构中,参看或体系时钟频率由一个份额因子分频来发作所需频率,该份额因子由二进制调谐字可编程操控。

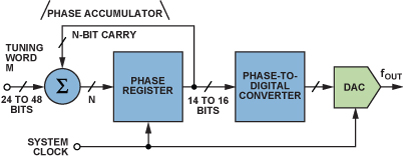

简言之,直接数字频率组成器将一串时钟脉冲转换成一个模仿波形,一般为一个正弦波、三角波或方波。如图1所示,其首要部分为:相位累加器(发作输出波形相位视点的数据), 相数转换器,(将上述相位数据转换为瞬时输出起伏数据),以及数模转换器(DAC)(将该起伏数据转换成采样模仿数据点)

关于正弦波输出,相数转换器一般为一个正弦查找表(图2)。相位累加器以N为单位计数,并依据以下等式发作一个相关于fC的频率:

其间:

M为调谐字的分辨率(24至48位)

N为对应于相位累加器输出字最小增量相位改动的fC的脉冲数.

由于更改N会当即改动输出相位和频率,因此,体系本身具有相位接连,特色,这是许多运用的要害特点之一。无需环路树立时刻,这与模仿体系不同,如锁相环 (PLL).

DAC一般为一个高功用电路,专门针对DDS内核(相位累加器和相幅转换器)而规划。大都状况下,成果构成的器材(一般为单芯片)一般称为纯DDS或C-DDS。

实践的DDS器材一般集成多个寄存器,以完成不同的频率和相位调制计划。如相位寄存器,其存储的相位内容被加在相位累加器的输出相位上。这样,能够对应于一个相位调谐字推迟输出正弦波的相位。关于通讯体系相位调制运用,这十分有用。加法器电路的分辨率决议着相位调谐字的位数,因此,也决议着推迟的分辨率。

在单个器材上集成一个DDS引擎和一个DAC既有长处也有缺点,可是,不管集成与否,都需求一个DAC来发作纯度超高的高品质模仿信号。DAC将数字正弦输出转换为一个模仿正弦波,或许是单端,也或许是差分。一些要害要求是低相位噪声、优异的宽带(WB)和窄带(NB)无杂散动态规模 (SFDR)以及低功耗。假如是外部器材,则DAC有必要足够快以处理信号,因此,内置并行端口的器材十分常见。

DDS与其他处理计划

其他发作频率的办法包含模仿锁相环(PLL),时钟发作器和运用FPGA对DAC的输出进行动态编程。经过调查频谱功用和功耗,能够对这些技能进行简略的比较,表1以定性办法展现了比较成果

表1.DDS与竞赛技能——高档比较

| 功耗 | 频谱纯度 |

补白 |

|

| DDS |

低 |

中 |

易于调谐 |

| 分立式 DAC + FPGA |

中 |

中-高 |

具有调谐才干 |

| 模仿 PLL |

中 |

高 |

难以调谐 |

锁相环是一种反应环路,其组成部分为:一个相位比较器, 一个除法器和一个压操控振荡器 (VCO). 相位比较器将基准频率与输出频率(一般是输出频率的N)分频)进行比较。相位比较器发作的差错电压用于调理VCO,然后输出频率。当环路树立后,输出将在频率和/或相位上与参看频率坚持一种准确的联系。PLL长期以来一向被认为是在特定频带规模内要求高保真度和安稳信号的低相位噪声和高无杂散动态规模 (SFDR) 运用的抱负挑选.

由于PLL无法准确、快速地调谐频率输出和波形,并且呼应较慢,这约束了它们关于快速跳频和部分频移键控和相移键控运用的适用性.

其他计划,包含集成DDS引擎的现场可编程门阵列 (FPGAs) ——合作现成DAC以组成输出正弦波——虽然能够处理PLL的跳频问题,但也存在本身的缺点。首要体系缺点包含较高的作业和接口功耗要求、本钱较高、尺度较大,并且体系开发人员还须考虑额定的软件、硬件和存储器问题。例如,运用现代FPGA中的DDS引擎选项,要发作动态规模为60 dB的10 MHz输出信号,需求多达72 kB的存储器空间。别的,规划师需求承受并了解纤细权衡和DDS内核的架构。

从有用视点来看(见表2),得益于CMOS工艺和现代数字规划技能的快速开展以及DAC拓扑结构的改善,DDS技能现已能在广泛的运用中完成史无前例的低功耗、频谱功用和本钱水平。虽然纯DDS产品不或许在功用和规划灵活性上到达高端DAC技能与FPGA相结合的水平,但DDS在尺度、功耗、本钱和简略性方面的优势使其成为许多运用的首要挑选。

表2.基准剖析小结——频率发作技能(<50 MHz)

| Phase-Locked Loops |

DAC + FPGA |

DDS |

|

| 频谱功用 |

高 |

中-高 |

Medium |

| 体系功耗要求 |

高 |

高 |

底 |

| 数字频率调谐 |

无 |

是 |

是 |

| 数字频率调谐 |

高 |

底 |

底 |

| 处理计划尺度 |

中 |

高 |

底 |

| 处理计划尺度 |

底 |

中 |

高 |

| 本钱 |

中 |

高 |

底 |

| 规划重用 |

中 |

底 |

高 |

| 完成杂乱度 |

中 |

高 |

底 |

一起需求指出,由于DDS器材从根本上来说是用数字办法发作输出波形,因此它能够简化一些处理计划的架构,或许为对波形进行数字化编程创造条件。虽然一般运用正弦波来解说DDS的功用和作业原理,但运用现代DDS IC也能够轻松发作三角波或方波(时钟)输出,由此消除了前一种状况的查找表以及后一种状况的DAC的必要性,由于集成一个简略而准确的比较器就够了.

DDS的功用与约束

Images and Envelopes: Sin(x)/x Roll-Off

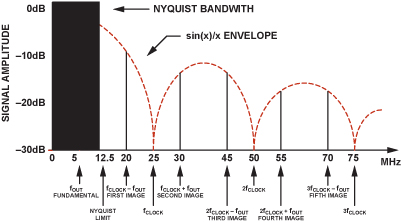

DAC的实践输出不是接连的正弦波,而是带有正弦时刻包络的一系列脉冲。对应的频谱是一系列图画和混叠信号。图画沿sin(x)/x 包络散布(见图3中的|起伏|曲线图)。有必要进行滤波,以按捺方针频带之外的频率,可是不能按捺通带中呈现的高阶混叠(例如,因DAC非线性所造成的)

奈奎斯特准则 要求,每个周期至少需求两个采样点才干重建所需输出波形。镜像呼应发作于采样输出频率中 K fCLOCK × fOUT. 在本例中,其间 fCLOCK = 25 25 MHz且 fOUT = 5 MHz,榜首和第二镜频呈现在(见图3)fCLOCK × fOUT, o即20 MHz和30 MHz。第三和第四镜频呈现在45 MHz和55 MHz。留意,sin(x)/x零值呈现在采样频率的倍数处。当fOUT 大于奈奎斯特带宽 (1/2 fCLOCK), 时,榜首镜频将呈现于奈奎斯特带宽之内,发作混叠(例如,15 MHz的信号将向下混叠至10 MHz)。无法用传统的奈奎斯特抗混叠滤波器从输出中滤掉混叠镜频

在典型的DDS运用中,运用一个低通滤波器来按捺输出频谱中镜频呼应的影响。为了使低通滤波器的截止频率要求坚持于合理水平,并使滤波器规划坚持简略,一种可行的做法是运用一个经济的低通输出滤波器将fOUT 带宽约束在fCLOCK频率的40%左右.

任何给定镜频相关于基波的起伏可用sin(x)/x公式来核算。由于该函数随频率滚降,因此根本输出的起伏将与输出频率成反比而下降;在DDS体系中,下降量为DC-奈奎斯特带宽规模的–3.92 dB。

榜首镜频的起伏较大——基波的3 dB规模内。为了简化DDS运用的滤波要求,有必要拟定频率计划,并剖析镜频和sin(x)/x起伏呼应在fOUT和fCLOCK方针频率下的频谱要求。在线互动规划东西 支撑ADI DDS产品系列,能够快速、轻松地仿真镜像频率巨细,并答运用户挑选镜像坐落方针频带之外的频率。更多有用信息,请参看更多信息和有用的链接部分.

输出频谱中的其他不需求的频率(如DAC的积分和微分线性差错、与DAC相关的突波能量和时钟馈通噪声)不会遵从sin(x)/x滚降呼应。这些不需求的频率将以谐波和杂散能量呈现在输出频谱中的许多地方——但其起伏一般会远远低于镜频呼应。DDS器材的一般本底噪声由基板噪声、热噪声效应、接地耦合和其他信号源耦合等要素累积组合决议。DDS器材的本底噪声、功用杂散和颤动遭到电路板布局、电源质量以及——最重要的是——输入参看时钟质量的深刻影响。

颤动

完美时钟源的边缘将以准确的时刻距离发作,而该距离永久都不会改动。当然,这是不或许的;即便最好的振荡器也是由不抱负的元件构成,具有噪声等缺点。优质的低相位噪声晶体振荡器的颤动为皮秒级,并且是从数百万个时钟边缘累积起来的。导致颤动的要素有热噪声、振荡器电路不安稳以及电源、接地和输出衔接等带来的外部搅扰等,一切这些要素都会搅扰振荡器的时序特性。别的,振荡器受外部磁场或电场以及邻近发射器的射频搅扰的影响。振荡器电路中,一个简略的放大器、反相器或缓冲器也都会给信号带来额定的颤动。

因此,挑选一个颤动低、边缘陡的安稳的参看时钟振荡器是至关重要的。较高频率的基准时钟答应较大的过采样,并且,经过分频能够在必定程度上减轻颤动,由于对信号进行分频将在更长时期发作相同量的颤动,因此能够下降信号上的颤动的百分比。

噪声——包含相位噪声

采样体系的噪声取决于许多要素,首要要素是参看时钟颤动,这种颤动表现为基波信号上的相位噪声。在DDS体系中,切断相位寄存器输出或许带来因代码而异的体系差错。二进制字不会导致切断差错。但关于非二进制字,相位噪声切断差错会在频谱中发作杂散。杂散的频率/起伏取决于代码字。DAC的量化和线性差错也会给体系带来谐波噪声。时域差错(如欠冲/过冲和代码过错)都会加剧输出信号的失真.

运用

DDS运用能够分为两大类:

- 要求捷变频率源以进行数据编码和调制运用的通讯和雷达体系

- 要求通用频率组成功用以及可编程调谐、扫描和鼓励才干的丈量、工业和光学运用

两种状况下,都呈现了一种走向更高频谱纯度(更低的相位噪声和更高的无杂散动态规模)的趋势,一起还存在低功耗和小尺度的要求,以习惯长途或电池供电设备的需求。

调制/数据编码和同步中的DDS

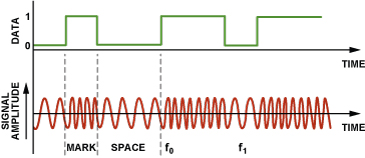

DDS产品首要呈现于雷达和军事运用之中,其部分特性的开展(功用的提高、本钱和尺度等)已使DDS技能在调制和数据编码运用中日渐盛行。本节将评论两种数据编码计划及其在DDS体系中的完成办法

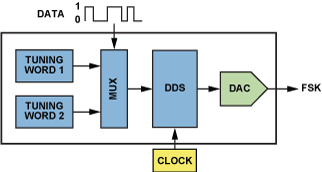

二进制1和0表明为两个不同的频率,分别为f0和f1。这种编码计划能够轻松在DDS器材中完成。代表输出频率的DDS频率调谐字被改动,以从将发射的1和0发作f0和f1。在ADI纯DDS产品系列中,至少有两款器材AD9834和AD9838—另见附录),用户能够简略地将两个当时FSK频率调谐字编程进IC的嵌入式频率寄存器之中。要改换输出频率,则须用专用的引脚FSELECT挑选含有相应调谐字的寄存器(见图5)

相移键控(PSK)是另一种简略的数据编码办法。在PSK中,载波的频率坚持不变,经过改动发射信号的相位来传递信息。能够运用多种计划来完成PSK。最简略的办法一般称为二进制PSK(即BPSK),只选用两个信号相位:0°(逻辑1)和180°(逻辑0)。各位的状况取决于前一位的状况。假如波的相位不变,则信号状况将坚持不变(低或高)。假如波的相位改动180°,即相位回转,则信号状况将改动(低变为高,或高变为低)。PSK编码能够轻松在DDS产品中完成,由于大都器材都有一个独立的输入寄存器(相位寄存器),能够加载相位值。该值被直接添加到载波的相位,而不改动其频率。更改该寄存器的内容将调制载波的相位,成果发作一个PSK输出。关于要求高速调制的运用,内置相位寄存器对的AD9834和AD9838答应其PSELECT引脚上的信号在预加载的相位寄存器之间改换,以依据需求调制载波。

更杂乱的PSK选用四个或八个波相位。这样,每逢相位发作改动时,二进制数据的传输速率将高于BPSK调制。在四相位调制 (正交 PSK),中,或许的相位视点为0°, +90°, −90°, 和 +180°;每次相位改换或许代表两个信号因子AD9830, AD9831, AD9832, 和 AD9835 供给四个相位寄存器,经过接连更新寄存器的不同相位偏移,能够完成杂乱的相位调制计划.

以同步形式运用多个DDS元件完成I/Q功用

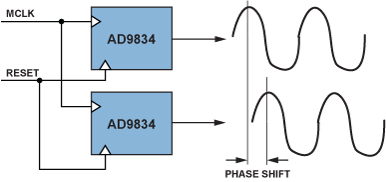

许多运用要求发作两个或两个以上具有已知相位联系的正弦波或方波信号。一个常见的比如是同相和正交调制(I/Q),在这种技能中,在0°和90°相位视点从载波频率取得信号信息。能够用相同的源时钟来运转两个独自的DDS元件,以输出能够直接操控和操作其相位联系的信号。在图6中,用一个基准时钟对AD9838器材编程;相同的RESET引脚用于更新两个器材。这样,能够完成简略的I/Q调制

RESET有必要在上电后以及向DDS传输任何数据之前初始化。成果可将DDS输出置于已知相位,使其成为一起的参看视点,以便同步多个DDS器材。当新数据被一起送至多个DDS器材时,DDS之间能够坚持相关相位联系,或许经过相位偏移寄存器能够猜测性调整多个DDS之间的相对相位偏移。AD983x系列DDS产品具有12位相位分辨率,有用分辨率为0.1°。

有关同步多个DDS器材的更多信息,请参看运用笔记 AN-605同步多个根据DDS的频率组成器AD9852..

网络剖析

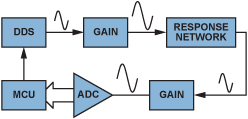

电子世界中的许多运用都需求搜集和解码来自网络的数据,例如模仿丈量和光学通讯体系。正常状况下,体系剖析要求是为了以起伏和相位已知的频率模仿电路或体系,并剖析经过体系的呼应信号的特性.

对呼应信号搜集的信息用于确认要害体系信息。测验网络的规模(见图7)或许十分广泛,包含电缆完整性测验、生物医学传感和流速丈量体系。不管何时,只需根本要求是发作根据频率的信号并将呼应信号的相位和起伏与原始信号进行比较,或许是要经过体系鼓励一系列频率,或许要求具有不同相位联系(如具有I/Q功用的体系中)的测验信号,则可运用直接数字频率组成IC,便利、高雅地经过软件以数字办法操控鼓励频率和相位。

电缆完整性/损耗丈量

缆完整性丈量是一种非介入式电缆剖析办法,广泛用于飞机布线、局域网(LAN)和电话线路等运用之中。确认功用的一种办法是看经过电缆时损耗了多少信号。经过注入频率和起伏已知的信号,用户能够在电缆远端丈量起伏和相位,由此算出电缆衰减。直流电阻和特性阻抗等参数将影响详细电缆的衰减。其成果一般表明为在整个测验频率规模内低于信号源的(0 dB)分贝数。方针频率取决于电缆类型。DDS器材因具有发作宽规模频率的才干,所以能够用作具有必要频率分辨率的鼓励。

流量计

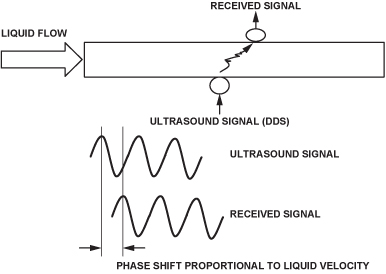

一种相关运用是对管道中的水、其他液体和气体进行流量剖析。一个比如是超声流量丈量,其作业原理是相移准则,如图8所示。根本而言,从有液体活动的通道的一端发射信号,一起在另一端放置一个传感器以丈量相位呼应(取决于流速)。这种技能存在多种改动。测验频率取决于丈量的物质;一般来说,往往在一系列频率规模内发射输出信号。DDS具有无缝设置和更改频率的灵活性

更多信息和有用的链接

互动式规划东西

它是什么?它是DDS的在线互动式规划东西,是在给定参看时钟和方针输出频率和/或相位时用于挑选调谐字的辅助东西。该东西的编程核算成果给出了调谐字和其他装备位,供对器材串行接口编程时运用。在运用外部重构滤波器之后,能够显现选定参看时钟和输出频率的抱负输出谐波。ADI规划东西的链接能够在互动式规划东西主页上找到AD9834规划东西便是比如之一.

评价套件

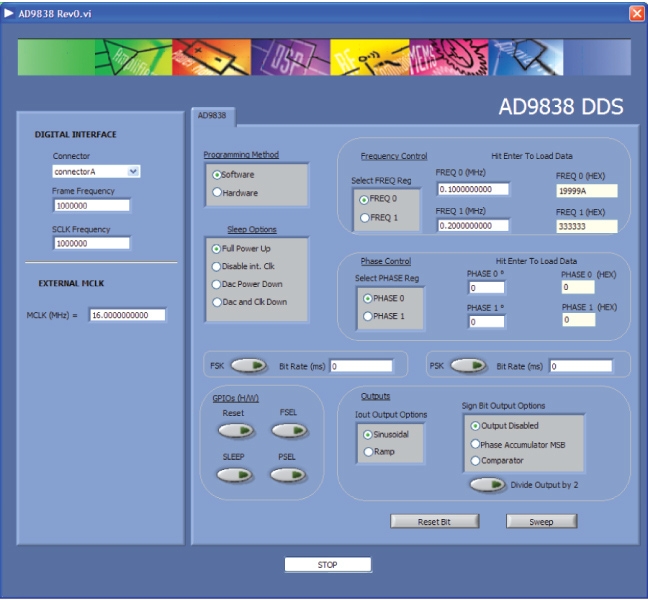

AD983x系列产品装备功用完善的评价套件,并配有原理图和布局攻略。凭借评价套件中供给的软件,用户能够轻松对器材进行编程、装备和测验(见图9)

其他有用的DDS信号能够在DDS网站上找到.

另请参看:

Murphy, Eva and Colm Slattery. “直接数字频率组成全攻略.” 运用工程师问答—33。模仿对话。2004年第38卷第3期: 8–12.

数字信号组成技能教程.. 1999. Analog Devices, Inc.

附录

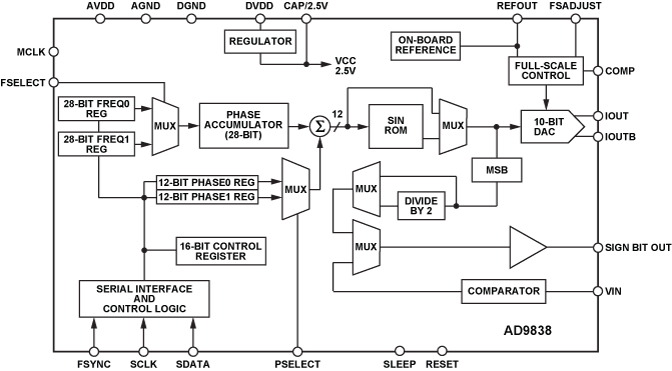

AD9838简介:AD9838 DDS的功用框图如图10所示。该器材选用细线CMOS工艺制成,是一款超低功耗(11 mW)的纯DDS。28位的频率寄存器支撑0.06 Hz频率分辨率和16 MHz时钟,以及0.02 Hz频率分辨率和5 MHz时钟。相位和频率调制经过片内寄存器运用软件或引脚挑选来装备。该器材具有−68 dBc宽带和−97 dBc窄带SFDR,作业温度规模为–40°C至+125°C扩展温度规模。器材选用小型4 mm × 4 mm、20引脚LFCSP(引脚架构芯片级)封装.

| Power Consumption | Spectral Purity |

Comment |

|

| DDS |

底 |

Medium |

Easy to tune |