关于国内而言,正如DSP在20年前呈现的景象相同,现在,FPGA正处于数字信号处理技能的前沿。而DSP都是依据一种精简指令集的计算机体系架构,其固定的硬件结构和数据总线宽度已不合适许多面向用户型(可重装备型)的DSP使用体系;其速度也受制于CPU的指令次序履行的根本作业形式,这已成为DSP处理器一个难以打破的瓶颈。

现代的大容量、高速度FPGA器材一般都内嵌有可装备的高速RAM、PLL、LVDS、LVTTL以及硬件乘法累加器(MAC)等DSP模块,并且都供给了支撑以低体系开支、低本钱完结高速乘-累加(MAC)超前进位链的DSP算法。 在许多宽带信号处理范畴(如无线通讯、多媒体体系、卫星通讯、雷达体系等),FPGA技能具有更宽广的使用远景,已替代DSP完结许多前端的数字信号处理算法。用FPGA来完结数字信号处理能够很好地处理并行性和速度问题,并且其灵敏的可装备特性,使得FPGA构成的数字信号处理体系易于修正、测验及体系升级,能下降规划本钱,缩短开发周期。

本文使用FPGA技能针对一个长途监控体系的多路数据收集体系,完结了64bit位宽的海量数据实时收集、存储以及时钟匹配。

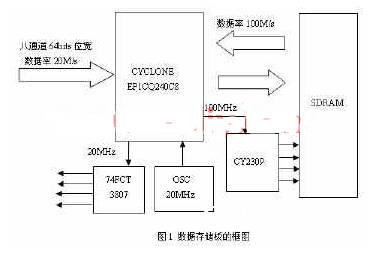

1 数据存储板的结构

图1为数据收集体系中数据存储板的根本框图,数据收集时钟为20MHz,远低于SDRAM存储的作业时钟100MHz,需求进行缓冲处理。通用CPU的SDRAM操控器只支撑32bit位宽数据,并且容量也很难做到480M,笔者运用Altera公司的Cyclone系列高性价比EP1CQ240C8定制SDRAM操控器。

EP1CQ240C8是该数据存储板的中心器材,其首要功用有:完结数据的缓冲;对SDRAM的读写时序操控;完结EPP(增强型并口)协议与计算机通讯;供给SDRAM的100MHz作业时钟;发生SDRAM所需的守时改写、充电、装备等操控指令;供给SDRAM的地址空间等。SDRAM挑选HYNIX公司32M×8bit×16组的HYM72V64636BT8。

20MHz晶振为EP1CO240C8供给输入时钟,一起被EP1CQ240C8内部的PLL倍频到100MHz和跟从的20MHz,前者被CY2309功分到SDRAM,为SDRAM的存储器组供给作业时钟;后者被时钟驱动芯片74FCT3807分为多路,为A/D供给采样时钟。

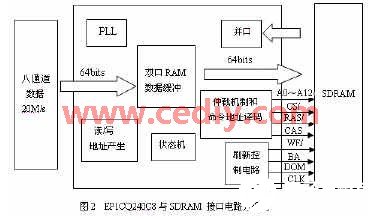

2 EP1CQ240C8与SDRAM的接口规划

SDRAM的作业形式装备

HYM72V64636BT8具有同步接口,其所有输入和输出都与体系时钟CLK上升沿同步,由输入信号RAS、CAS、WE组合发生SDRAM操控指令,完结相应的形式寄存器设置、改写、激活、读写、预充电等操作。

SDRAM在作业之前有必要设置形式寄存器,其读写作业形式分为一般形式和页形式。一般形式的数据长度能够为1,2,4,8;页形式和一般形式不同,一旦确认队伍地址,则数据依照作业时钟(本体系作业时钟为100MHz)读出或写完一页(1024列)。

为了编程便利,笔者选取读写不同的作业形式:向SDRAM写入数据时选用页形式,写满后读出数据时选用是突发长度为1的一般形式。读写操作完结后用PCH指令或BT指令预充电间断读或写操作。在没有读写操作的时分,每64ms有必要用ARF指令改写存储单元,避免数据丢掉。

SDRAM的操控接口规划

依据本体系SDRAM的作业要求, EP1CQ240C8与SDRAM的接口电路方框图如图2示,笔者对FPGA的内部硬件资源进行了具体装备。

(1)PLL(锁相环)完结时钟办理。

(2)地址发生模块由计数器构成,包含写地址模块和读地址模块。写地址模块发生的地址一起送到双口RAM和状态机,状态机宣布初始化、改写、读写、充电等指令,交给裁定机制,在不抵触的情况下完结指令的译码和地址的队伍复用,这时数据被存入到由地址的行和列所确认的SDRAM地址中去。数据存满SDRAM后再切换到读地址模块,经过读地址模块发生读地址将数据读出到并口,然后导入计算机进行相关的处理。

(3)裁定机制完结对读写指令和改写指令的裁定,根绝一起操作;指令译码首要用于操控SDRAM的各种时序,完结SDRAM的读写和改写。

(4) 改写操控电路首要完结对SDRAM数据改写进行计时,保证每64ms改写8192行数据;改写操控电路首要由781计数器构成。因为SDRAM作业时钟是100MHz,SDRAM要求在64ms之内改写8192行数据,因而该计数器应小于:64ms/8192/0.01us=781.25 。当计数器计满781次后,改写操控电路向裁定电路宣布改写恳求,裁定机制依据恳求向SDRAM宣布改写指令。

(5)状态机是SDRAM操控器的中心。在程序计划上,笔者规划了两个模块:一个模块发生状态机指令和操控指令;另一个模块完结指令的译码,包含读写、改写、充电等操作,将指令翻译成SDRAM的指令码字,完结特定的操作。

在本体系中,因为多通道数据收集后进入FPGA的时钟是20MHz,而FPGA的状态机以及SDRAM的时钟是100MHz,因而,数据需求做缓冲处理。笔者使用FPGA内部的硬件资源结构双口RAM处理时钟匹配问题,一起又考虑到SDRAM作业在页形式,因而将双口RAM的容量结构成SDRAM一页的数据容量1024×64bits,这样数据缓冲一页就存入一页。双口RAM作为FPGA装备中的要害模块,下面将具体介绍双口RAM的规划。

3 双口RAM的结构

因为本体系中数据读出时钟是写入时钟的五倍,所以有必要留意时钟追逐的问题,即读出一定要滞后写入,不然读出的数据就不是存入双口RAM的数据。

笔者的编程思路是:当数据以20MHz时钟写入到双口RAM容量的7/8时,便以100MHz时钟开端读出,读完一页后有必要就等候下次写满7/8。读出的一页数据刚好存满SDRAM的一页,顺次类推,这样就完结了数据的缓冲。当然,读写地址的发生是FPGA内部用计数器完结的,因而,就得到如图3示的算法流程图。

图3中clk1为20MHz时钟,clk2为100MHz时钟;count1[9:0]输入到双口RAM的wraddress[9:0],count2[9:0]输入到rdaddress[9:0]。并和“1110000000”比较,判别是否写满了双口RAM的容量的7/8,假如写满了就触发100MHz的读出时钟,数据开端从双口RAM读出。依据上述思路,使用Altera公司的开发渠道QUARTUS II完结编译、仿真得到双口RAM的功用仿真波形如图4示,由仿真成果可知该计划很好地处理了时钟追逐问题,完结了数据缓冲。

4 数据存储板的功能测验

笔者使用在FPGA内部资源编写了一个测验模块,用它发生有规则的数据信号(模仿采样的数据),并存入SDRAM,当存满后经过EPP将数据存储到计算机,使用相关软件读出保存到计算机的数据如图5示,仿真成果表明存入的数据与测验模块发生的数据共同,存储板能正常作业。

本文作者的立异点:

在本监控体系中,充分使用了FPGA内部的硬件资源—嵌入式逻辑块,使用软件编程处理了64位宽的海量数据缓冲、分页存储及体系时钟匹配问题,发挥了FPGA技能在信号处理范畴的重要作用。

责任编辑:gt