莱迪思半导体白皮书

2019年11月

现在,嵌入式视觉体系规划师需求投合许多商场趋势。例如,现在的规划运用的传感器越来越多,便于搜集更多数据或完成新的功用。比如在轿车商场,几十年前,轿车厂商在车辆上装置一个备份摄像头就算是立异之举了,而现在他们现已开端将摄像头用于路途违背监控、速度标志牌辨认和其他许多智能驾驭运用。

一起,嵌入式视觉体系规划师正逐渐选用契合移动工业处理器接口(MIPI)联盟规范的组件。 MIPI起初是为移动商场开发的,它界说了移动设备的规划人员在在构建高功用、高本钱效益、牢靠的移动处理方案时所需的硬件和软件接口规范。在曩昔几年中MIPI现已成为开发嵌入式体系的干流规范。包含工业和轿车等范畴的各类运用的规划人员都现已意识到这一点,并且开端寻觅办法来运用移动组件高功用和规模经济的优势。

缩短上市时刻带来的压力也推动了对易于运用的嵌入式视觉处理方案的需求。只供给芯片的做法现已远远不够了。这些压力让规划人员迫切需求能够供给一切硬件、软件、IP和参阅规划的嵌入式视觉规划环境,然后快速规划和开发终端产品。与此一起,现在的用户期望他们的嵌入式显现屏能够像消费电子产品那样反响快捷。发动很慢的嵌入式显现屏会带来伪像,损坏用户体会。

新的应战

这些快速开展的趋势在发明机会的一起,也为嵌入式视觉规划师带来了严峻的应战。首要,许多嵌入式体系中运用的摄像头和显现屏与当今的运用处理器(AP)的接口类型或数量不匹配。AP上用于传感器的I/O很有限,却又要支撑各类显现屏和传感器,更为扎手的是,各种运用的显现巨细和分辨率也不尽相同。此外,工业显现屏运用寿命较长,许多尚在运用的显现屏开始是经过传统接口衔接的。那么,当嵌入式运用的规划人员在规划中不得不运用传统或专用的显现屏和传感器时,怎么运用好MIPI组件商场的优势呢?

为了支撑运用更多传感器和更有效地办理I/O资源,规划人员需求可编程的处理方案来补偿I/O缺乏的缺点。抱负情况下,这样的处理方案需求聚合传感器输入,并且让规划师对数据进行预处理,削减处理器的负载。抱负的处理方案还需求是可编程的,能够轻松地习惯定制化的显现屏规划。曾经,规划师只能经过为每种显现类型开发专门的ASIC来支撑不同的显现尺度和分辨率。而可编程的处理方案能够运用单个器材完成不同的显现要求。

2016年,跟着CrossLinkTM系列FPGA的推出,莱迪思半导体成为这一范畴的抢先供货商。这是一款可编程的视频桥接器件,支撑衔接移动图画传感器和显现屏的各类协议和接口。为了满意嵌入式视频商场不断增加的需求,莱迪思又推出了CrossLink的增强版别——CrossLinkPlusTM。CrossLinkPlus新增了2 Mbit的嵌入式闪存作为装备存储器,满意用户对显现屏无缝发动的需求。有了片上闪存,CrossLinkPlus能够在10 ms内瞬时发动,而人脑一般无法在15 ms内感知图画,因而不会产生伪像搅扰用户体会。片上闪存可支撑现场从头编程。

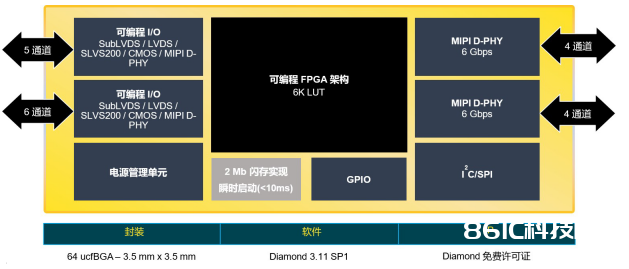

图1:莱迪思半导体的CrossLinkPlus FPGA

CrossLinkPlus具有同尺度FPGA中速度最快的MIPI D-PHY,一起功耗十分低。此款FPGA封装尺度仅为3.5 mm x 3.5 mm,共支撑12 Gbps D-PHY。除了高速MIPI D-PHY外,CrossLinkPlus还具有6K LUT可编程FPGA架构和灵敏的高速I/O,支撑MIPI CSI-2、MIPI DSI、LVDS、SLVS200、CMOS和Sub-LVDS等接口的视频桥接。由于CrossLinkPlus能够衔接这类显现屏和传感器,为规划团队供给了极大的规划灵敏性。

全新器材能够协助开发团队提高规划功率,然后应对产品快速上市的压力。例如,针对接收器、转换器和发送器等功用供给的即时可用的预验证IP库能让规划人员专心于开发其规划的高价值特性,让他们的产品在竞赛中锋芒毕露。预验证的视频IP模块和参阅规划不只能缩短规划周期,还能免费当即取得。此外,这些IP模块在CrossLink和CrossLinkplus产品系列均可复用。

莱迪思还供给易于运用的硬件和软件东西来模仿功用体现、验证体系级功用、加速产品开发。器材上的嵌入式闪存让规划人员能够在现场更新位流,满意不断改变的商场需求。全新CrossLinkPlus还能协助工程师处理严厉的尺度和功耗约束问题,一起避免了运用外部闪存产生更多功耗。

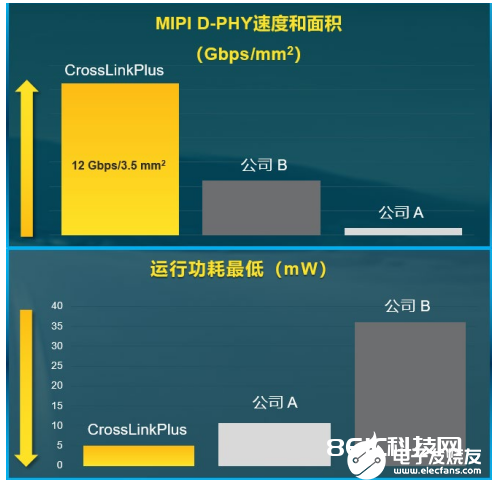

从竞赛力视点而言,该器材的单位尺度硬核MIPI D-PHY速率为业界最快。莱迪思CrossLinkPlus与相似的竞品比较不只尺度更小,D-PHY功用更强,功耗也更低。

图2:莱迪思CrossLinkPlus FPGA不只供给高功用的MIPI D-PHY,并且功耗极低

莱迪思为加速产品开发供给了许多支撑。例如,莱迪思会定时推出根据CrossLink和CrossLinkPlus的新参阅规划。这些参阅规划都是为在新的或现有产品规划上完成盛行的视频桥接特性而定制的。

新的运用

CrossLinkPlus的常见用例标明它能够赋予规划人员高度的规划灵敏性。下列图3描绘了怎么运用该器材桥接不同接口的传感器和处理器。这此事例中,规划人员面对这样一个问题:一方面它们期望运用MIPI处理器的本钱、功用和尺度的优势;另一方面,他们期望保存选用职业规范的现有摄像头。在图3的机器视觉运用中,规划人员选用CrossLinkPlus来桥接Sub-LVDS接口的摄像头和D-PHY接口的MIPI处理器。

图3:在此运用示例中,莱迪思CrossLinkPlus FPGA在Sub-LVDS摄像头与机器视觉处理器的MIPI I/O之间起到桥接的效果。

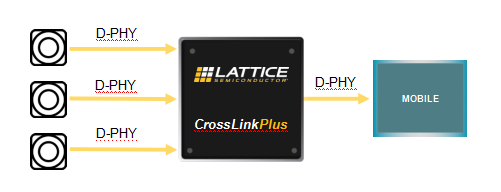

莱迪思CrossLinkPlus的第二个潜在运用是聚合多个传感器的输入,并将其发送至运用处理器。例如,在图4中,三个图画传感器经过三个D-PHY端口与CrossLinkPlus器材衔接。CrossLinkPlus将传感器数据聚合,经过单个D-PHY输出至处理器。规划人员能够经过这种聚合功用优化运用处理器有限的I/O资源。

图4:莱迪思CrossLinkPlus能够在一个端口上聚合多个传感器信号,节省处理器的I/O

规划人员还能够运用CrossLinkPlus来完成MIPI信号别离或仿制。在图5中,规划人员将来自传感器的信号馈送到CrossLinkPlus器材中,然后将输出拆分或将其仿制到两个独自的输出中。莱迪思以为这种办法将越来越多地运用于智能轿车的ADAS或重视数据冗余备份的运用中。在此事例中,来自摄像头的信号进入莱迪思CrossLinkPlus器材,并被仿制到两个输出流中。一个被发送到实时处理数据的运用处理器。第二个被存档到本地或云端进行数据记载和备份,相似飞机的黑匣子。若产生毛病或交通事端,查询人员能够检查数据备份,确认事端原因。

图5:在该ADAS视觉体系中,CrossLinkPlus FPGA仿制摄像头信号输出,发送至运用处理器和数据备份处

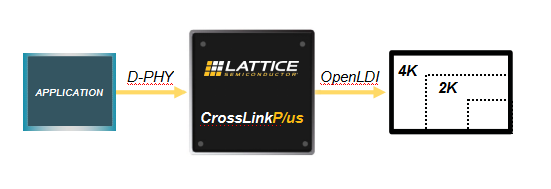

下图6展现了规划人员怎么运用CrossLinkPlus将传统显现器衔接到新的高功用AP。许多工业操控运用在衔接OpenLDI接口的传统显现屏和AP时,需求选用桥接器材,由于OpenLDI显现屏一般比MIPI显现屏大许多。新的MIPI运用处理器经过D-PHY将数据传送到CrossLinkPlus。然后,该器材运用OpenLDI桥接,将数据发 送到传统显现屏。相同,CrossLinkPlus可用于桥接非MIPI接口的图画传感器和MIPI AP。

图6:在该运用示例中,莱迪思CrossLinkPlus完成了传统显现器和现代运用处理器之间的衔接

定论

现在,有了莱迪思CrossLinkPlus,那些期望加速嵌入式视觉开发的规划师们就无需苦苦寻觅了。经过将FPGA的可重编程性引进嵌入式视觉体系,CrossLinkPlus让规划人员能够运用MIPI组件供给的本钱和功用优势。其硬核D-PHY接口可供给职业抢先的功用,嵌入式闪存可完成瞬时显现。该器材的运转功耗极低,尺度小,有助于简化散热办理,对各类常用接口和传统接口的支撑最大极限地提高了规划灵敏性。最终, CrossLinkPlus全面的、预先验证且免费的IP库进一步加速了开发速度,让规划人员将更多时刻用于规划的 中心部分——提高竞赛优势。